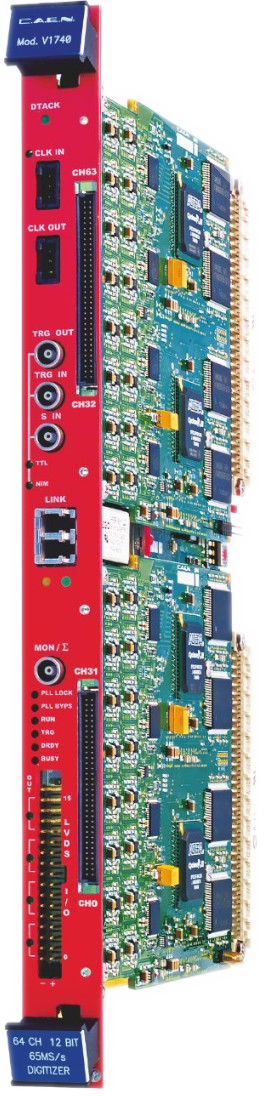

64 Channel 12 bit 62.5 MS/s Digitizer supporting DPP-QDC firmware

V1740D

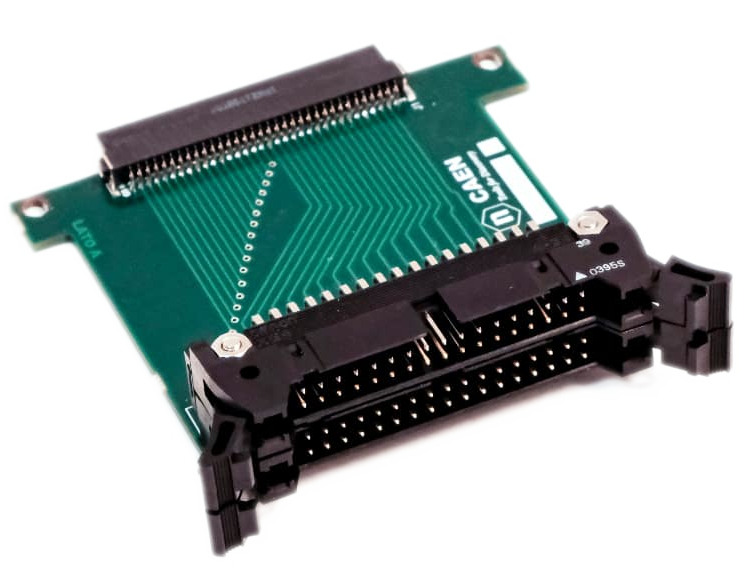

The Mod. V1740D is a 1-unit wide VME 6U module housing a 64 Channel 12 bit 62.5 MS/s (65 MS/s using external clock) Flash ADC Waveform Digitizer and featuring 2 Vpp single ended input dynamics on two ERNI SMC connectors.

The DC offset adjustment (range ±1 V) by programmable 16bit DACs (one for each 8-channel group) allows a right sampling of a bipolar (Vin = ±1 V) up to a full positive (Vin = 0 ÷ +2 V) or negative (vin = 0 ÷ -2 V) analog input swing without losing dynamic resolution.

The module features front panel Clock Input and Output as well as a PLL for clock synthesis from internal/external references. The data stream is continuously written in a circular memory buffer. When the trigger occurs, the FPGA writes further N samples for the post trigger and freezes the buffer that can be read either by VMEbus or Optical Link. The acquisition can continue without dead time in a new buffer.

Each channel has a SRAM Multi-Event Buffer divisible into 1 ÷ 1024 buffers of programmable size. The readout (by VMEbus or Optical Link) of a frozen buffer is independent from the write operations in the active buffer (ADC data storage). Each channel has a SRAM Multi-Event Buffer of 192 kS divisible into 1.

V1740D supports multi-board synchronization allowing all ADCs to be synchronized to a common clock source and ensuring Trigger time stamps alignment. Once synchronized, all data will be aligned and coherent across multiple V1740D boards.

The trigger signal can be provided externally via the front panel Trigger Input as well as via the software, but it can also be generated internally thanks to threshold self-trigger capability. The trigger from one board can be propagated to the other boards through the front panel Trigger Output.

An Analog Output is available with four operating modes supported:

-

Waveform Generator: 1 Vpp ramp generator

-

Majority: output signal is proportional to the number of channels groups under/over threshold (1 step = 125 mV)

-

Buffer Occupancy: output signal is proportional to the Multi Event Buffer Occupancy: 1 buffer ~ 1 mV

-

Voltage level: output signal is a programmable voltage level

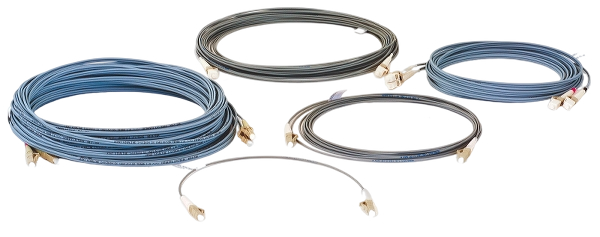

V1740D houses VME (VME64X compliant) and Optical Link interfaces. The VME interface allows data transfers of 60 MB/s (MBLT64), 100 MB/s (2eVME), 160 MB/s (2eSST). The Optical Link supports transfer rate of 80 MB/s and offers Daisy chain capability. Therefore, it is possible to connect up to 8/32 ADC modules to a single Optical Link Controller (Mod. A5818).

Software available (Windows and Linux):

CAEN provides drivers for all the different types of physical communication channels, a set of C and LabView libraries (CAENComm and CAENDigitizer), demo applications and utilities:

-

CAENUpgrader: tool that allows the user to update the firmware of the digitizers, change the PLL settings, load, when requested, the license for the pay firmware and other utilities.

Standard Firmware compliant:

-

CAEN WaveDump: software console application that can be used to configure and readout event data from any model of the CAEN digitizer family and save the data into a memory buffer allocated for this purpose.

Digital Pulse Processing firmware for Physics Applications – this special firmware allows to perform on-line processing on detector signal directly digitizer:

-

DPP-QDC Pulse Processing for Charge to Digital Converter DT5740D digitizer running DPP-QDC firmware becomes a digital replacement of Single Gate QDC plus Discriminator and Gate Generator.

-

CoMPASS Multiparametric Acquisition Software.

Supported third-party software:

-

FSUDAQ – Florida State University DAQ

×Note: V1740D can be operated with VME8004B / VME8004X / VME8008B / VME8008X / VME8010 / VME8011 / VME8100 / VME8200.

Never use this digitizer with crates VME8001, VME8002, VME8004 and VME8004A. Overheat may damage the module.

Features

-

12 bit 62.5 MS/s ADC

-

64 channels

-

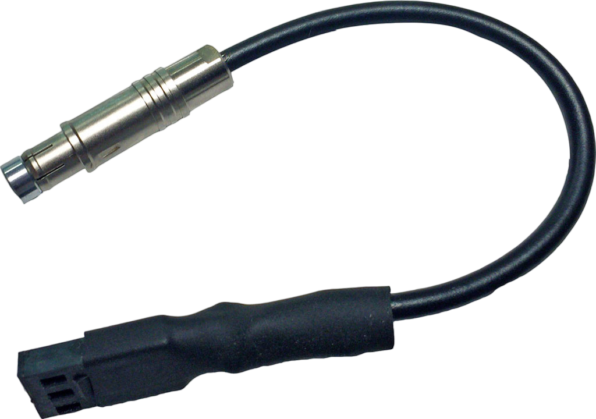

Two ERNI SMC Dual Row 68pin connectors (32 + 32 channels)

-

2 Vpp single ended input range

-

16-bit programmable DC offset adjustment: ±1 V

-

Trigger Time stamps

-

Memory buffer: 192 kS/ch, up to 1024 events

-

FPGA for real-time data processing:

-

Programmable event size and pre-post trigger adjustment

-

Analog Sum/Majority and digital over/under threshold flags for Global Trigger logic

-

Front panel clock In/Out available for multiboard synchronisation (direct feed through or PLL based synthesis)

-

16 programmable LVDS I/Os

-

Optical Link interface (CAEN proprietary protocol)

-

VME64X compliant interface

-

A2818 (PCI) / A3818 (PCIe) Controller available for handling up to 8/32 modules Daisy chained via Optical Link

-

Firmware upgradeable via VME/Optical Link

-

Libraries, Demos (C and LabView) and Software tools for Windows and Linux

V1740D: Data Sheets

V1740D: Manuals

V1740D: Download