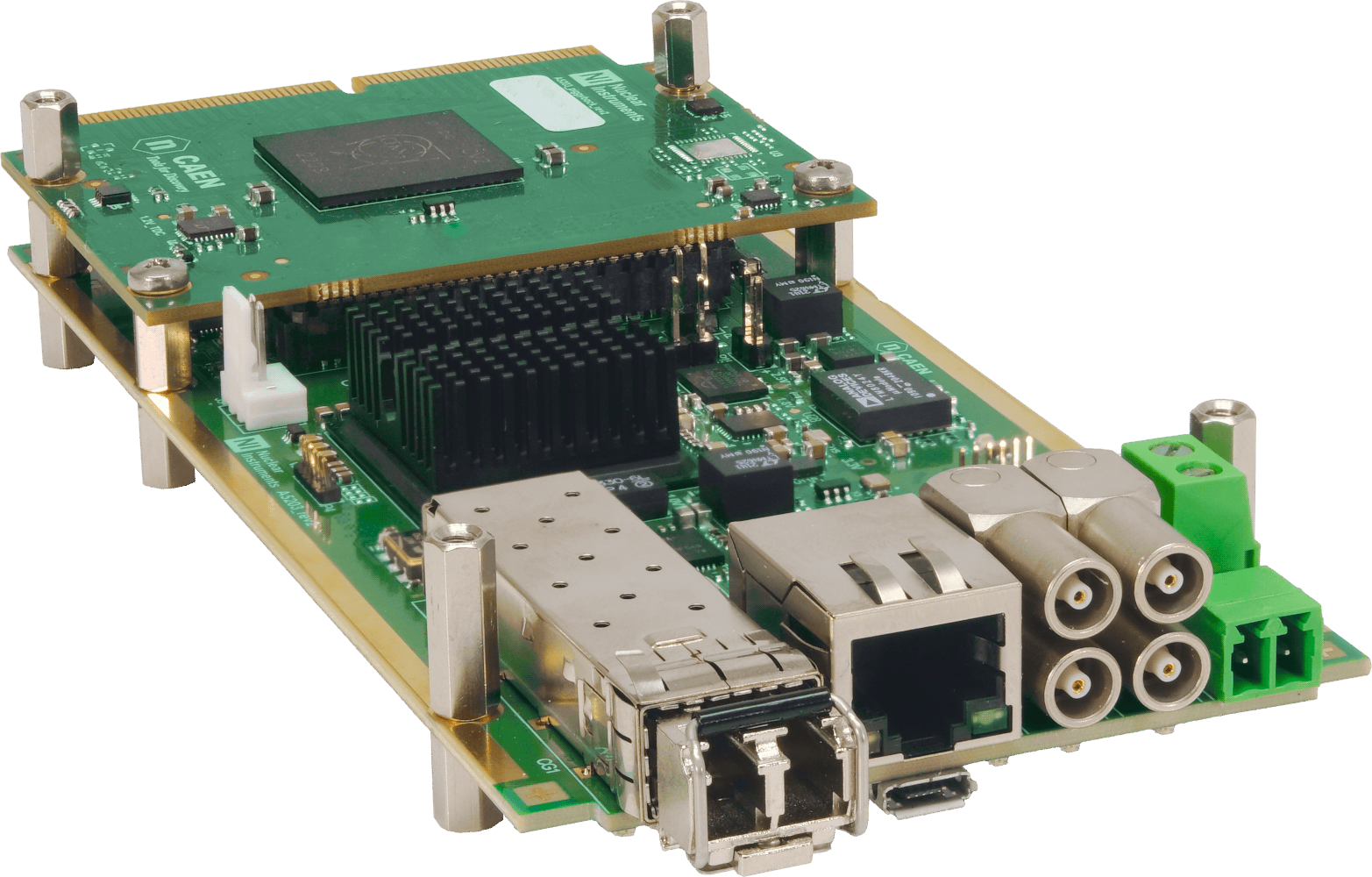

64/128 Channel picoTDC unit for FERS-5200

A5203

FERS-5200 is a front‐end readout system designed for the readout of large detector arrays, such as SiPMs, multi‐anode PMTs, Silicon Strip detectors, Wire Chambers, GEMs, Gas Tubes and others. FERS‐5200 is a distributed and scalable system, where each unit is a small card that houses 64 or 128 channels. It features a detector specific Front-End interfaced to a common infrastructure that guarantees readout interfaces, slow control and synchronization. Typically, the front-end is based on ASIC chips that allow for high density, cost effective integration of multi-channel readout electronics into small size and low power modules. FERS is a flexible platform: combining the same back-end (i.e. readout architecture and interface) with different types of front-end to fit a wide range of detectors.The A5203 (and DT5203, which is the boxed version for desktop use) is a member of the FERS-5200 family. It uses the picoTDC chip (produced by CERN) for high-resolution multi-hit time measurements. The A5203B houses an additional mezzanine card with a second picoTDC chip, thus implementing a 128 channel TDC module.Each readout channel accepts LVDS signals and measures the time stamp of both rising and falling edges with an LSB of 3.125 ps. In this way, the unit is able to reconstruct Time of Arrival of signals as an absolute timestamp or as a deltaT with respect to a common Tref pulse. The picoTDC can also acquire Time over Threshold information and combine it with the edge time stamp. The ToT allows for amplitude estimation, energy spectrum reconstruction, and timing walk correction, and it also enables the possibility to achieve optimal timing resolution with no need of Constant Fraction Discriminators.For small setups a single A5203 unit can be used stand alone, without any additional hardware, by simply connecting the unit to a PC via USB 2.0 or Ethernet 10/100T. For large readout systems, a flexible and scalable network of units can be created by means of the high speed optical link called TDlink. The TDlink system supports up to 128 FERS units to be connected to and managed by one DT5215 FERS Data Concentrator Module. The TDlink supports optical daisy chaining and provides slow control, high speed data readout, synchronization between the units (clock and sync distribution), as well as command broadcasting for triggers, time resets, etcThe A5203 is fully supported by the CAEN Janus open source software for Windows® and Linux. Janus can run in console mode (C program, without graphics) or connected to a GUI written in Python. The GUI has configuration panels and run control which make it easy to manage acquisition. Both console and GUI modes acquire data from multiple boards, manage the event building and timing histograms (deltaT and/or ToT), display data statistics (hit rate, throughput, etc…), plot histograms, and save output, including spectra and list files with the acquired timing data.The A5203 supports the following acquisition modes:

-

Common Start: channel 0 is the common start that opens the acquisition gate and represents the time reference. All other channels provide deltaT time measurements: DTN = TN – T0. The gate width is programmable by software. Any hit falling outside the gate will be discarded. In the case of multiple hits in the same channel only the first will be used for the deltaT acquisition (although all multiple hits will be acquired by the picoTDC). The common time reference on channel 0 can be driven from the relevant LVDS input or from the T0, T1 IN/OUT connectors (NIM or TTL), enabling the possibility to distribute the Tref signal among multiple boards through a daisy-chain. In Common Start mode the event data are composed by the Trigger ID, the 56 bit coarse time stamp (LSB = 12.8 ns) for the absolute time, the Tref (i.e. Ch 0) fine time stamp (LSB = 3.125 ps) and the list of the deltaT (LSB = 3.125 ps) for the channels from 1 to 63 (only those channels that have been hit). If enabled, ToT is also acquired for all channels, including Ch0 (Tref)

-

Common Stop: similar to common start, but the common time reference on channel 0 is used as a stop that closes the acquisition gate: DTN = T0 – TN. In case of multiple hits only the last one will be used.

-

Trigger Matching: in this mode there is a trigger signal (typically coming from the T0/T1 inputs) which defines an acquisition window with programmable width and offset. All hits falling within that window will be recorded. Multi-hit acquisition is supported. All time measurements are referred to the start of the acquisition window with coarse timing resolution (LSB = 25.6 ns). However, the relative timing between the channels keeps the maximum resolution of 3.125 ps. In Trigger Matching mode the event data are composed by the Trigger ID, the 56 bit coarse time stamp (LSB = 12.8 ns) for the absolute time of the trigger, and the list of the hit time stamps of all channels (LSB = 3.125 ps). It is possible to save leading edge only, leading edge and trailing edge, or leading edge + ToT.

-

Streaming: this acquisition mode implements a continuous hit recording, without any gate or trigger windowing. All hits received by the inputs are converted into a 64 bit time stamp (LSB = 3.125 ps) and saved in the form of a sorted list. It is possible to save leading edge only, leading edge plus trailing edge, or leading edge plus ToT. In order to make the data management easier the list is split into time frames of fixed width, thus creating event data packets identified by an ID and a coarse time stamp.

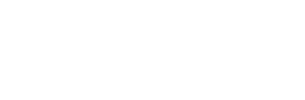

FULL RANGE OF ACCESSORIES FOR SENSORS REMOTIZATION! The A5203 has an input edge card connector, type HSEC8-170, which mates to a Samtec HSEC8-170-01-S-DV. The connector has 140 contacts (0.8 mm pitch) and brings 64 LVDS pairs, a few control signals and a 3.3V power line. The edge connector makes it possible to build a custom backplane or a flange for the interconnection to the detectors. CAEN also offers a wide range of adapters and cables, in order to provide different connectors and also signal conditioning, as well as the ability to remotely operate the detectors.A wide range of adapters and cables has been also specifically designed for FERS-5200 boards, in order to provide versatility of choice and the ability to remotely operate the detectors:

-

A5255, four 17×2, 2.54 mm pin header adapter (64 channels in total) for flat cables. Aux LEMO connector for NIM/TTL signals, driving channel 0, that is the common time reference (selection between NIM/TTL or LVDS of ch0 via solder jumpers).

-

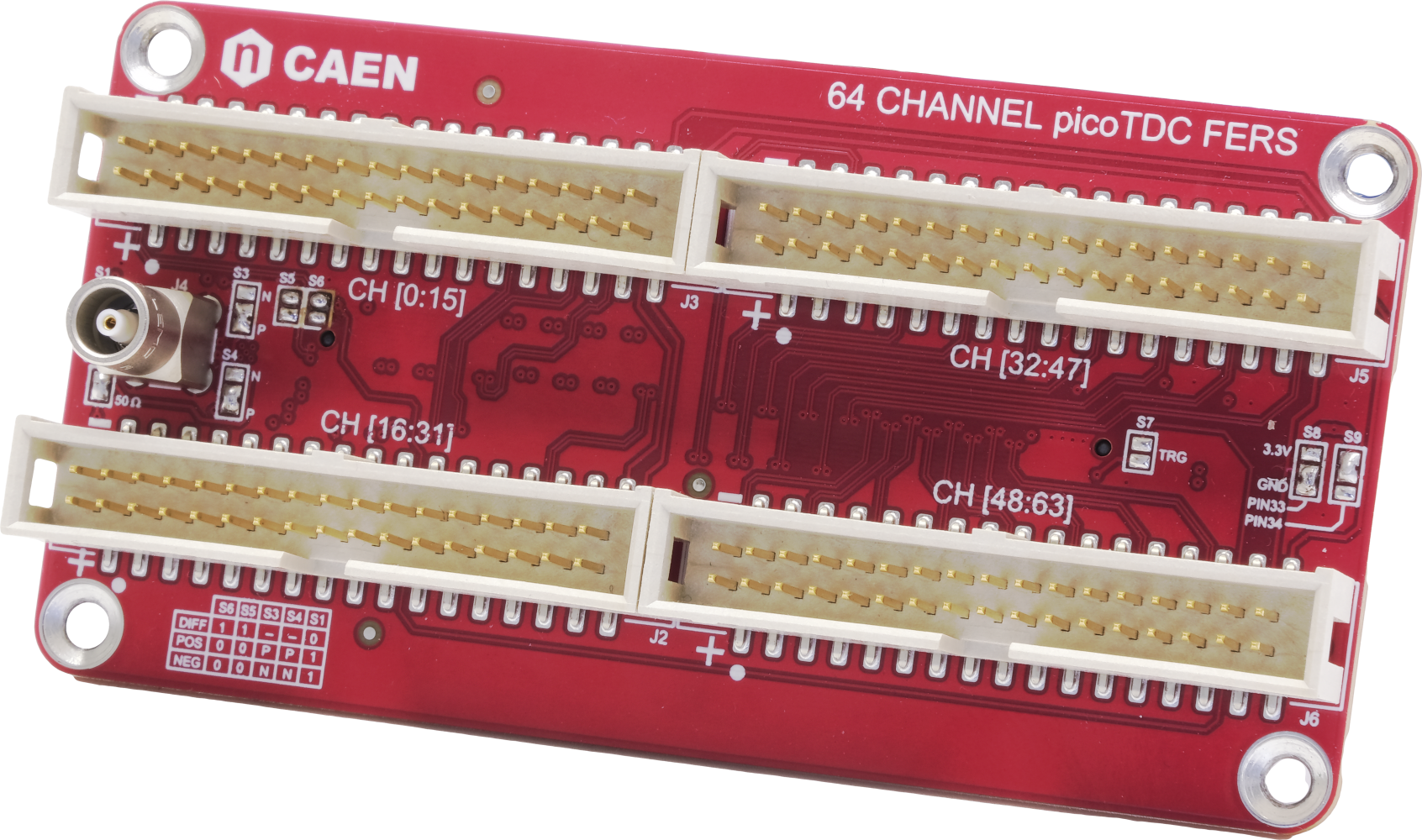

A5256, 16+1 channel dual threshold, leading edge discriminator for analog single-ended signals on LEMO coaxial connectors. It includes ultra-fast comparators with programmable thresholds (DAC) and accepts both positive and negative analog pulses as well as NIM or TTL logic signals. Dedicated connector for Channel 0 (Tref). The dual threshold allows for a better ToT to amplitude conversion and walk correction, as well as pulse shape discrimination.

-

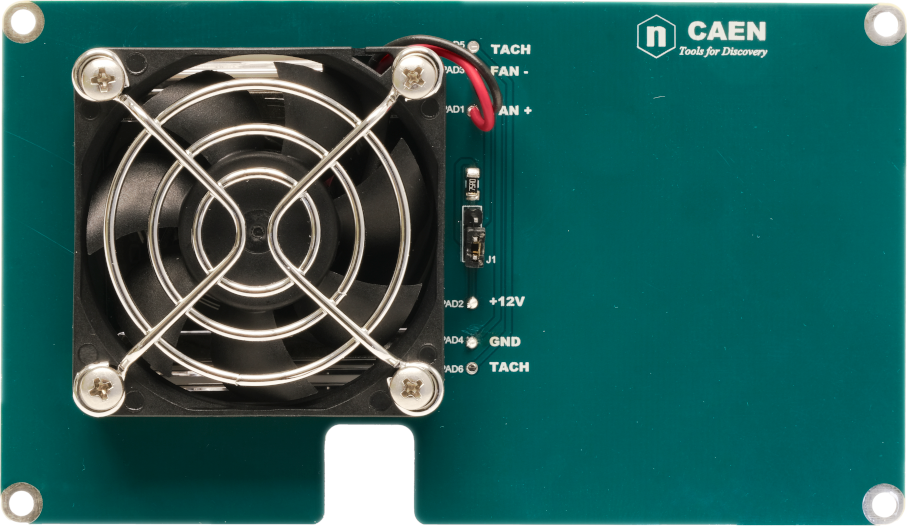

A5260, the remotization cable for FERS-5200 board.

A detailed documentation of all FERS-5200 header adapters and cables is available on CAEN website.

Features

-

64/128-ch TDC unit for high-resolution timing applications housing the CERN picoTDC prova

-

Part of FERS-5200, the CAEN platform for the readout of large arrays of detectors (SiPM, MA-PMTs, Gas Tubes, Si detectors, …)

-

Timing resolution: LSB = 3.125 ps, RMS typ. ~ 7ps

-

LVDS-compliant input, possibility to use single-ended analog/NIM/TTL through dedicated adapters

-

Acquisition of rising/falling edge timestamps enabling ToA and ToT measurements

-

Scalability and easy-synch: up to 128 cards (8192 channels) can be managed and synchronized by a single DT5215 Concentrator Board, thanks to the optical TDLink

-

Janus software available for board and DAQ control

-

Flexibility: a full range of adapters and cables for different kind of applications and sensors remotization

-

Boxed FERS unit (DT5203) for desktop use available

A5203: Data Sheets

A5203: Manuals

A5203: Download