64 Channel 16 bit 125 MS/s Digitizer

DT2740

The CAEN DT2740 Digitizer is a 64-channel digital signal processor for radiation detectors in a Desktop form factor. It offers not only waveform digitization and recording but also Multi-Channel Analysis for nuclear spectroscopy using Silicon strip, segmented HPGe, Scintillation detector with PMTs, Wire Chambers, and others.

The DT2740 can perform pulse height measurements (PHA), and other algorithms that will be gradually developed, such as constant fraction timing (CFD), charge integration (QDC) and pulse shape discrimination (PSD). Algorithm settings can be set independently channel by channel.

Each channel of the module digitizes the analog input, that can be the signal coming from a physics detector, with a 16 bit, 125 MS/s ADC. The sampled data are used to initiate the digital pulse processing sequence, managed in the FPGA at the firmware level. Different firmware types can be selected via software, according to the specific setup and acquisition mode.

-

Common trigger: all channels acquire simultaneously with a common trigger. The trigger can be fed externally or generated by a combination of individual channel discriminators. This mode is mainly intended for the acquisition of waveforms, like a digital oscilloscope. Options for zero suppression are available to remove not significant data.

-

Independent trigger: suited for trigger-less applications, where no global trigger is needed but each channel acquires waveforms upon its self-trigger which fires through a digital discriminator, independently of the others.

-

DPP: real-time processing in the FPGA allows for the extraction of physical parameters from the waveform (e.g. pulse height, charge, timestamp, PSD), well suited for high counting rate applications. It is yet possible to save both raw waves and parameters.

A template of the firmware is available for customers who want to personalize the acquisition to implement custom algorithms for pulse processing in the open FPGA. The user can have control of the data output information and customize the trigger logic to get several combinations of self-triggers and I/O signals to validate or discard the events.

Custom software can run on the onboard CPU for data reduction and analysis. Multi-board synchronization can be implemented via backplane or front panel easy-cabling options.

The communication interface selection offers fast readout options: USB 3.0 type-C and 1/10 Gigabit Ethernet or optional Optical (CONET – CAEN Daisy Chainable Optical Link Protocol Available on request) Links.

Supported third-party software:

Features

-

16-bit @ 125 MS/s ADC – TEST Prod 14:22

-

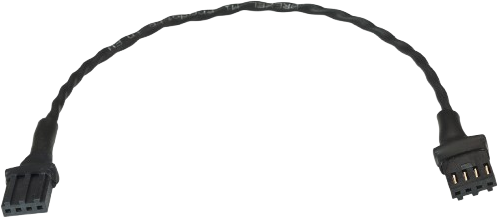

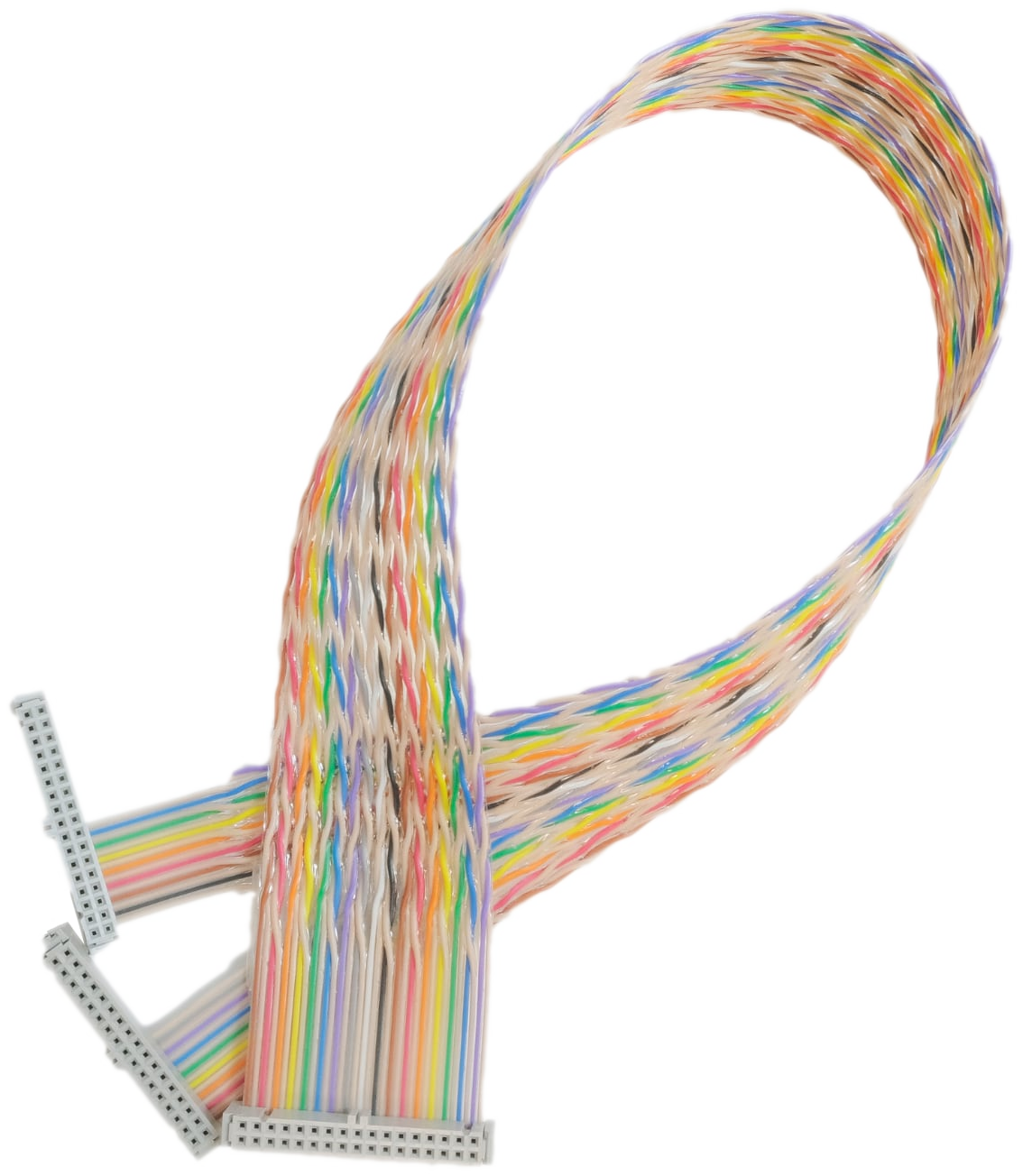

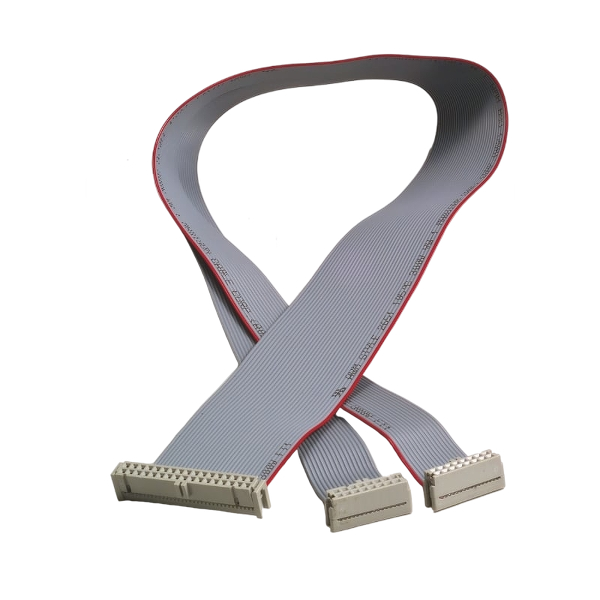

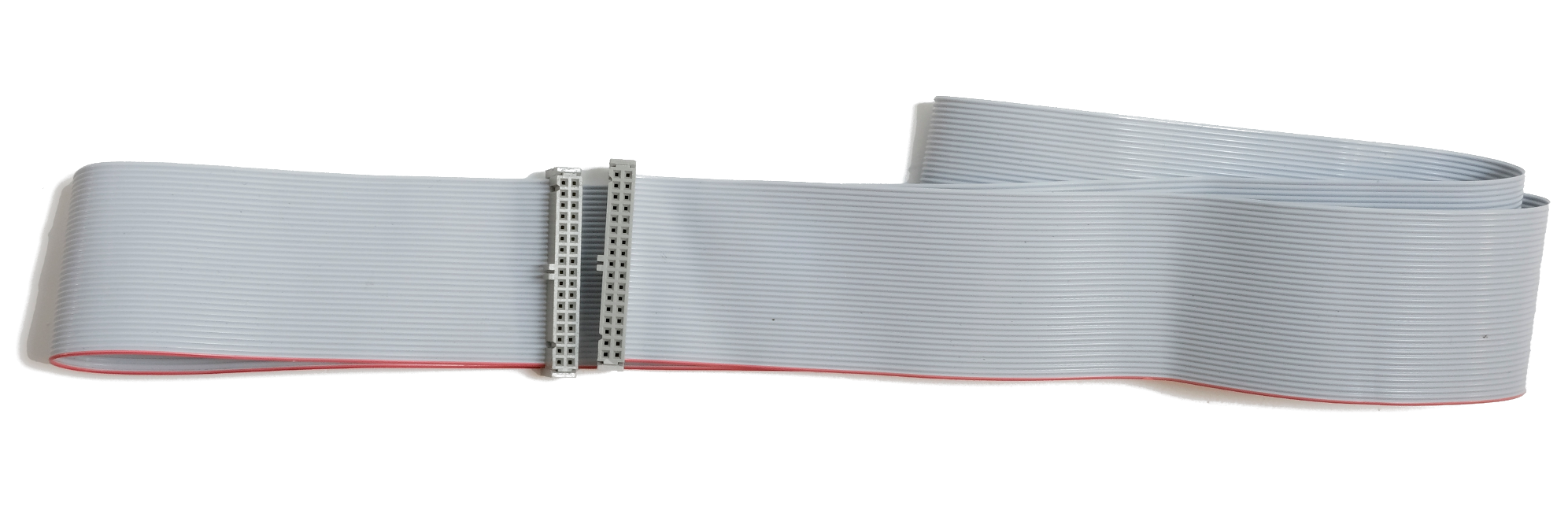

64 analog inputs, differential or single-ended, on four 2mm 40-pin header connectors

-

2Vpp input range, fixed Analog Gain x1

-

Open FPGA programming through graphical tool SCI-Compiler

-

Wide range of applications (from Neutrino Physics & Dark Matter to Nuclear and Particle Physics to Spectroscopic Imaging)

-

Suited for signals from Semiconductor Detectors coupled with CSPs (Si, HPGe) or scintillators coupled with PMTs (NaI, CsI)

-

On-board firmware selection for different acquisition modes:

-

Scope mode (simultaneous raw waveform acquisition on common trigger)

-

DPP-PHA mode (pulse height and time acquisition on independent channel self-triggers)

-

DPP-PSD mode (pulse shape discrimination and time acquisition on independent channel self-triggers)

-

Predisposition for other algorithms like zero suppression and data reduction

-

-

Multi-board synchronization and system building capabilities

-

Rack mount brackets included

-

Front panel fully programmable I/Os (4 LEMO TTL/NIM and 16 LVDS)

-

Special 125MS/s 14bit DAC output (LEMO) for signal inspection, pulse generation, majority level

-

2.5GB of Total Acquisition memory (DDR4)

-

On-board Zynq® UltraScale +™ MPSoC integrating an Arm®-based CPU running Linux®

-

Multi Interface: USB-3.0 and 1/10 GbE or CONET Available on request optical link (switchable on the same socket)

-

SDK for embedded Arm and host PC

DT2740: Data Sheets

DT2740: Manuals

DT2740: Download