# How to make channel correlations with CAEN Digitizers

The complete guide with step-by-step instructions

# Purpose of the Document

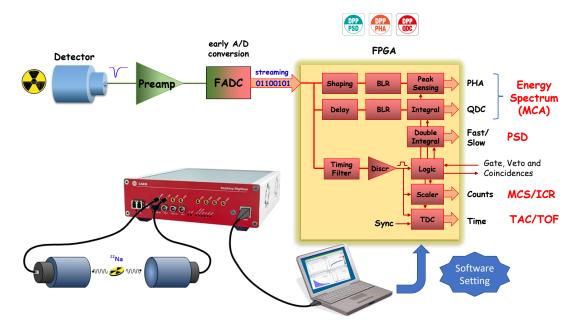

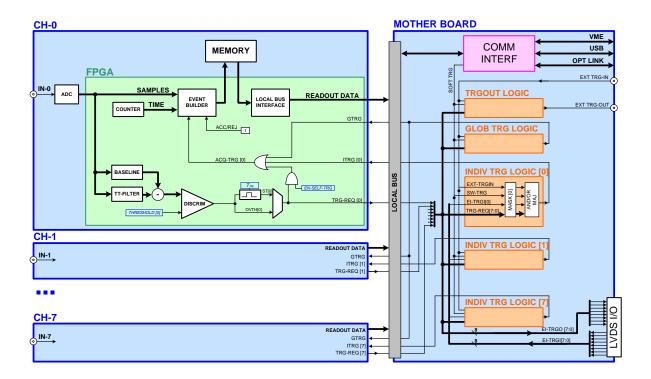

This guide wants to provide detailed instructions on how to implement channel correlations with CAEN digitizers, equipped either with WR or DPP firmware, and MCAs, presenting a DPP-PHA firmware.

For any reference to registers in this user manual, please refer to the related document at the module web page.

# **Change Document Record**

| Date                         | Revision | Changes                                                                                     |

|------------------------------|----------|---------------------------------------------------------------------------------------------|

| Sep. 23 <sup>rd</sup> , 2013 | 00       | Initial Release                                                                             |

|                              |          | Fully revised version. Added support to MC <sup>2</sup> Analyzer.                           |

| Jul. 4 <sup>th</sup> , 2016  | 01       | Added support to x730, x725, 781, and 790 series.                                           |

|                              |          | DPP-CI no longer supported                                                                  |

|                              |          | Modified register 0x1n84 for DPP-PSD of 725 and 730                                         |

|                              |          | series (revision <b>4.11_136.10</b> on). Modified register                                  |

|                              |          | 0x1nA0 for DPP-PHA of 725 and 730 series (revision                                          |

| Nov. 22 <sup>nd</sup> , 2016 | 02       | <b>4.11_139.5</b> on). Added example for 780 series.                                        |

|                              |          | Modified bits[11:10] of register 0x811C. Corrected                                          |

|                              |          | examples for 725-730 DPP-PHA. Fully revised Chapter 5                                       |

|                              |          | in "How to Veto the acquisition".                                                           |

|                              |          | Modified examples for DPP-PSD of 725 and 730 series:                                        |

| Mar. 14 <sup>th</sup> , 2017 | 03       | latency window inside the couple set to 2 clock cycles;                                     |

| Widi. 14 , 2017              |          | trigger validation mask corrected to 0xFFFFFFFF; added                                      |

|                              |          | example for coincidences among 16 channels (VME).                                           |

|                              |          | Reviewed Cover and End pages. Enumerated document                                           |

| Oct. 10 <sup>th</sup> , 2025 | 04       | sections. Updated Chap. 1, Chap. 2, Chap. 4, Chap. 5,                                       |

| 000. 10 , 2025               | 04       | Chap. <b>6</b> , Chap. <b>11</b> . Added Chap. <b>3</b> , Chap. <b>7</b> , Chap. <b>8</b> , |

|                              |          | Chap. <b>9</b> and Chap. <b>10</b> .                                                        |

## Symbols, Abbreviated Terms and Notations

A/D Analog to Digital

ADC Analog-to-Digital Converter

BLR BaseLine Restorer

CI Charge Integration

DAQ Data Acquisition

DPP Digital Pulse Processing

FADC Flash Analog to Digital Converter FPGA Field Programmable Gate Array

ICR **Incoming Count Rate** MCA Multi-Channel Analyzer MCS Multi-Channel Scaler OS **Operating System** PC **Personal Computer** PHA Pulse Height Analysis  $\mathsf{PMT}$ Photo Multiplier Tube PSD **Pulse Shape Discrimination** QDC Charge-to-Digital Converter TAC Time-to-Amplitude Converter

TCP/IP Transmission Control Protocol/Internet Protocol

TDC Time-to-Digital Converter

TOF Time-of-Flight

USB Universal Serial Bus

WR Waveform Recording

& AND, coincidence

|| OR

⊕ XOR, anti-coincidence

#### **Reference Documents**

- [RD1] W. R. Leo. *Techniques for Nuclear and Particle Physics Experiments*. Ed. by Springer. II ed.

- [RD2] K. S. Crane. Introductory nuclear physics. Ed. by J. Wiley and sons

- [RD3] G. F. Knoll. Radiation detection and measurement. Ed. by J. Wiley and sons. III ed.

- [RD4] UM5960 CoMPASS User Manual

- [RD5] UM5175 V2495 User Manual

- [RD6] UM6508 DT5495 User Manual

- [RD7] GD6300 CoMPASS QuickStart Guide

- [RD8] AN2086 Synchronization of a multi-board acquisition systems with CAEN digitizers

- [RD9] UM4380 725-730 DPP-PSD Registers Description

- [RD10] UM5678 725-730 DPP-PHA Registers Description

- [RD11] UM11802 2730 FELib PSD Parameters User Manual

- [RD12] UM8762 2740 FELib PSD Parameters User Manual

- [RD13] UM11796 2745 FELib PSD Parameters User Manual

- [RD14] UM7788 2740 FELib PHA Parameters User Manual

- [RD15] UM11794 2745 FELib PHA Parameters User Manual

- [RD16] UM11800 2730 FELib Scope Parameters User Manual

- [RD17] UM7787 2740 FELib Scope Parameters User Manual

- [RD18] UM11792 2745 FELib Scope Parameters User Manual

- [RD19] UM11844 2751 FELib Scope Parameters User Manual

- [RD20] UM4855 720 DPP-PSD Registers Description

- [RD21] UM5110 751 DPP-PSD Registers Description

- [RD22] UM5416 DT5790 DPP-PSD Registers Description

- [RD23] UM6769 724-781 DPP-PHA Registers Description

- [RD24] UM6771 780 DPP-PHA Registers Description

- [RD25] UM3148 DT5730/DT5725 User Manual

- [RD26] UM3147 N6730/N6725 User Manual

- [RD27] UM2792 V1730/VX1730 & V1725/VX1725 User Manual

- [RD28] UM2754 WaveCatcher User Manual

- [RD29] UM2091 CAEN WaveDump User Manual

- [RD30] UM5961 720 WR Registers Description

- [RD31] UM5918 724 WR Registers Description

- [RD32] UM6009 751 WR Registers Description

- [RD33] UM7934 WaveDump2 User Manual

All CAEN documents can be downloaded at:

https://www.caen.it/support-services/documentation-area/ (login required)

#### **Manufacturer Contacts**

#### CAEN S.p.A.

Via Vetraia, 11 55049 Viareggio (LU) - ITALY Tel. +39.0584.388.398 Fax +39.0584.388.959 www.caen.it | info@caen.it ©CAEN SpA – 2025

### Limitation of Responsibility

If the warnings contained in this manual are not followed, CAEN will not be responsible for damage caused by improper use of the device. The manufacturer declines all responsibility for damage resulting from failure to comply with the instructions for use of the product. The equipment must be used as described in the user manual, with particular regard to the intended use, using only accessories as specified by the manufacturer. No modification or repair can be performed.

#### **Disclaimer**

No part of this manual may be reproduced in any form or by any means, electronic, mechanical, recording, or otherwise, without the prior written permission of CAEN SpA.

The information contained herein has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. CAEN SpA reserves the right to modify its products specifications without giving any notice; for up to date information please visit www.caen.it.

## Made in Italy

We remark that all our boards have been designed and assembled in Italy. In a challenging environment where a competitive edge is often obtained at the cost of lower wages and declining working conditions, we proudly acknowledge that all those who participated in the production and distribution process of our devices were reasonably paid and worked in a safe environment (while this is true for the boards marked "MADE IN ITALY", we cannot guarantee for third-party manufactures).

# Index

| Pu  | rpose            | of this N      | Manual                                                                                                                                                 | 2               |

|-----|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Ch  | ange c           | locumen        | nt record                                                                                                                                              | 2               |

| Sy  | mbols,           | , abbrevi      | iated terms and notation                                                                                                                               | 3               |

| Re  | ferenc           | e Docum        | nents                                                                                                                                                  | 4               |

| M   | anufac           | turer Co       | ntacts                                                                                                                                                 | 5               |

| Lir | nitatio          | n of Res       | ponsibility                                                                                                                                            | 5               |

| Di  | sclaim           | er             |                                                                                                                                                        | 5               |

| M   | ade in           | Italy .        |                                                                                                                                                        | 5               |

| 1   | Intro<br>1.1     |                | dences: the traditional approach                                                                                                                       | <b>12</b><br>13 |

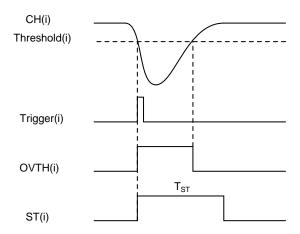

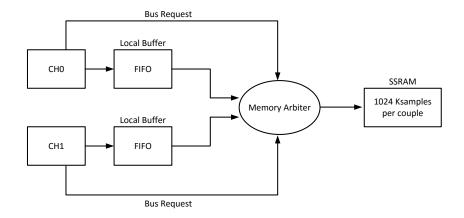

| 2   | <b>Coinc</b> 2.1 | DPP No         | with CAEN DPP firmware                                                                                                                                 |                 |

|     | 2.2              | DPP Co         | eneration                                                                                                                                              |                 |

|     |                  | 2.2.1<br>2.2.2 | eneration                                                                                                                                              | 20<br>23<br>23  |

|     | 2.3              | Channe         | el correlations with CAEN DPP Firmware in Digitizers of the Second Generation                                                                          | 24              |

| 3   |                  |                | tware for coincidences with CAEN DPP firmware                                                                                                          | 25              |

|     | 3.1<br>3.2       |                | e Coincidences                                                                                                                                         |                 |

|     | 3.3              |                | e onboard Coincidences                                                                                                                                 |                 |

| 4   | Exam             | ples for       | DPP-PSD firmware                                                                                                                                       | 31              |

|     | 4.1              | How to         | configure the registers - 720 and 751 series with DPP-PSD                                                                                              |                 |

|     | 4.2              | Exampl         | les for 720-751 series                                                                                                                                 |                 |

|     |                  | 4.2.1          | Coincidence between channel 0 and channel 1 (ch0 & ch1)                                                                                                |                 |

|     |                  | 4.2.2          | Anti-coincidence between two channels (ch0 $\oplus$ ch1)                                                                                               |                 |

|     |                  | 4.2.3          | Coincidence among four channels (ch0 & ch1 & ch2 & ch3)                                                                                                | 34              |

|     |                  | 4.2.4          | Coincidence between channel 0 and channel 1, coincidence between channel 2 and channel 3 (ch0 & ch1), (ch2 & ch3)                                      | 35              |

|     |                  | 4.2.5          | Coincidence among eight channels (ch0 & ch1 & ch2 & ch3 & ch4 & ch5 & ch6 & ch7) - VME only                                                            | 36              |

|     | 4.3              | How to         | configure the registers - 725 and 730 series with DPP-PSD                                                                                              | 37              |

|     | 4.4              |                | les for 725-730 series                                                                                                                                 | 39              |

|     |                  | 4.4.1          | Coincidence between channel 0 and channel 1 (ch0 & ch1)                                                                                                | 39              |

|     |                  | 4.4.2          | Coincidence inside the couples (ch0 & ch1), (ch2 & ch3), (ch4 & ch5), (ch6 & ch7)                                                                      | 39              |

|     |                  | 4.4.3          | Anti-coincidence between PAIRED channels: (ch0 $\oplus$ ch1), (ch2 $\oplus$ ch3), (ch4 $\oplus$ ch5), (ch6 $\oplus$ ch7)                               | 40              |

|     |                  | 4.4.4          | Coincidence inside the couples (ch0 & ch1), (ch2 & ch3), (ch4 & ch5), (ch6 & ch7), (ch8 & ch9), (ch10 & ch11), (ch12 & ch13), (ch14 & ch15) - VME only | 41              |

|     |                  | 4.4.5          | Coincidence among four channels (four different couples, ch0 & ch2 & ch4 & ch6)                                                                        | 43              |

|     |                  | 4.4.6          | Coincidence among four channels (two different couples, ch0 & ch1 & ch2 & ch3)                                                                         | 44              |

|   |                 | 4.4.7          | ch6 & ch7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45          |

|---|-----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|   |                 | 4.4.8          | Coincidence between couples of channels in OR:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|   |                 |                | (ch0    ch1) & (ch2    ch3) & (ch4    ch5) & (ch6    ch7) & (ch8    ch9) & (ch10    ch11) & (ch12    c & (ch14    ch15) - VME only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ch13)<br>46 |

|   |                 | 4.4.9          | Coincidence among eight channels (eight different couples, ch0 & ch2 & ch4 & ch6 & ch8 & ch10 & ch12 & ch14) - VME only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 48          |

|   |                 | 4.4.10         | Coincidence among eight channels (four different couples, ch0 & ch1 & ch2 & ch3 & ch4 & ch5 & ch6 & ch7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49          |

|   |                 | 4.4.11         | Coincidence among sixteen channels (ch0 & ch1 & ch2 & ch3 & ch4 & ch5 & ch6 & ch7 & ch8 & ch9 & ch10 & ch11 & ch12 & ch13 & ch14 & ch15) - VME only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50          |

|   |                 | 4.4.12         | Coincidence between ch6 and ch7, in AND with at least one AND of the other pairs: ((ch6 & ch7) & (ch0 & ch1)) $  $ ((ch6 & ch7) & (ch2 & ch3)) $  $ ((ch6 & ch7) & (ch4 & ch5))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51          |

|   |                 | 4.4.13         | Coincidence between ch2 and ch3, in AND with at least one of other 4 channels (ch4-5-6-7): (ch2 & ch3) & (ch4    ch5    ch6    ch7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52          |

|   |                 | 4.4.14         | Majority of at least three channels among couples of the whole board (sixteen channels) - VME only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

|   |                 | 4.4.15         | Majority of two or more couples for the whole board (eight couples) - VME only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56          |

|   |                 | 4.4.16         | Global Trigger to all Channels by the coincidence between ch0 and ch1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58          |

|   |                 | 4.4.17         | Global Trigger on ch0, ch1, ch2, ch3 as OR of their Trigger Request and Global Trigger on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

|   |                 |                | ch4, ch5, ch6, ch7 as OR of their Trigger Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58          |

|   |                 | 4.4.18         | LVDS Global trigger - VME only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|   | 4.5             |                | configuration requests from users                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

|   | 1.5             | 4.5.1          | Coincidence among four channels (ch0 & ch1 & ch4 & ch5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

|   |                 | 4.5.2          | Coincidence among four channels (ch0 & ch1 & ch6 & ch7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

|   |                 | 4.5.3          | Coincidence among four channels (ch2 & ch3 & ch4 & ch5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

|   |                 | 4.5.4          | Coincidence among four channels (ch2 & ch3 & ch6 & ch7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

|   | 4.6             |                | configure the registers - DT5790 with DPP-PSD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

|   | 4.7             |                | es for DT5790                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

|   | 4.7             | ·=             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

|   |                 | 4.7.1<br>4.7.2 | Coincidence between channel 0 and channel 1 (ch0 & ch1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

| 5 | Exam            | ples for I     | DPP-PHA firmware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65          |

|   | 5.1             | -              | configure the registers - 724, 781 and 782 series with DPP-PHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|   | 5.2             |                | es for 724, 781 series and V1782 with DPP-PHA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

|   | 3.2             | 5.2.1          | Coincidence between channel 0 and channel 1 (ch0 & ch1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

|   |                 | 5.2.2          | Anti-coincidence between channel 0 and channel 1 (ch0 $\oplus$ ch1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

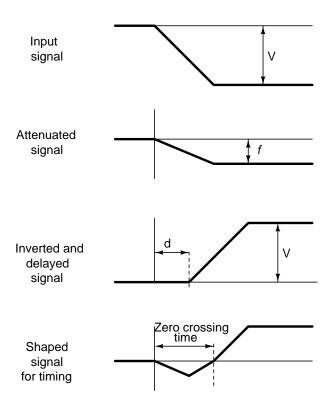

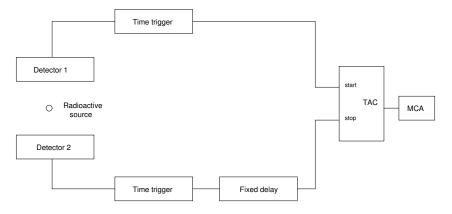

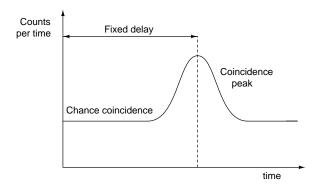

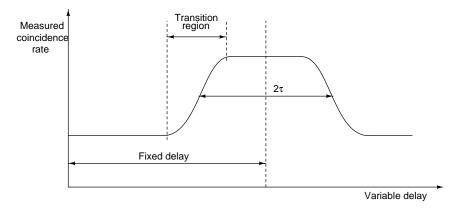

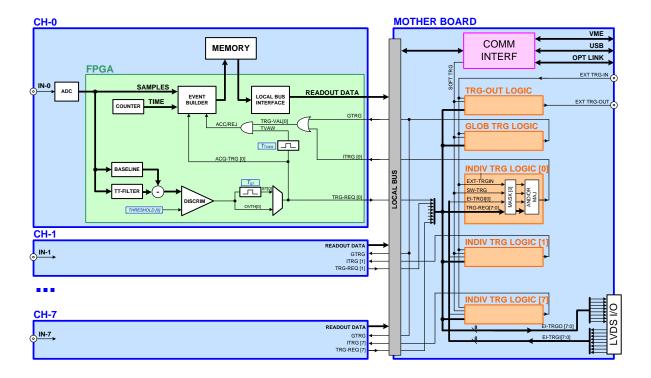

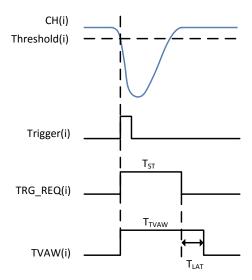

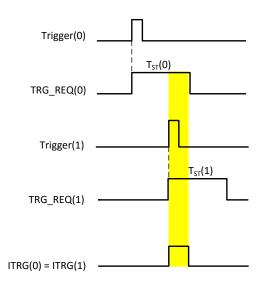

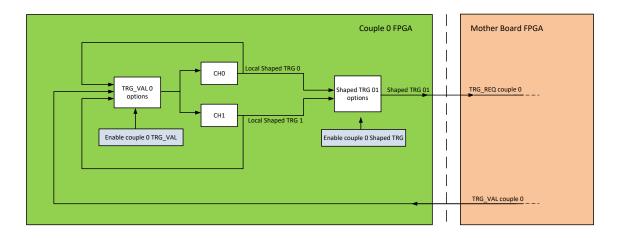

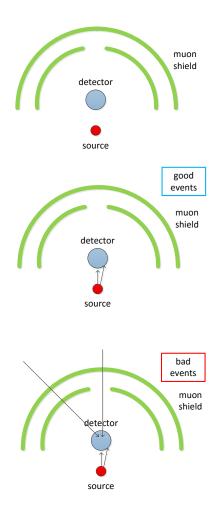

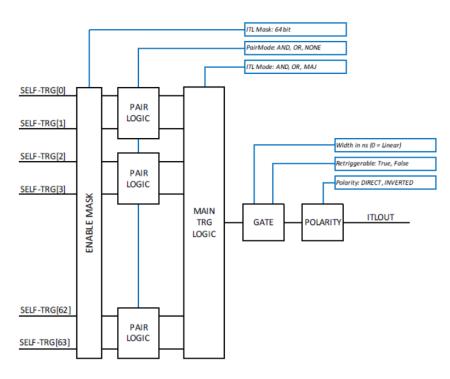

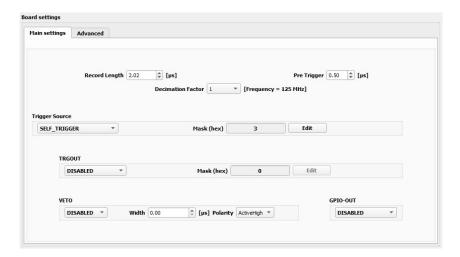

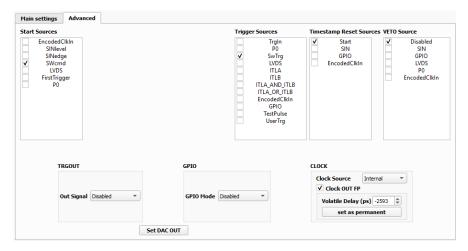

|   |                 | 5.2.3          | Coincidence among four channels (ch0 & ch1 & ch2 & ch3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |