-

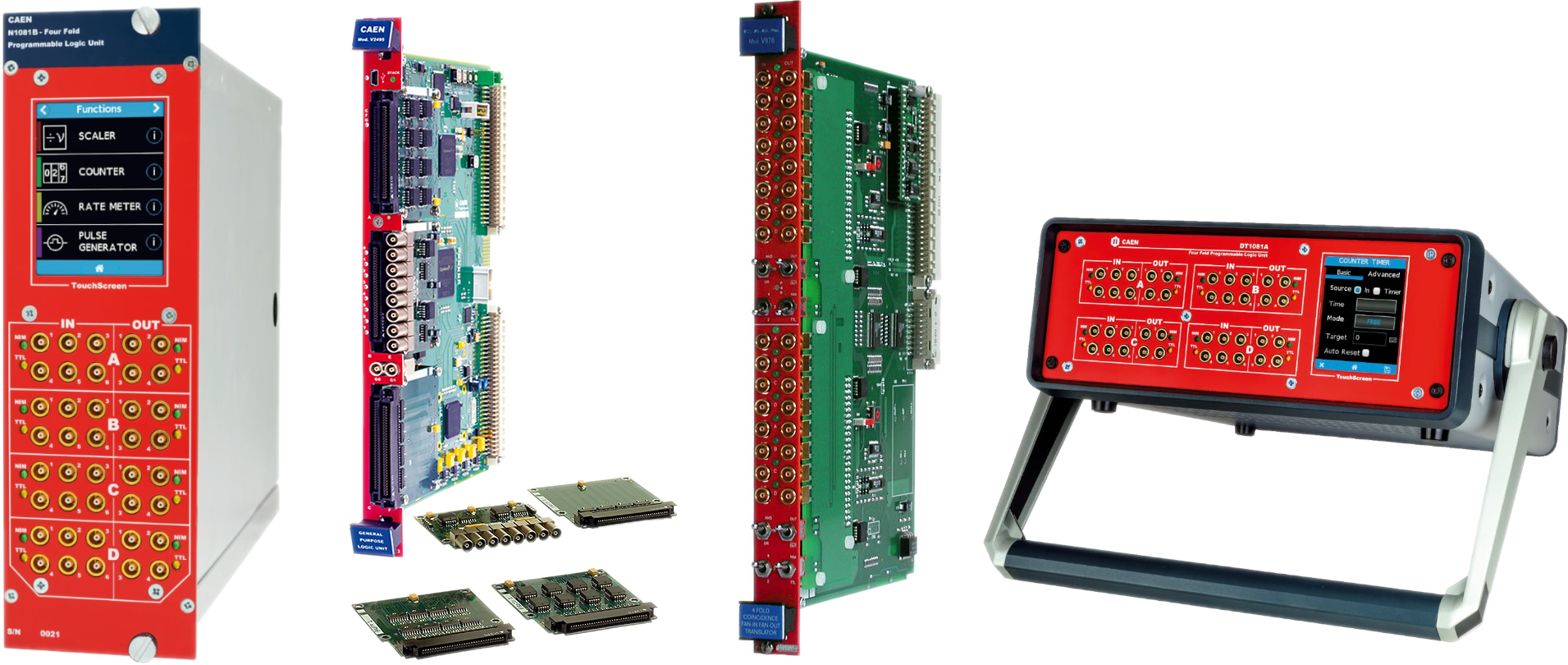

Handy Desktop form factor

-

Wide range of user-selectable functionalities: logic functions, counting, timing, digital pulse generator

-

4 independent sections, each with:

-

6 NIM/TTL/ANALOG input

-

4 NIM/TTL output

-

-

Input stage with Gate&Delay and Leading Edge Discriminator for analog input signals

-

Output stage with Monostable capability

-

2.8” touch screen display with user-friendly widgets to configure each section and monitor real-time data

-

Ethernet (1 Gbps) and USB2.0 connectivity

-

Web-based Graphical User Interface to remotely control the module and access advanced features

Digital

Coincidence/Logic/Trigger Units

Coincidence/Logic/Trigger Units Models

DT1081B

DT5495

-

User Programmable FPGA

-

Compact Desktop form factor

-

Up to 162 inputs, up to 130 outputs

-

LVDS/ECL/PECL/NIM/TTL

-

3 expansion slots for piggyback board:

-

A395A 32 LVDS/ECL/PECL input ch.

-

A395B 32 LVDS output ch.

-

A395C 32 ECL output ch.

-

A395D 8 NIM/TTL input/output ch.

-

A395E 8 Analog output 16bit ch.

-

-

32 independent programmable Gate and Delay Generator

-

Ethernet and Mini-USB 2.0 Connection

-

Available in VME version V2495

-

Supported by SCI-Compiler software tool

N1081B

-

Double-width NIM unit

-

Wide range of user-selectable functionalities: logic functions, counting, timing, digital pulse generator.

-

4 independent sections, each with:

-

6 NIM/TTL/ANALOG input

-

4 NIM/TTL output

-

-

Input stage with Gate&Delay and Leading Edge Discriminator for analog input signals

-

Output stage with Monostable capability

-

2.8” touch screen display with user-friendly widgets to configure each section and monitor real-time data

-

Ethernet (1 Gbps) and USB2.0 connectivity

-

Web-based Graphical User Interface to remotely control the module and access advanced features

-

Python SDK and libraries available for free

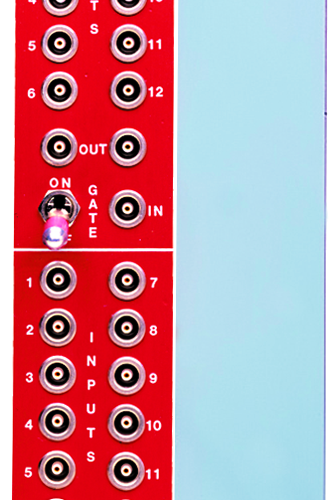

N113

- 2 independent OR sections, 12 inputs each

- 1 GATE signal per section

- Cascadeable sections

- Less than 10 ns input/output delay

N405

-

Three independent sections with 4 standard NIM inputs each

-

AND, OR, MAJORITY function selectable for each section

-

One auxiliary NIM output per section whose width is equal to the coincidence duration

-

NIM shaped outputs with Fan Out of two

-

One negated NIM shaped output per section

-

One VETO input per section

-

Front panel trimmer for output width adjustment on each section

N408

- 24 DC-coupled Std. NIM inputs

- 50 MHz maximum input frequency

- Majority level settable via front panel trimmer

- Auxiliary input for adder function

- Normal and complementary NIM outputs with adjustable width (40 to 350 ns)

- Normal and complementary linear outputs

- Retriggerable or non retriggerable operating mode selectable through internal jumper

N455

-

4 identical independent sections

-

Two inputs per section

-

130 MHz Max input frequency

-

6 ns double pulse resolution

-

10 ns I/O delay

-

Switch selectable AND/OR logical function

-

Adjustable output FWHM (4 to 650 ns)

-

Overlap output

-

Common Veto

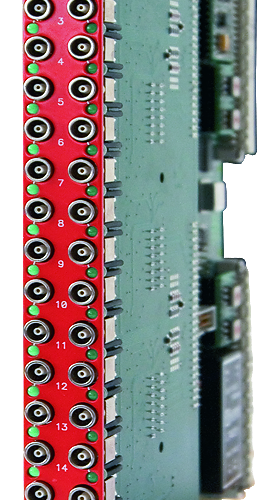

V1495

-

User customisable FPGA Unit (with preloaded demo code)

-

LVDS/ECL/PECL inputs (differential)

-

64 inputs, expandable to 162 (with 32 outputs)

-

32 outputs, expandable to 130 (with 64 inputs)

-

405 MHz maximum frequency supported by clock tree for registered logic

-

I/O delay smaller than 15 ns (in Buffer Mode)

-

Programmable 3-color LED

-

Libraries (C and LabView) and Software tools for Windows and Linux

V2495

-

User customisable FPGA Unit

-

LVDS/ECL/PECL inputs (differential)

-

64 inputs, expandable to 162 (with 32 outputs)

-

32 outputs, expandable to 130 (with 64 inputs)

-

32 independent programmable Gate and Delay Generators

-

3 expansion slots for piggyback board

-

Mini-USB 2.0 Connection

-

Available in Desktop version DT5495

V976

-

Four independent sections with four channels each

-

TTL and NIM inputs automatically detected

-

NIM/TTL selectable output level

-

AND, OR, Majority function with selectable number of inputs

-

Logic Fan In / Fan Out

-

Selectable direct or negated output