Rev. 12 - September 5<sup>th</sup>, 2025

# V1742/VX1742

16+1 Channel 12 bit 5 GS/s

Switched Capacitor Digitizer

n

# Register your device

Register your device to your **MyCAEN+** account and get access to our customer services, such as notification for new firmware or software upgrade, tracking service procedures or open a ticket for assistance. **MyCAEN+** accounts have a dedicated support service for their registered products. A set of basic information can be shared with the operator, speeding up the troubleshooting process and improving the efficiency of the support interactions.

**MyCAEN+ dashboard is designed to offer you a direct access to all our after sales services. Registration is totally free, to create an account go to <https://www.caen.it/become-mycaenplus-user> and fill the registration form with your data.**

<https://www.caen.it/become-mycaenplus-user/>

## Purpose of the Document

This document contains the full hardware description of the V1742 and VX1742 CAEN digitizers and their principle of operating as **Waveform Recording Digitizer** (basing on the hereafter called "*waveform recording firmware*"). The reference firmware revision is: **4.30\_1.08**.

**For higher releases compatibility, check in the firmware revision history files.**

**For any reference to registers in this user manual, please refer to document [RD1] at the digitizer web page.**

## Change Document Record

| Date                             | Revision | Changes                                                                                                                                                                                                                                                                                  |

|----------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                                | 00-06    | N/A                                                                                                                                                                                                                                                                                      |

| Jan. 27 <sup>th</sup> , 2017     | 07       | Revised text layout. Improved text description to make it clearer.                                                                                                                                                                                                                       |

| Feb. 5 <sup>th</sup> , 2020      | 08       | Updated Sections: <b>8.2, 9.5, 9.13.3, 9.11, 13.3</b> .<br>Reviewed Sections: <b>9.15, 9.16, 10.1</b> .<br>Added Sections: <b>9.17</b> .                                                                                                                                                 |

| Apr. 4 <sup>th</sup> , 2022      | 09       | Updated text formatting and copyrights. Added <b>Safety Notices, Chap. 5, Chap. 7, Chap. 14, Chap. 15, Chap. 16</b> , Updated <b>Chap. 1 (Tab. 1.1), Chap. 3, Chap. 4, Chap. 8, Chap. 9 (Sec. 9.7.3, Sec. 9.8.2, Sec. 9.9.3, Sec. 9.9.4, Sec. 9.13, Sec. 9.16), Chap. 10, Chap. 12</b> . |

| January 31 <sup>st</sup> , 2023  | 10       | Added the extended 60-bit Trigger Timestamp specifications in <b>Chap. 3</b> and the description in <b>Sec. 9.8.2</b> .                                                                                                                                                                  |

| June 21 <sup>st</sup> , 2023     | 11       | Added information about the input range customization at 2 V <sub>pp</sub> in <b>Chap. 1, Chap. 3, Chap. 8, and Chap. 9</b> .                                                                                                                                                            |

| September 5 <sup>th</sup> , 2025 | 12       | Reviewed End page. Replaced references to CAENUpgrader with CAENToolbox. Updated <b>Safety Notices, Chap. 1, Tab 1.1, Chap. 3, Chap. 6, Chap. 7, Sec. 9.8.2, Sec. 9.11, Sec. 9.16, Chap. 10, Chap. 11, Sec. 13.3</b> . Added Sec. <b>9.9.5.1, Sec. 11.1</b> .                            |

# Symbols, Abbreviated Terms, and Notations

|        |                                            |

|--------|--------------------------------------------|

| ADC    | Analog-to-Digital Converter                |

| AMC    | ADC & Memory Controller                    |

| CML    | Current-Mode Logic                         |

| DAQ    | Data Acquisition                           |

| DAC    | Digital-to-Analog Converter                |

| DC     | Direct Current                             |

| DRS4   | Domino Ring Sampler 4                      |

| ECL    | Emitter Coupled Logic                      |

| FPGA   | Field-Programmable Gate Array              |

| GPI    | General Purpose Input                      |

| GPO    | General Purpose Output                     |

| LVDS   | Low-Voltage Differential Signal            |

| LVPECL | Low-Voltage Positive Emitter Coupled Logic |

| NIM    | Nuclear Instrumentation Module             |

| PECL   | Positive Emitter Coupled Logic             |

| PLL    | Phase-Locked Loop                          |

| ROC    | ReadOut Controller                         |

| SW     | SoftWare                                   |

| TTL    | Transistor-Transistor Logic                |

| TTT    | Trigger Time Tag                           |

| USB    | Universal Serial Bus                       |

## Reference Documents

- [RD1] UM5698 - 742 Registers Description

- [RD2] UM11111 – CAEN Toolbox User Manual

- [RD3] Precautions for Handling, Storage and Installation

- [RD4] UM1935 - CAENDigitizer User & Reference Manual

- [RD5] UM2091 - CAEN WaveDump User Manual

- [RD6] UM7715 - CAENVMElib User & Reference Manual

- [RD7] UM1934 - CAENComm User & Reference Manual

- [RD8] GD5695 - 742 Quick Start Guide

- [RD9] AN2086 - Synchronization of CAEN Digitizers in Multiple Board Acquisition Systems

- [RD10] UM10551 A5818 Technical Information Manual

- [RD11] UM7685 - V3718 & VX3718 User & Reference Manual

- [RD12] UM8305 - V4718 & VX4718 User & Reference Manual

- [RD13] DS7799 - A4818 Adapter Data Sheet

All CAEN documents can be downloaded at:

<https://www.caen.it/support-services/documentation-area/> (login required)

## Manufacturer Contacts

### CAEN S.p.A.

Via Vетраia, 11 55049 Viareggio (LU) - ITALY

Tel. +39.0584.388.398 Fax +39.0584.388.959

[www.caen.it](http://www.caen.it) | [info@caen.it](mailto:info@caen.it)

©CAEN SpA – 2025

## Limitation of Responsibility

If the warnings contained in this manual are not followed, CAEN will not be responsible for damage caused by improper use of the device. The manufacturer declines all responsibility for damage resulting from failure to comply with the instructions for use of the product. The equipment must be used as described in the user manual, with particular regard to the intended use, using only accessories as specified by the manufacturer. No modification or repair can be performed.

## Disclaimer

No part of this manual may be reproduced in any form or by any means, electronic, mechanical, recording, or otherwise, without the prior written permission of CAEN SpA.

The information contained herein has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. CAEN SpA reserves the right to modify its products specifications without giving any notice; for up to date information please visit [www.caen.it](http://www.caen.it).

## Made in Italy

We remark that all our boards have been designed and assembled in Italy. In a challenging environment where a competitive edge is often obtained at the cost of lower wages and declining working conditions, we proudly acknowledge that all those who participated in the production and distribution process of our devices were reasonably paid and worked in a safe environment (while this is true for the boards marked "MADE IN ITALY", we cannot guarantee for third-party manufacturers).

# Index

|                                                            |           |

|------------------------------------------------------------|-----------|

| <b>Purpose of the Document</b> . . . . .                   | <b>3</b>  |

| <b>Change Document Record</b> . . . . .                    | <b>3</b>  |

| <b>Symbols, Abbreviated Terms, and Notations</b> . . . . . | <b>4</b>  |

| <b>Reference Documents</b> . . . . .                       | <b>4</b>  |

| <b>Manufacturer Contacts</b> . . . . .                     | <b>5</b>  |

| <b>Limitation of Responsibility</b> . . . . .              | <b>5</b>  |

| <b>Disclaimer</b> . . . . .                                | <b>5</b>  |

| <b>Made in Italy</b> . . . . .                             | <b>5</b>  |

| <b>1 Introduction</b> . . . . .                            | <b>13</b> |

| <b>2 Block Diagram</b> . . . . .                           | <b>16</b> |

| <b>3 Technical Specifications</b> . . . . .                | <b>17</b> |

| <b>4 Packaging and Compliancy</b> . . . . .                | <b>19</b> |

| <b>5 PID (Product Identifier)</b> . . . . .                | <b>21</b> |

| <b>6 Power Requirements</b> . . . . .                      | <b>23</b> |

| <b>7 Cooling Management</b> . . . . .                      | <b>24</b> |

| 7.1 Cleaning Air Vents . . . . .                           | 24        |

| <b>8 Panels Description</b> . . . . .                      | <b>25</b> |

| 8.1 Front Panel . . . . .                                  | 26        |

| 8.2 Internal Components . . . . .                          | 29        |

| <b>9 Functional Description</b> . . . . .                  | <b>30</b> |

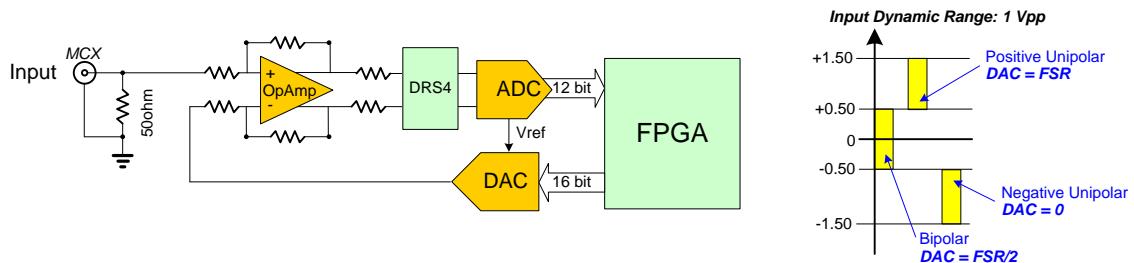

| 9.1 Analog Input Stage . . . . .                           | 30        |

| 9.1.1 DC Offset Setting . . . . .                          | 30        |

| 9.1.2 Additional Input . . . . .                           | 30        |

| 9.2 Domino Ring Sampling . . . . .                         | 31        |

| 9.3 TR0 and TR1 Inputs . . . . .                           | 32        |

| 9.4 Clock Distribution . . . . .                           | 33        |

| 9.5 PLL Mode . . . . .                                     | 34        |

| 9.6 Output Clock . . . . .                                 | 34        |

| 9.7 Data Correction . . . . .                              | 35        |

| 9.7.1 Cell Index Offset Correction . . . . .               | 36        |

| 9.7.2 Sample Index Offset Correction . . . . .             | 37        |

| 9.7.3 Time Correction . . . . .                            | 38        |

| 9.8 Acquisition Modes . . . . .                            | 41        |

| 9.8.1 Acquisition Run/Stop . . . . .                       | 41        |

| 9.8.2 Event Structure . . . . .                            | 41        |

| 9.9 Trigger Management . . . . .                           | 44        |

| 9.9.1 Software Trigger . . . . .                           | 45        |

| 9.9.2 External Trigger . . . . .                           | 45        |

| 9.9.3 Fast ("Low Latency") Trigger . . . . .               | 45        |

|           |                                                                                  |           |

|-----------|----------------------------------------------------------------------------------|-----------|

| 9.9.4     | Self-Trigger . . . . .                                                           | 47        |

| 9.9.5     | How to work with Self-Trigger . . . . .                                          | 48        |

| 9.9.5.1   | Channel Self-Trigger to generate a Global Trigger for the entire board . . . . . | 49        |

| 9.10      | Multi-board Synchronization . . . . .                                            | 50        |

| 9.11      | Front Panel LVDS I/Os . . . . .                                                  | 52        |

| 9.11.1    | Mode 0: REGISTER . . . . .                                                       | 54        |

| 9.11.2    | Mode 1: TRIGGER . . . . .                                                        | 54        |

| 9.11.3    | Mode 2: nBUSY/nVETO . . . . .                                                    | 54        |

| 9.11.4    | Mode 3: LEGACY . . . . .                                                         | 55        |

| 9.12      | Test Pattern Generator . . . . .                                                 | 56        |

| 9.13      | Reset, Clear and Default Configuration . . . . .                                 | 57        |

| 9.13.1    | Global Reset . . . . .                                                           | 57        |

| 9.13.2    | Memory Reset . . . . .                                                           | 57        |

| 9.13.3    | Timer Reset . . . . .                                                            | 57        |

| 9.14      | VMEBus Interface . . . . .                                                       | 58        |

| 9.14.1    | Addressing Capabilities . . . . .                                                | 58        |

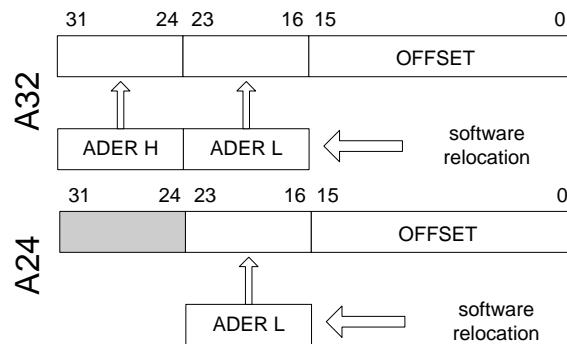

| 9.14.2    | Address Relocation . . . . .                                                     | 59        |

| 9.15      | Data Transfer Capabilities and Events Readout . . . . .                          | 60        |

| 9.15.1    | Block Transfer D32/D64, 2eVME and 2eSST . . . . .                                | 60        |

| 9.15.2    | Chained Block Transfer D32/D64 . . . . .                                         | 61        |

| 9.15.3    | Single D32 Transfer . . . . .                                                    | 61        |

| 9.16      | Optical Link Access . . . . .                                                    | 62        |

| 9.17      | Trigger Rate . . . . .                                                           | 63        |

| 9.17.1    | "Average" Trigger Rate Calculation . . . . .                                     | 64        |

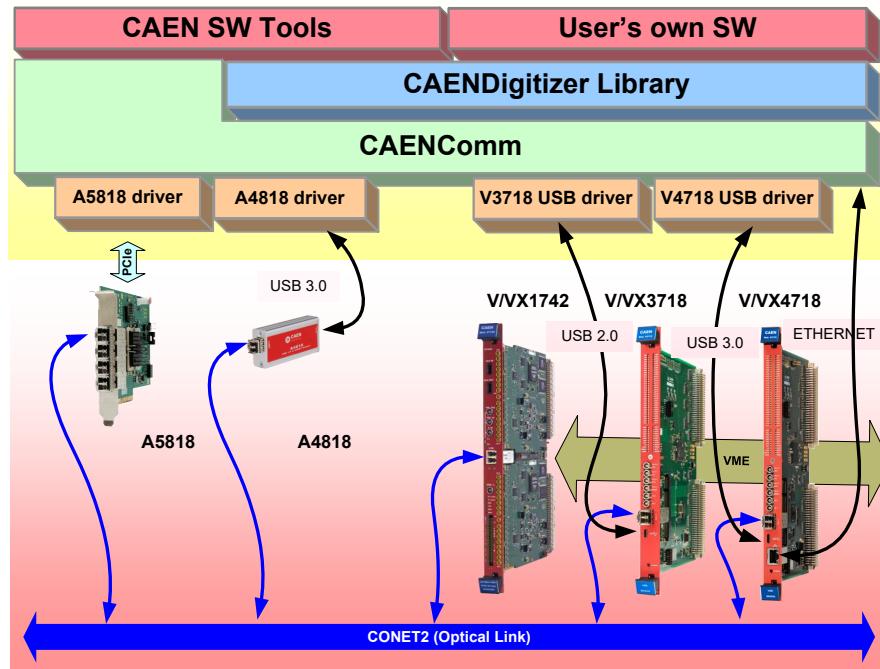

| <b>10</b> | <b>Drivers &amp; Libraries</b> . . . . .                                         | <b>65</b> |

| 10.1      | Drivers . . . . .                                                                | 65        |

| 10.2      | Libraries . . . . .                                                              | 65        |

| <b>11</b> | <b>Software Tools</b> . . . . .                                                  | <b>67</b> |

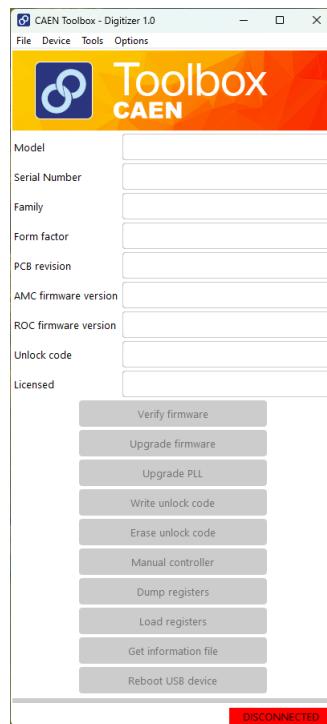

| 11.1      | CAEN Toolbox . . . . .                                                           | 67        |

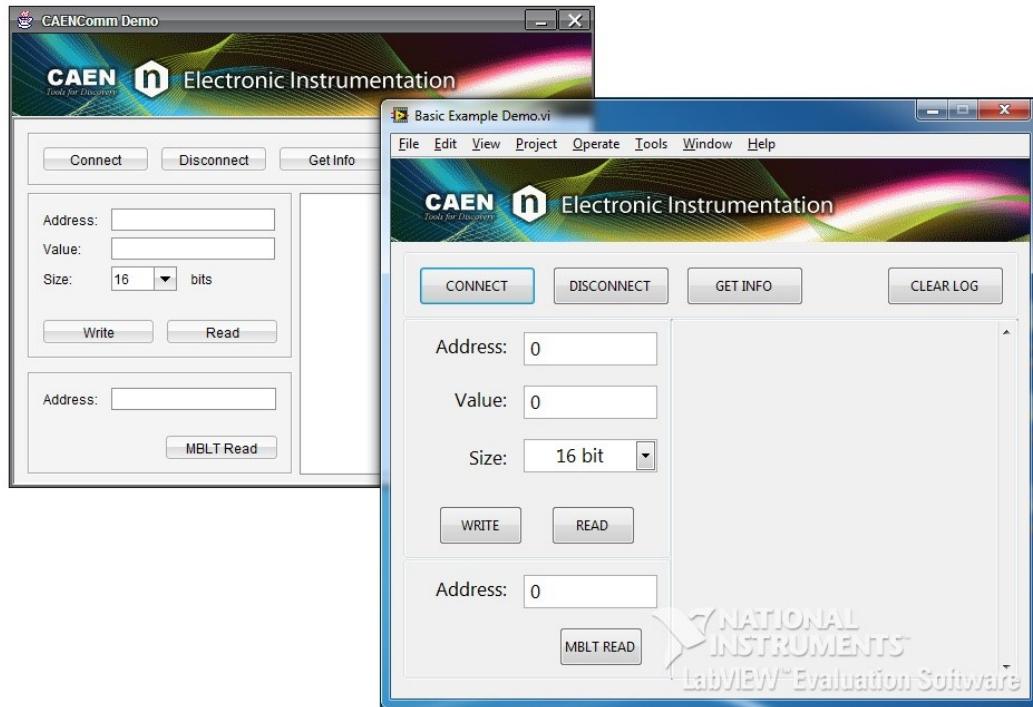

| 11.2      | CAENComm Demo . . . . .                                                          | 68        |

| 11.3      | CAEN WaveDump . . . . .                                                          | 69        |

| <b>12</b> | <b>HW Installation</b> . . . . .                                                 | <b>70</b> |

| 12.1      | Power-on Status . . . . .                                                        | 71        |

| <b>13</b> | <b>Firmware and Upgrades</b> . . . . .                                           | <b>72</b> |

| 13.1      | Firmware Updates . . . . .                                                       | 72        |

| 13.2      | Firmware File Description . . . . .                                              | 73        |

| 13.3      | Troubleshooting . . . . .                                                        | 74        |

| <b>14</b> | <b>Instructions for Cleaning</b> . . . . .                                       | <b>75</b> |

| 14.1      | Cleaning the Touchscreen . . . . .                                               | 75        |

| 14.2      | Cleaning the Air Vents . . . . .                                                 | 75        |

| 14.3      | General Cleaning Safety Precautions . . . . .                                    | 75        |

| <b>15</b> | <b>Device Decommissioning</b> . . . . .                                          | <b>76</b> |

| <b>16</b> | <b>Disposal</b> . . . . .                                                        | <b>77</b> |

| <b>17</b> | <b>Technical Support</b> . . . . .                                               | <b>78</b> |

# List of Figures

|                  |                                                                                                                                                                                                                                                                               |    |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Fig. 2.1</b>  | Block Diagram                                                                                                                                                                                                                                                                 | 16 |

| <b>Fig. 5.1</b>  | PID location on V1742 (the number in the picture is purely indicative)                                                                                                                                                                                                        | 21 |

| <b>Fig. 5.2</b>  | PID location on VX1742 (the number in the picture is purely indicative)                                                                                                                                                                                                       | 22 |

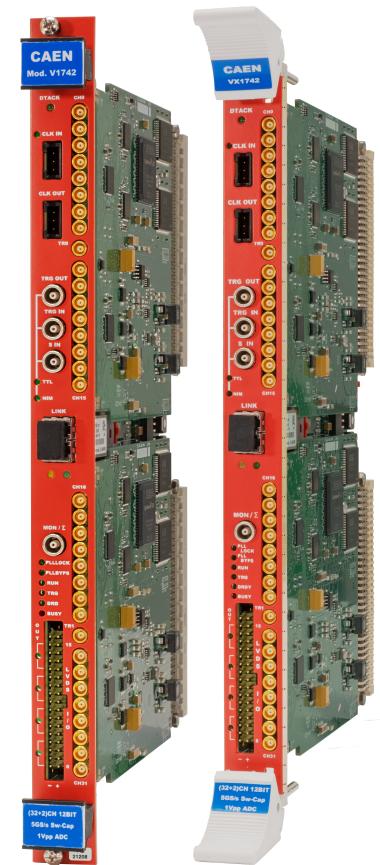

| <b>Fig. 8.1</b>  | Front panels view: V1742 on the left, VX1742 on the right                                                                                                                                                                                                                     | 25 |

| <b>Fig. 8.2</b>  | Rotary and dip switches location                                                                                                                                                                                                                                              | 29 |

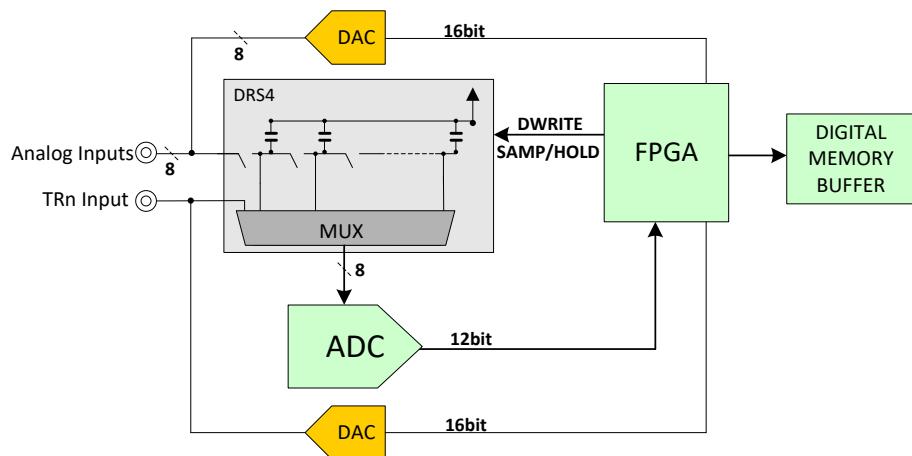

| <b>Fig. 9.1</b>  | Analog input diagram                                                                                                                                                                                                                                                          | 30 |

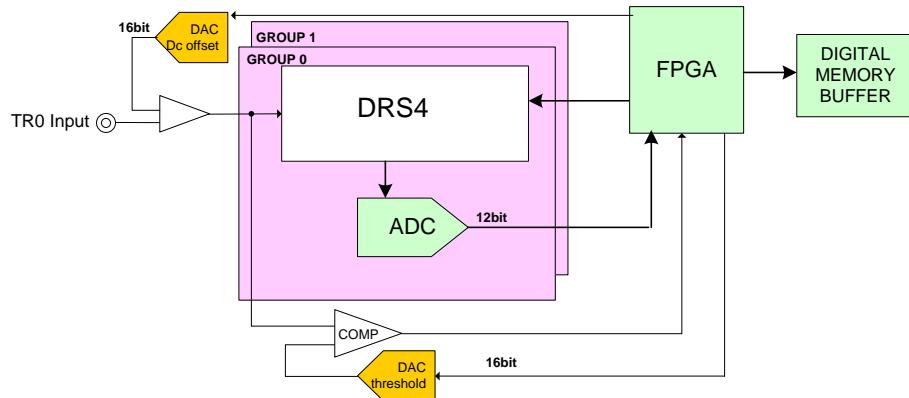

| <b>Fig. 9.2</b>  | Input Diagram                                                                                                                                                                                                                                                                 | 31 |

| <b>Fig. 9.3</b>  | TR0 logic block diagram                                                                                                                                                                                                                                                       | 32 |

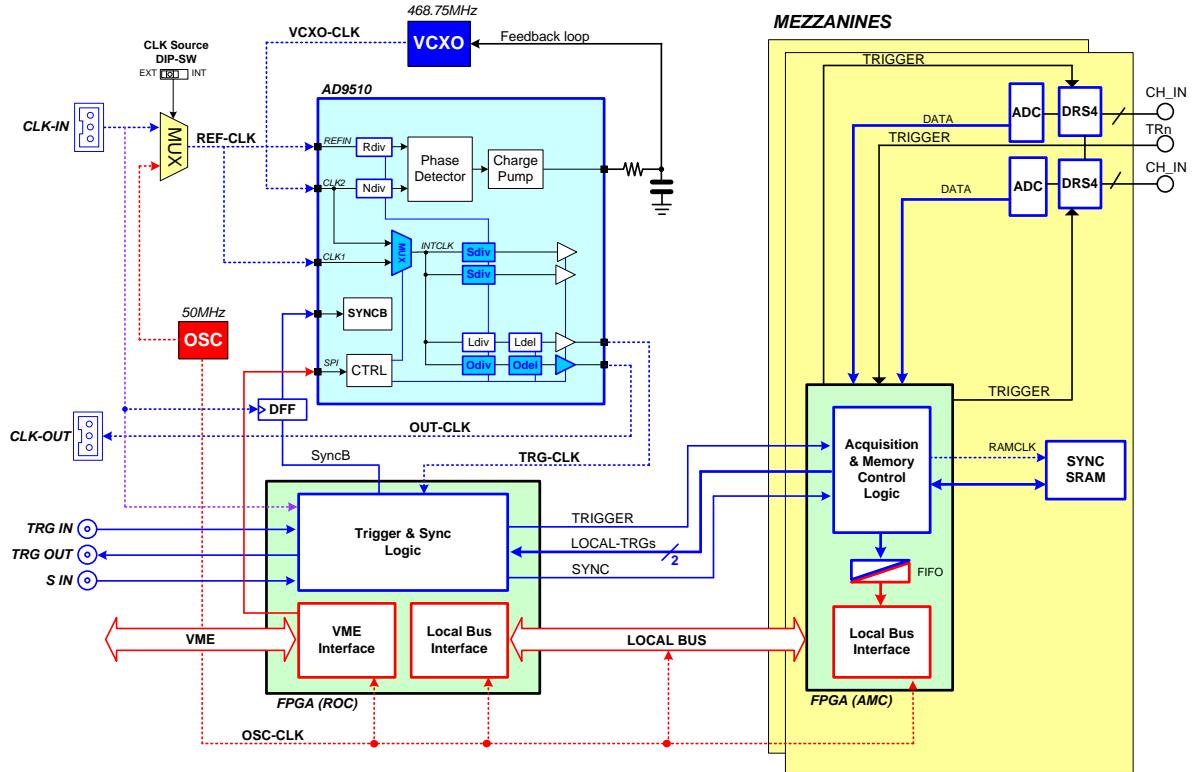

| <b>Fig. 9.4</b>  | Clock distribution diagram                                                                                                                                                                                                                                                    | 33 |

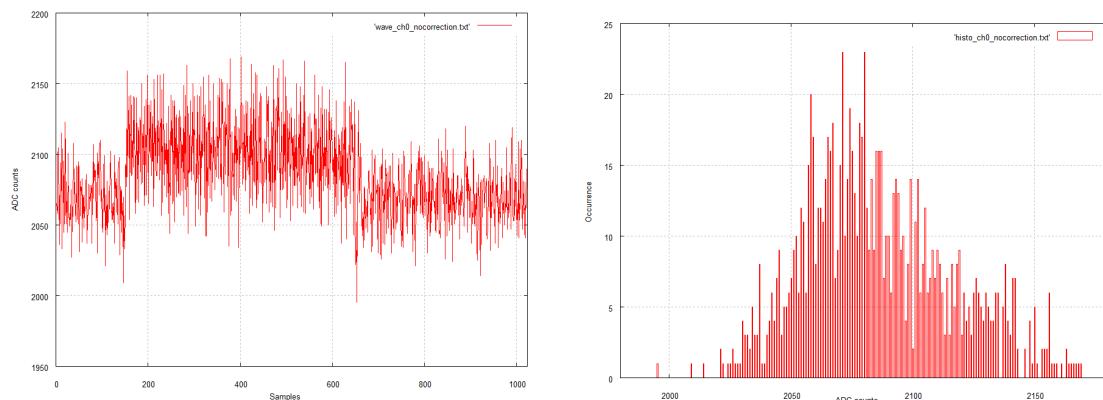

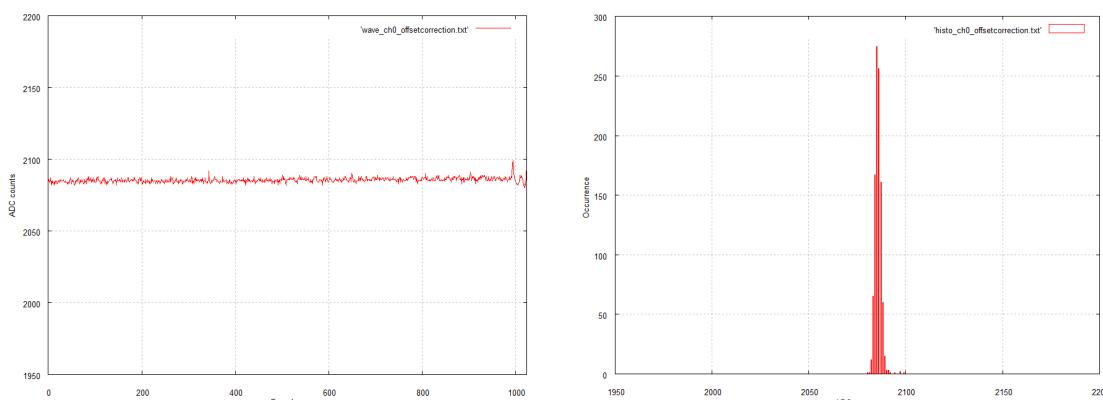

| <b>Fig. 9.5</b>  | Sampled waveform (left) and noise histogram (right) before cell index offset correction                                                                                                                                                                                       | 36 |

| <b>Fig. 9.6</b>  | Sampled waveform (left) and noise histogram (right) after cell index offset correction                                                                                                                                                                                        | 36 |

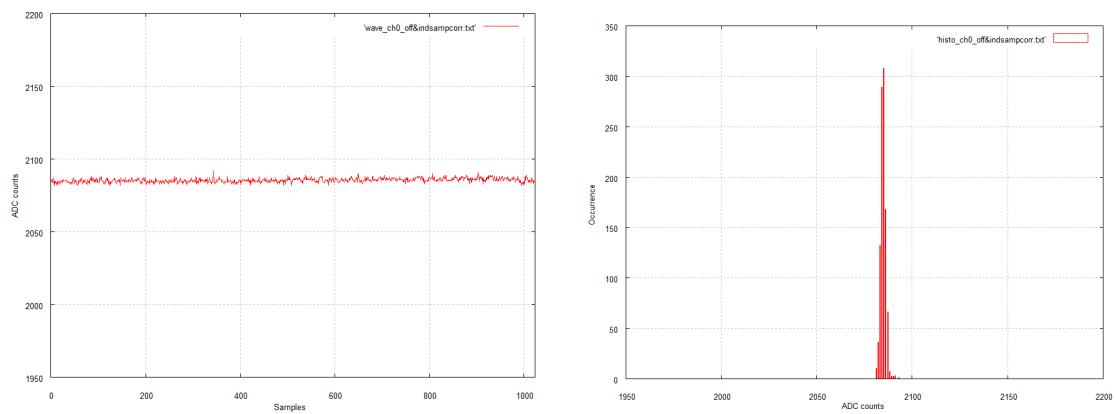

| <b>Fig. 9.7</b>  | Sampled waveform (left) and noise histogram (right) after sample index offset correction                                                                                                                                                                                      | 37 |

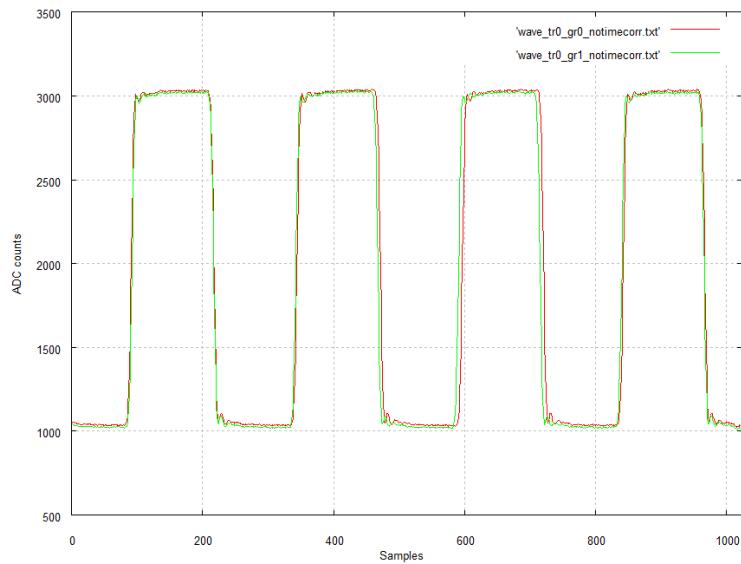

| <b>Fig. 9.8</b>  | Sampled TR0 signal in DRS4 chip for GR0 and GR1 before time correction                                                                                                                                                                                                        | 39 |

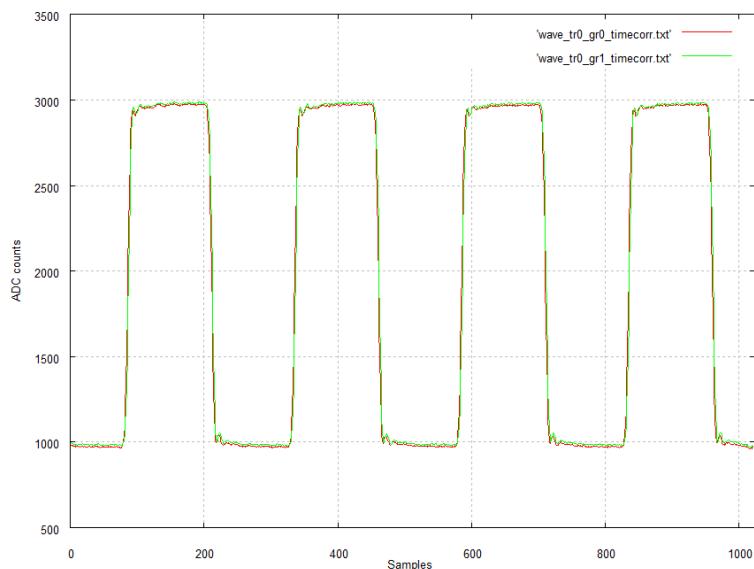

| <b>Fig. 9.9</b>  | Sampled TR0 signal in DRS4 chips for GR0 and GR1 after time correction                                                                                                                                                                                                        | 39 |

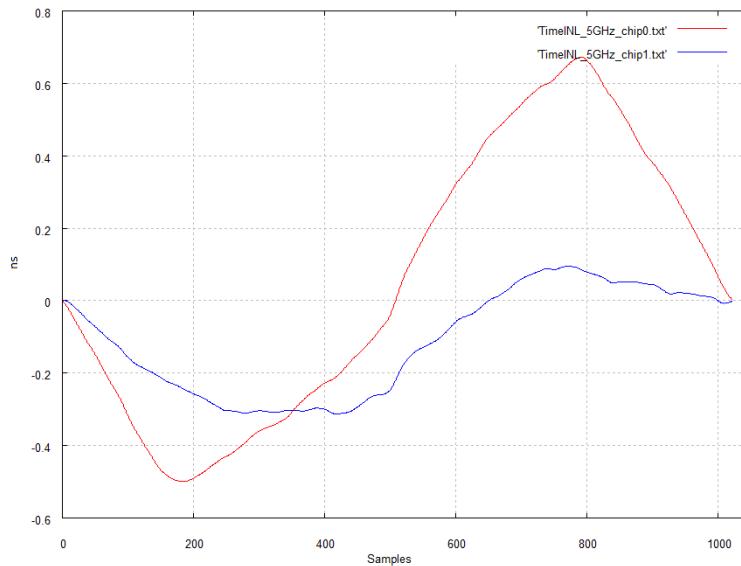

| <b>Fig. 9.10</b> | INL time profile of DRS4 chips for GR0 and GR1 before time correction                                                                                                                                                                                                         | 40 |

| <b>Fig. 9.11</b> | INL time profile of DRS4 chips for GR0 and GR1 after time correction                                                                                                                                                                                                          | 40 |

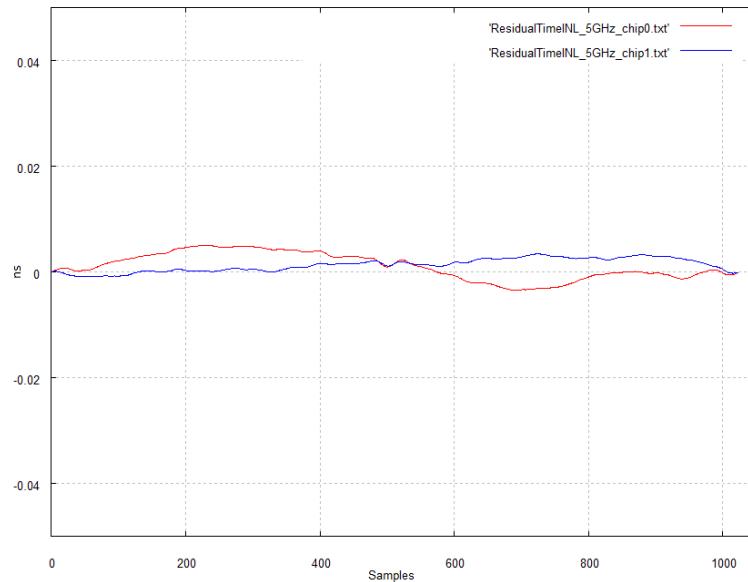

| <b>Fig. 9.12</b> | Event Format                                                                                                                                                                                                                                                                  | 42 |

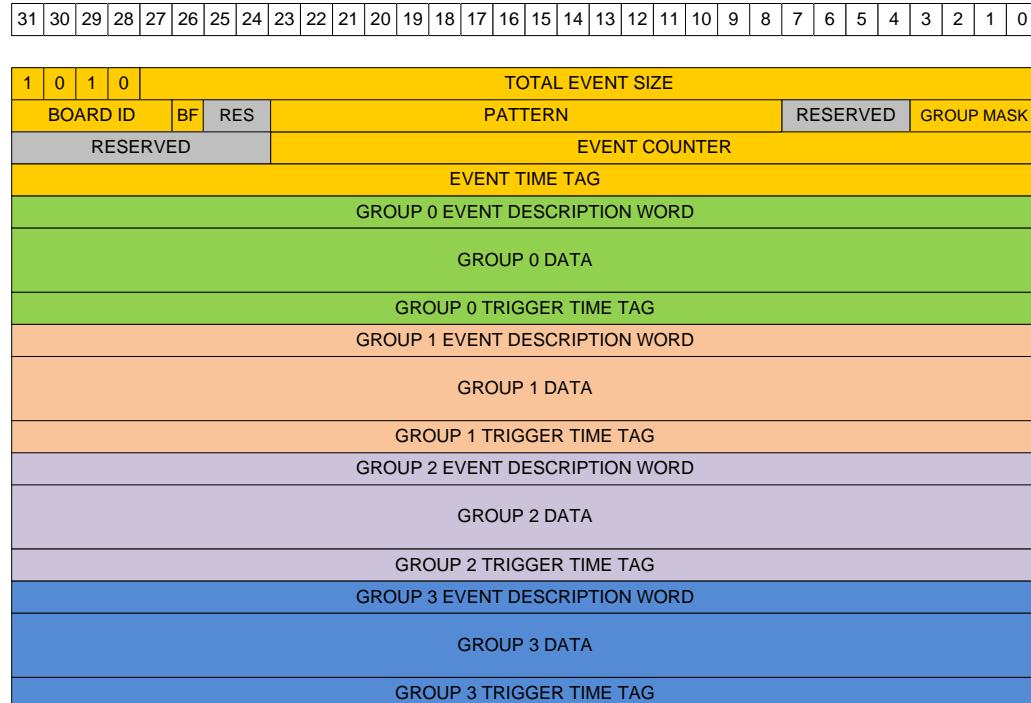

| <b>Fig. 9.13</b> | Group Data Format                                                                                                                                                                                                                                                             | 43 |

| <b>Fig. 9.14</b> | Block diagram of Trigger management                                                                                                                                                                                                                                           | 44 |

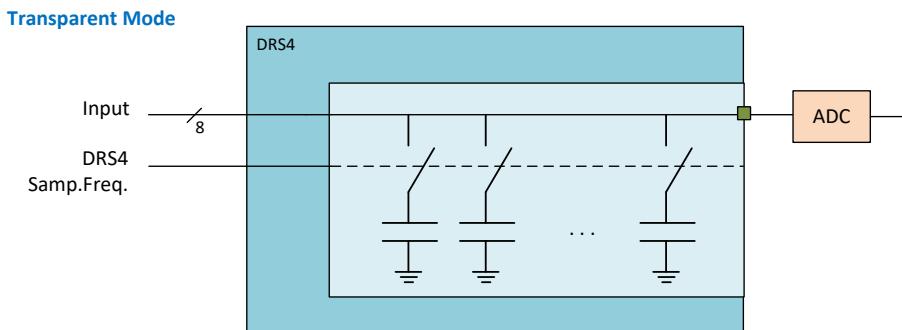

| <b>Fig. 9.15</b> | Diagram showing the “Transparent Mode” functioning. The analog input is both sampled by the DRS4 capacitors (analog sampling) and made available at the output for the ADC digital sampling at a smaller rate. The output stage is distorted with respect to the Output mode. | 47 |

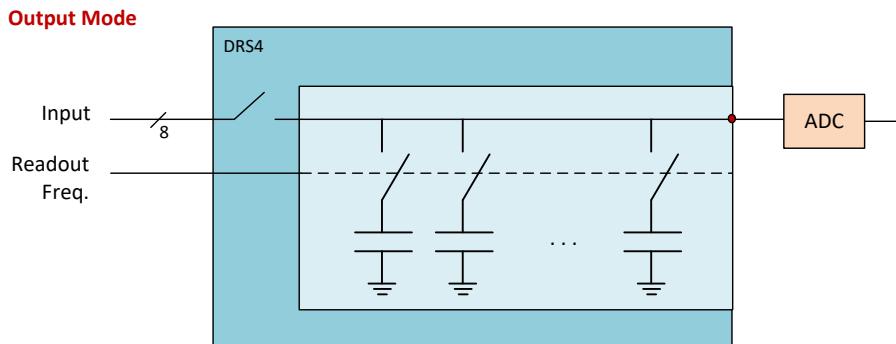

| <b>Fig. 9.16</b> | Diagram showing the “Output Mode” functioning. the input is no longer sampled and the capacitors hold the acquired samples and send them one at a time to the ADC at a frequency controlled by the FPGA (readout frequency). The output stage is correctly differential.      | 48 |

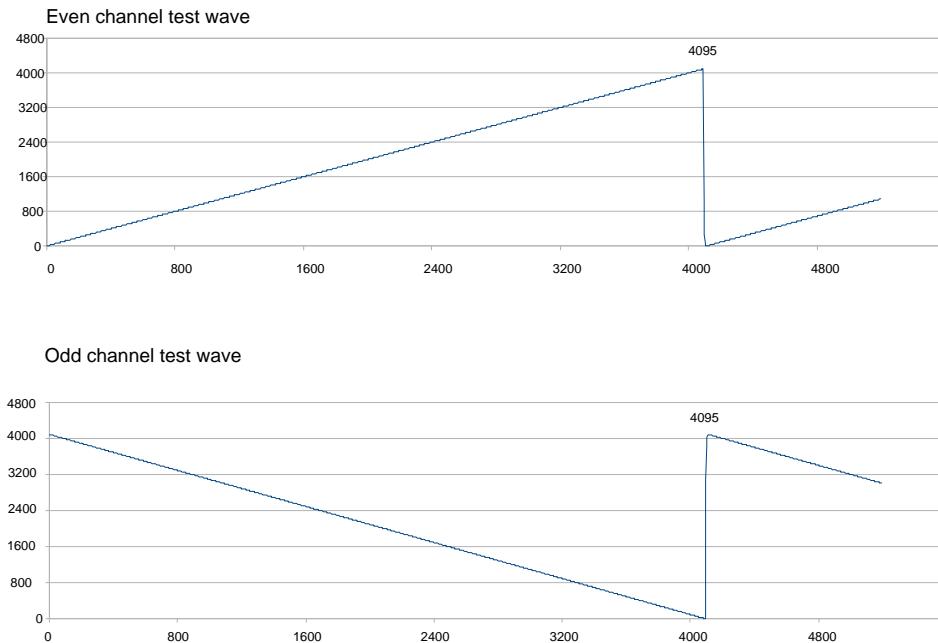

| <b>Fig. 9.17</b> | FPGA test waveform                                                                                                                                                                                                                                                            | 56 |

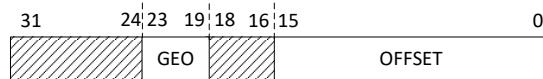

| <b>Fig. 9.18</b> | A24 addressing                                                                                                                                                                                                                                                                | 58 |

| <b>Fig. 9.19</b> | A32 addressing                                                                                                                                                                                                                                                                | 58 |

| <b>Fig. 9.20</b> | CR/CSR addressing                                                                                                                                                                                                                                                             | 59 |

| <b>Fig. 9.21</b> | Software relocation of base address                                                                                                                                                                                                                                           | 59 |

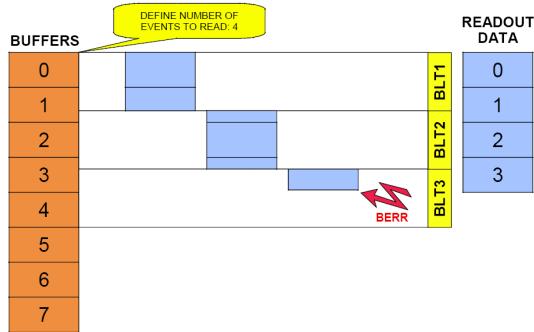

| <b>Fig. 9.22</b> | Example of BLT readout                                                                                                                                                                                                                                                        | 61 |

| <b>Fig. 10.1</b> | Drivers and software layers (the obsolete bridge models are not shown in the figure)                                                                                                                                                                                          | 66 |

| <b>Fig. 11.1</b> | CAEN Toolbox Graphical User Interface                                                                                                                                                                                                                                         | 67 |

| <b>Fig. 11.2</b> | CAENComm Demo Java™ and LabVIEW™ graphical interface                                                                                                                                                                                                                          | 68 |

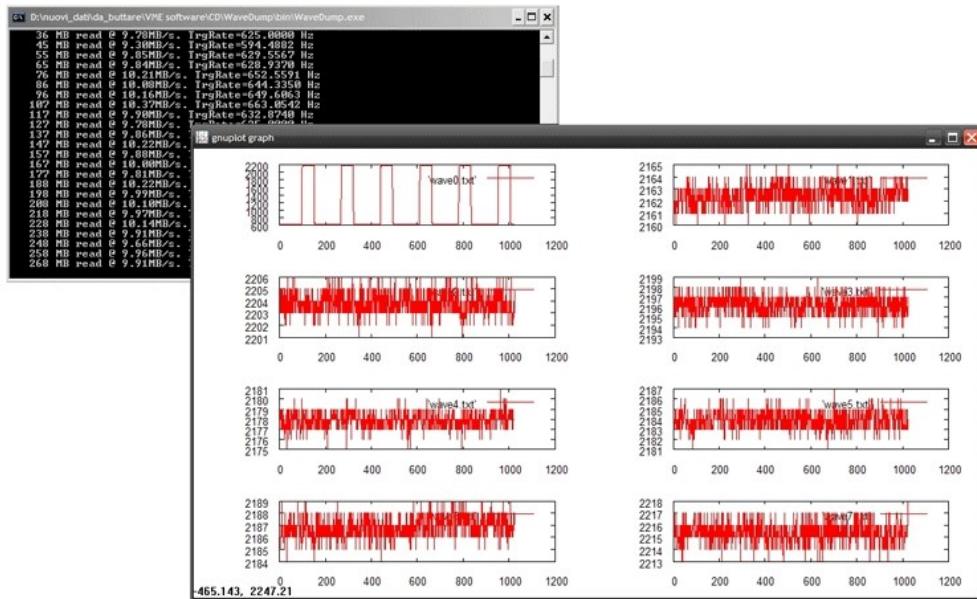

| <b>Fig. 11.3</b> | CAEN WaveDump                                                                                                                                                                                                                                                                 | 69 |

| <b>Fig. 12.1</b> | Front panel LEDs status at power-on                                                                                                                                                                                                                                           | 71 |

# List of Tables

|                 |                                                                                                                                                                          |    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Tab. 1.1</b> | Table of models and related items . . . . .                                                                                                                              | 15 |

| <b>Tab. 3.1</b> | Specification table . . . . .                                                                                                                                            | 18 |

| <b>Tab. 4.1</b> | Delivered kit content . . . . .                                                                                                                                          | 19 |

| <b>Tab. 6.1</b> | Power requirements table . . . . .                                                                                                                                       | 23 |

| <b>Tab. 9.1</b> | Examples of DC Offset and Trigger Threshold (in hexadecimal / decimal) for typical signals on TRn connector.<br>Values are valid for mezzanine PCB revision ≥ 1. . . . . | 46 |

| <b>Tab. 9.2</b> | Examples of DC Offset and Trigger Threshold (in hexadecimal / decimal) for typical signals on TRn connector.<br>Values are valid for mezzanine PCB revision 0. . . . .   | 46 |

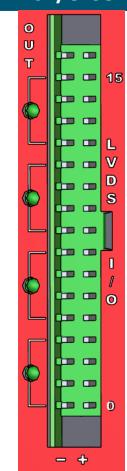

| <b>Tab. 9.3</b> | Functional description of the LVDS I/O signals for ROC FPGA firmware revisions < 3.8 . . . . .                                                                           | 52 |

| <b>Tab. 9.4</b> | Functional description of the LVDS I/O signals when configured as INPUT . . . . .                                                                                        | 53 |

| <b>Tab. 9.5</b> | Functional description of the LVDS I/O signals when configured as OUTPUT . . . . .                                                                                       | 53 |

| <b>Tab. 9.6</b> | Theoretical "average" trigger rate values for the Optical Link . . . . .                                                                                                 | 64 |

| <b>Tab. 9.7</b> | Theoretical "average" trigger rate values for the VME Link . . . . .                                                                                                     | 64 |

# Safety Notices

**N.B. Read carefully the “Precautions for Handling, Storage and Installation document provided with the product before starting any operation.**

The following HAZARD SYMBOLS may be reported on the unit:

|                                                                                     |                                   |

|-------------------------------------------------------------------------------------|-----------------------------------|

|    | Caution, refer to product manual  |

|    | Caution, risk of electrical shock |

|    | Protective conductor terminal     |

|    | Earth (Ground) Terminal           |

|   | Alternating Current               |

|  | Three-Phase Alternating Current   |

The following symbol may be reported in the present manual:

|                                                                                     |                           |

|-------------------------------------------------------------------------------------|---------------------------|

|  | General warning statement |

|-------------------------------------------------------------------------------------|---------------------------|

The symbol could be accompanied by the following terms:

- **DANGER:** indicates a hazardous situation which, if not avoided, will result in serious injury or death.

- **WARNING:** indicates a hazardous situation which, if not avoided, could result in death or serious injury.

- **CAUTION:** indicates a situation or condition which, if not avoided, could cause physical injury or damage the product and / or the surrounding environment.

## **GENERAL NOTICES:**

**CAUTION:** To avoid potential hazards

**USE THE PRODUCT ONLY AS SPECIFIED.

ONLY QUALIFIED PERSONNEL SHOULD PERFORM SERVICE

PROCEDURES**

**CAUTION:** Avoid Electric Overload

**TO AVOID ELECTRIC SHOCK OR FIRE HAZARD, DO NOT POWER A

LOAD OUTSIDE OF ITS SPECIFIED RANGE**

**CAUTION:** Avoid Electric Shock

**TO AVOID INJURY OR LOSS OF LIFE, DO NOT CONNECT OR

DISCONNECT CABLES WHILE THEY ARE CONNECTED TO A VOLTAGE

SOURCE**

**CAUTION:** Do Not Operate without Covers

**TO AVOID ELECTRIC SHOCK OR FIRE HAZARD, DO NOT OPERATE THIS

PRODUCT WITH COVERS OR PANELS REMOVED**

**CAUTION:** Do Not Operate in Wet/Damp Conditions

**TO AVOID ELECTRIC SHOCK, DO NOT OPERATE THIS PRODUCT IN

WET OR DAMP CONDITIONS**

**CAUTION:** Do Not Operate in an Explosive Atmosphere

**TO AVOID INJURY OR FIRE HAZARD, DO NOT OPERATE THIS

PRODUCT IN AN EXPLOSIVE ATMOSPHERE**

**THIS DEVICE SHOULD BE INSTALLED AND USED BY SKILLED

TECHNICIAN ONLY OR UNDER HIS SUPERVISION**

**DO NOT OPERATE WITH SUSPECTED FAILURES.

IF YOU SUSPECT THIS PRODUCT TO BE DAMAGED, PLEASE CONTACT

THE TECHNICAL SUPPORT**

See Chap. 17 for the Technical Support contacts.

### **VME NOTICES:**

**CAUTION:** This product needs proper cooling.

**USE ONLY CRATES WITH FORCED COOLING AIR FLOW SINCE

OVERHEATING MAY DEGRADE THE MODULE PERFORMANCES**

**V1742 DIGITIZERS CANNOT BE OPERATED WITH CAEN CRATES

VME8001, VME8002, VME8004, AND VME8004A. OVERHEAT MAY

DAMAGE THE MODULE**

**CAUTION:** This product needs proper handling.

**THE VME DIGITIZER DOES NOT SUPPORT LIVE INSERTION

(HOT-SWAP)

REMOVE OR INSERT THE BOARD WHEN THE CRATE IS POWERED OFF**

**ALL CABLES MUST BE REMOVED FROM THE FRONT PANEL BEFORE

EXTRACTING THE BOARD FROM THE CRATE**

# 1 Introduction

The Mod. V1742/VX1742 is a 1-unit wide VME 6U 32+2 Channel 12 bit 5 GS/s Switched Capacitor Digitizer based on the Switched Capacitor Array DRS4 (Domino Ring Sampler 4) chip<sup>1</sup>.

The default input dynamic range is 1 V<sub>pp</sub> (DC coupled) on single-ended MCX coaxial connectors with programmable DC Offset ( $\pm 1$  V range, controlled by a 16-bit DAC on each channel). The customization at 2 V<sub>pp</sub> of input range is available by ordering option.

The analog input signal is continuously sampled by the 1024 capacitive cells of the DRS4 in a circular way, at a frequency that is software selectable amongst 5 GHz, 2.5 GHz, 1GHz, and 750 MHz.

The analog to digital conversion is not simultaneous with the chip sampling phase, and it starts as soon as the trigger condition is met. When the trigger stops the DRS4 chip sampling (holding phase), the analog memory buffer is frozen, and the cell content is made available to the 12 bit ADC for the digital conversion. The digital memory allows the subsequent events to be stored, even if the readout is not yet started. Moreover, since the digital memory buffers work like FIFOs, the readout activity from VME or Optical Link does not affect write operations of subsequent events.

The chip functioning has two major consequences:

1. there is an unavoidable dead-time when the DRS4 chip stops its acquisition and the ADC converts the capacitances (110  $\mu$ s in case only the analog inputs are digitized, 181  $\mu$ s when also TRn are digitized).

2. the acquisition window is fixed to 1024 samples, that in case of 5 GHz corresponds to a maximum of about 200 ns. Refer to Sec. 9.2.

Moreover, the trigger processing introduces a latency between the trigger arrival and the DRS4 holding phase that varies according to the trigger source. The user must consider it when choosing the proper trigger source for its setup and the type of signal. Four possible trigger sources are available:

1. *Software Trigger*, common to all enabled groups, mainly intended for debug purposes. Refer to Sec. 9.9.1.

2. *External Trigger*, trigger on TRG-IN connector, common to all enabled groups. The external trigger latency makes this mode difficult to use at 5 GHz, while all other frequencies can be used with no problem. Refer to Sec. 9.9.2.

3. *Fast (Low Latency) Local Trigger*, trigger on TR0 and TR1 connectors, common to couples of 8-channels groups. This mode is called “Fast” or “Low Latency” since the trigger latency is reduced with respect to the external trigger. This trigger mode is convenient for high precision timing measurements, since the TRn can be digitized and reported in the output data to be used as time reference. Refer to Sec. 9.9.3.

4. *Self-trigger*, common to couples of 8-channels groups or to all channels of the board (*Global Trigger* mode). For each group is possible to select combinations of channels (logic OR) that provide a trigger whenever the input crosses the threshold. This *Self-trigger* mode cannot be used at 5 GHz due to the high trigger latency. Similarly, *Global trigger* mode introduces an additional latency, making it not recommended also at 2.5 GHz. Refer to Sec. 9.9.4 for additional details.

The module features the front panel CLK IN/CLK OUT connectors and an internal PLL for clock synthesis from internal/external references. V1742 supports multi-board synchronization allowing all DRS4s to be synchronized with a common clock source and ensuring Trigger Time Stamps alignment. Once synchronized, all data will be aligned and coherent across multiple V1742 boards.

By ordering options (see Tab. 1.1), the module is available with digital memory sizes of 128 event/ch or 1024 event/ch.

<sup>1</sup>Designed at Paul Scherrer Institute (PSI). Detailed documentation of the DRS4 chip is available at <http://drs.web.psi.ch/>

The VME interface of the module is VME64X compliant, and the data readout can be performed in several data transfer modes: BLT32, MBLT64 (up to 70 MB/s of transfer rate using CAEN Bridge), CBLT32/64, 2eVME, 2eSST (up to 200 MB/s of transfer rate). The built-in daisy chainable Optical Link, implementing CONET proprietary protocol, is able to transfer data at 80 MB/s, thus it is possible to connect up to 8 boards to a single A4818 Adapter, or up to 32 to a single A5818 Controller (4-link version, see **Tab. 1.1**).

| Board Models     |  | Description                                                                                  |

|------------------|--|----------------------------------------------------------------------------------------------|

| V1742            |  | 32+2 Ch. 12 bit 5 GS/s Switched-Capacitor Digitizer: 128 events/ch (1kS/events), EP3C16, SE  |

| V1742B           |  | 32+2 Ch. 12 bit 5 GS/s Switched-Capacitor Digitizer: 1024 events/ch (1kS/events), EP3C16, SE |

| VX1742           |  | 32+2 Ch. 12 bit 5 GS/s Switched-Capacitor Digitizer: 128 events/ch (1kS/events), EP3C16, SE  |

| VX1742B          |  | 32+2 Ch. 12 bit 5 GS/s Switched-Capacitor Digitizer: 1024 events/ch (1kS/events), EP3C16, SE |

| Personalizations |  | Description                                                                                  |

| VPERS1742        |  | x742 Customization with 2 V <sub>pp</sub> Input Range                                        |

| Related Products |  | Description                                                                                  |

| A4818            |  | A4818 – USB-3.0 to Optical Link                                                              |

| A5818            |  | A5818 - PCIe 4 Optical Link, Gen. 3                                                          |

| V3718            |  | V3718 – VME to USB2/CONET Bridge                                                             |

| VX3718           |  | VX3718 – VME to USB2/CONET Bridge                                                            |

| V4718            |  | V4718 – VME to USB 3.0/Ethernet/CONET Bridge                                                 |

| VX4718           |  | VX4718 – VME to USB 3.0/Ethernet/CONET Bridge                                                |

| VME8004B         |  | VME8004B - 2U 4 Slot VME64 Mini Crate                                                        |

| VME8004X         |  | VME8004X - 2U 4 Slot VME64X Mini Crate                                                       |

| VME8008B         |  | VME8008B - 4U 8 Slot VME64 Mini Crate                                                        |

| VME8008X         |  | VME8008X - 4U 8 Slot VME64X Mini Crate                                                       |

| VME8010          |  | VME8010 - 7U 21 Slot VME64 Low Cost Crate                                                    |

| VME8011          |  | VME8011 - 7U 21 Slot VME64 Low Cost Crate, pluggable power supply                            |

| VME8100          |  | VME8100 - 8U 21 Slot VME64/64X Enhanced Crate Series                                         |

| VME8200          |  | VME8200 - 9U 21 Slot VME64X Enhanced Crate series                                            |

| μ-Crate          |  | μ-Crate - Desktop single-slot VME64X Crate                                                   |

| NV8020A          |  | NV8020A - U CRATE VME/NIM 8 slot VME64 365W, 5 slot NIM 150W                                 |

| Accessories      |  | Description                                                                                  |

| A316             |  | A316 - Cable assembly 2.54mm 2-pin header female - 5 cm                                      |

| A317             |  | A317 - Cable assembly for Clock distribution 3-pin AMPMODU IV female terminations - 18 cm    |

| A317L            |  | A317L - Cable assembly for Clock distribution 3-pin AMPMODU IV female terminations - 25 cm   |

| DT4700           |  | Clock Generator and FAN-OUT                                                                  |

| A318             |  | Adapter for Clock signal FISCHER S101A004 male to 3-pin AMPMODU IV female - 10 cm            |

| A654             |  | Cable assembly LEMO 00 male to MCX male - 1 m                                                |

| A654 KIT4        |  | 4 Cable assembly LEMO 00 male to MCX male - 1 m                                              |

| A654 KIT8        |  | 8 Cable assembly LEMO 00 male to MCX male - 1 m                                              |

| A659             |  | Cable assembly BNC male to MCX male - 1 m                                                    |

| A659 KIT4        |  | 4 MCX TO BNC Cable Adapter                                                                   |

| A659 KIT8        |  | 8 MCX TO BNC Cable Adapter                                                                   |

| A952             |  | A952 - Cable assembly 2.54mm 34 pin female to 2.54mm 34 pin female - 50 cm                   |

| A953             |  | A953 - Cable assembly 2.54mm 34 pin female to two 2.54mm 34 pin female - 50 cm               |

| A954             |  | A954 - Cable assembly 2.54mm 34 pin female to two 2.54mm 16 pin female - 50 cm               |

| AI2740           |  | Optical Fibre 40 m simplex                                                                   |

| AI2730           |  | Optical Fibre 30 m simplex                                                                   |

| AI2720           |  | Optical Fibre 20 m simplex                                                                   |

| AI2705           |  | Optical Fibre 5 m simplex                                                                    |

| AI2703           |  | Optical Fibre 30 cm simplex                                                                  |

|        |                                           |

|--------|-------------------------------------------|

| AY2730 | Optical Fibre 30 m duplex                 |

| AY2720 | Optical Fibre 20 m duplex                 |

| AY2705 | Optical Fibre 5 m duplex (RoHS compliant) |

**Tab. 1.1:** Table of models and related items

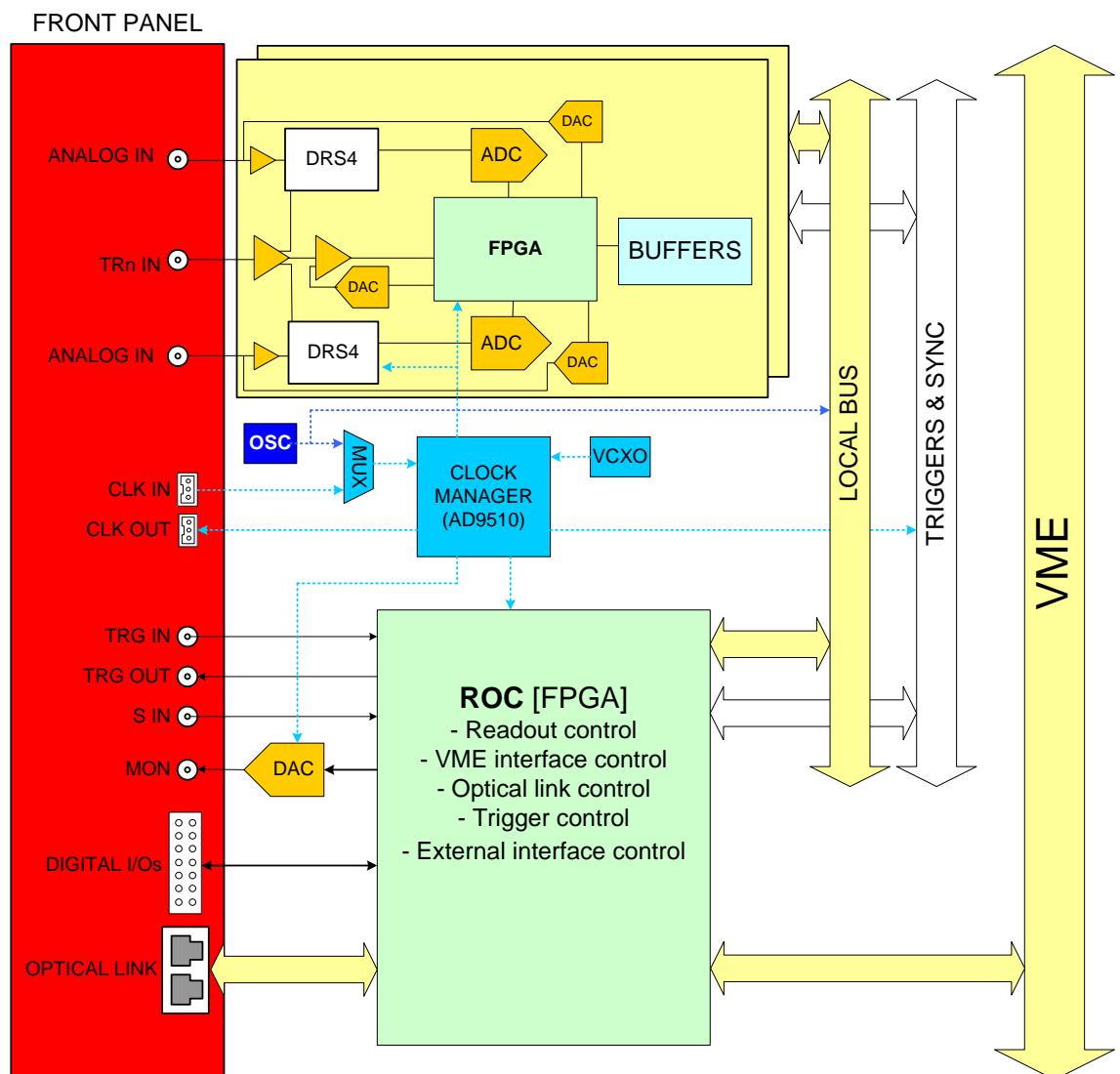

## 2 Block Diagram

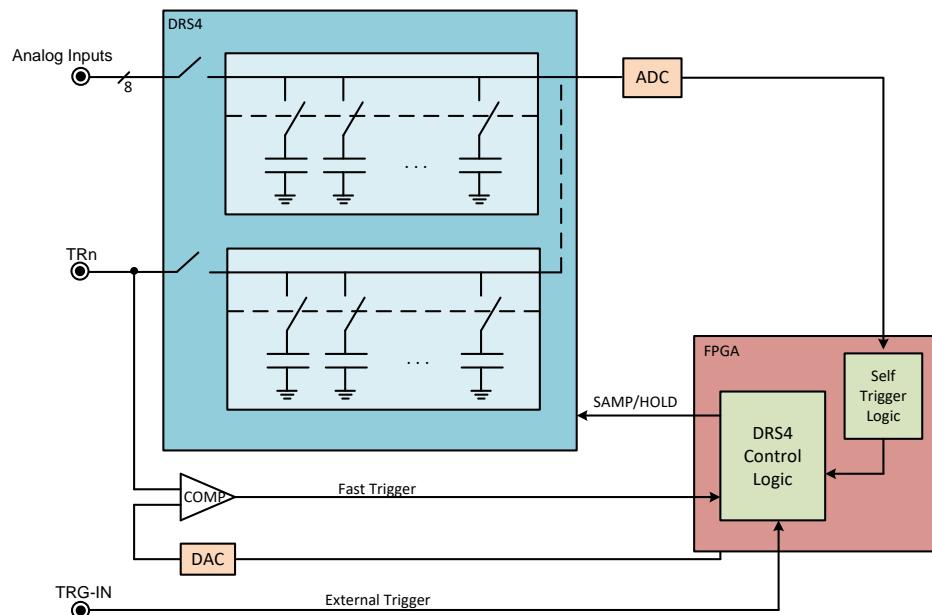

Fig. 2.1: Block Diagram

### 3 Technical Specifications

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                        |                                                                                                                                                        |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>ANALOG INPUTS</b>        | <p><b>Number of Channels</b><br/>32 channels<br/>2 special channels (TR0, TR1)<br/>Single ended</p> <p><b>Full Scale Range (FSR)</b><br/>1 V<sub>pp</sub> (default)<br/>2 V<sub>pp</sub> (by customization)</p> <p><b>Absolute Max Analog Input Voltage (for any DAC Offset)</b><br/>@1V<sub>pp</sub> = 3 V<sub>pp</sub> (with V<sub>rail</sub> max +3V or -3V)<br/>@2V<sub>pp</sub> = 6 V<sub>pp</sub> (with V<sub>rail</sub> max +6V or -6V)</p>                                                                                                  | <p><b>Impedance</b><br/><math>Z_{in} = 50 \Omega</math></p> <p><b>DC Offset</b><br/>Programmable 16-bit DAC for DC offset adjustment on each channel.<br/>Range: <math>\pm 1 \text{ V}</math></p>                      | <p><b>Connector</b><br/>MCX</p> <p><b>Bandwidth</b><br/>500 MHz</p>                                                                                    |

| <b>DIGITAL CONVERSION</b>   | <p><b>Resolution</b><br/>12 bits</p> <p><b>Switched Capacitor Array</b><br/>Domino Ring Sampler chip (DRS4), 8+1 channels with 1024 storage cells each</p>                                                                                                                                                                                                                                                                                                                                                                                          | <p><b>Sampling Rate</b><br/>5 GS/s - 2.5 GS/s - 1 GS/s - 0.75 GS/s SW selectable, simultaneously on each channel</p>                                                                                                   | <p><b>Dead Time (A/D Conversion)</b><br/>110 <math>\mu\text{s}</math>, analog inputs only<br/>181 <math>\mu\text{s}</math>, digitizing TR0 and TR1</p> |

| <b>FPGA</b>                 | Altera Cyclone EP3C16 (one FPGA manages 16+1 channels)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                        |                                                                                                                                                        |

| <b>TRIGGER</b>              | <p><b>Trigger Source</b></p> <ul style="list-style-type: none"> <li>- <i>Fast (Low Latency) trigger</i>: Programmable threshold on TR0 and TR1 (each TRn signal drives two 8-ch groups)</li> <li>- <i>Self-trigger</i>: Logic OR combination of channels over/under threshold (each channel self-trigger drives two 8-ch groups, or all 8-ch groups in case of <i>Global trigger mode</i>)</li> <li>- <i>External-trigger</i>: Common trigger by TRG-IN connector</li> <li>- <i>Software-trigger</i>: Common trigger by software command</li> </ul> | <p><b>Trigger Propagation</b><br/>TRG-OUT programmable digital output</p> <p><b>Trigger Time Stamp</b><br/>30-bit counter (extendable to 60-bit by sw)<br/>8.5 ns resolution<br/>9 s range<br/>Timer reset by S-IN</p> |                                                                                                                                                        |

| <b>ACQUISITION MEMORY</b>   | 128 events/ch or 1024 events/ch (1024 S/event) Multi-event Buffer<br>Independent read and write access; programmable event size and pre/post-trigger                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                        |                                                                                                                                                        |

| <b>ADC CLOCK GENERATION</b> | <p>Clock source: internal/external.</p> <p>On-board programmable PLL provides generation of the main board clocks from internal (50 MHz local Oscillator) or external (front panel CLK-IN connector) reference</p>                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                        |                                                                                                                                                        |

|                                 |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>DIGITAL I/O</b>              | <b>CLK-IN (AMP Modu II)</b><br>AC coupled differential input clock<br>LVDS, ECL, PECL, LVPECL, CML<br>(single ended NIM/TTL available by A318 adapter)<br>accuracy < 100 ppm requested                                                                                        | <b>TRG-IN (LEMO)</b><br>External trigger digital input NIM/TTL<br>Signal Width > 17 ns<br>$Z_{in} = 50 \Omega$                                                                                               | <b>S-IN (LEMO)</b><br>SYNC/START front panel digital input NIM/TTL<br>Signal Width > 17 ns<br>$Z_{in} = 50 \Omega$                                                                                                                                          |

|                                 | <b>CLK-OUT (AMP Modu II)</b><br>DC coupled differential LVDS clock output locked at ADC sampling clock                                                                                                                                                                        | <b>TRG-OUT (LEMO)</b><br>Trigger digital output NIM/TTL<br>$Z_{in} = 50 \Omega$                                                                                                                              | <b>LVDS I/O</b><br>16 general purpose LVDS I/O controlled by the FPGA: Busy, Data Ready, Memory full, Individual Trig-Out and other functions can be programmed.<br>An Input Pattern from the LVDS I/O can be associated to each trigger as an event marker |

| <b>SYNCHRONIZATION</b>          | <b>Clock Propagation</b><br><i>Daisy chain</i> : through CLK-IN/CLK-OUT connectors<br><i>One-to-many</i> : clock distribution from an external clock source to CLK-IN connector<br>Clock Cable delay compensation                                                             | <b>Acquisition Synchronization</b><br>Sync, Start/Stop through digital I/Os (S-IN or TRG-IN input / TRG-OUT output)                                                                                          | <b>Trigger Time Stamps Alignment</b><br>By S-IN input connector                                                                                                                                                                                             |

| <b>COMMUNICATION INTERFACES</b> | <b>Optical Link</b><br>CAEN CONET proprietary protocol<br>Up to 80 MB/s transfer rate<br>Daisy-chain capability                                                                                                                                                               | <b>Data Alignment</b><br>Busy/Veto management through digital I/Os (TRG-OUT/TRG-IN) or LVDS I/Os                                                                                                             | <b>VME</b><br>VME 64X compliant<br>Data transfer mode: BLT32, MBLT64 (70 MB/s by CAEN Bridge), CBLT32/64, 2eVME, 2eSST (200 MB/s)                                                                                                                           |

| <b>FIRMWARE</b>                 | <b>Waveform Recording Firmware</b><br>Free firmware for waveform recording                                                                                                                                                                                                    | <b>Upgrades</b><br>Supported via VMEbus/Optical Link                                                                                                                                                         |                                                                                                                                                                                                                                                             |

| <b>SOFTWARE</b>                 | <b>Readout SW</b><br><i>WaveDump</i> readout software with C source files and VS project for developers (Windows®, Linux®)                                                                                                                                                    | <b>Libraries and Tools</b><br>General purpose C libraries with readout demos (Windows®, Linux®, and LabVIEW™ support) and configuration tools                                                                |                                                                                                                                                                                                                                                             |

| <b>MECHANICAL</b>               | <b>Form Factor</b><br>1-unit wide VME64/VME64X boards                                                                                                                                                                                                                         | <b>Weight</b><br>520 g                                                                                                                                                                                       | <b>Dimension</b><br>6U x 160 mm                                                                                                                                                                                                                             |

| <b>ENVIRONMENTAL</b>            | <b>Environment:</b><br><b>Operating Temperature:</b><br><b>Storage Temperature:</b><br><b>Operating Humidity:</b><br><b>Storage Humidity:</b><br><b>Altitude:</b><br><b>Pollution Degree:</b><br><b>Overvoltage Category:</b><br><b>EMC Environment:</b><br><b>IP Degree:</b> | Indoor use<br>0°C to +40°C<br>-10°C to +60°C<br>10% to 90% RH non condensing<br>5% to 90% RH non condensing<br>< 2000m<br>2<br>II<br>Commercial and light industrial<br>IPX0 Enclosure, not for wet location |                                                                                                                                                                                                                                                             |

| <b>REGULATORY COMPLIANCE</b>    | <b>EMC</b><br>CE 2014/30/EU Electromagnetic compatibility Directive                                                                                                                                                                                                           | <b>Safety</b><br>CE 2014/35/EU Low Voltage Directive                                                                                                                                                         |                                                                                                                                                                                                                                                             |

| <b>POWER REQUIREMENTS</b>       | 5.5 A @ +5V<br>85 mA @ +12V                                                                                                                                                                                                                                                   |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                             |

**Tab. 3.1:** Specification table

## 4 Packaging and Compliancy

The V1742/VX1742 digitizer modules are available in 1-unit wide VME64/VME64X boards, EMC compliant.

The devices are inspected by CAEN before the shipment, and they are guaranteed to leave the factory free of mechanical or electrical defects.

The content of the delivered package standardly consists of the part list shown in the table below (**Tab. 4.1**).

| Part                                                                                | Description                                                             | Qt |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----|

|    | V1742/VX1742<br>32+2 Channel 12 bit 5 GS/s Switched Capacitor Digitizer | x1 |

|  | Documentation<br>UM4279 - V1742/VX1742 User Manual                      | -  |

**Tab. 4.1:** Delivered kit content

**CAUTION:** to manage the product, consult the operating instructions provided.

When receiving the unit, the user is strictly recommended to:

- Inspect containers for damage during shipment. Report any damage to the freight carrier for possible insurance claims.

- Check that all the components received match those listed on the enclosed packing list as in **Tab. 4.1**. (CAEN cannot accept responsibility for missing items unless any discrepancy is promptly notified.)

- Open shipping containers; be careful not to damage contents.

- Inspect contents and report any damage. The inspection should confirm that there is no exterior damage to the unit such as broken knobs or connectors and that the front panel is not scratched or cracked. Keep all packing material until the inspection has been completed.

- If damage is detected, file a claim with carrier immediately and notify CAEN service (see Chap. 17).

- If equipment must be returned, carefully repack equipment in the original shipping container with original packing materials, if possible. Please contact CAEN service.

- If equipment is not installed when unpacked, place equipment in original shipping container and store in a safe place until ready to install.

**DO NOT SUBJECT THE ITEM TO UNDUE SHOCK OR VIBRATIONS**

**DO NOT BUMP, DROP OR SLIDE SHIPPING CONTAINERS**

**DO NOT LEAVE ITEMS OR SHIPPING CONTAINERS UNSUPERVISED IN AREAS WHERE UNTRAINED PERSONNEL MAY MISHANDLE THE ITEMS**

**USE ONLY ACCESSORIES WHICH MEET THE MANUFACTURER SPECIFICATIONS**

For a correct and safe use of the module, refer to Chap. 6 and 7.

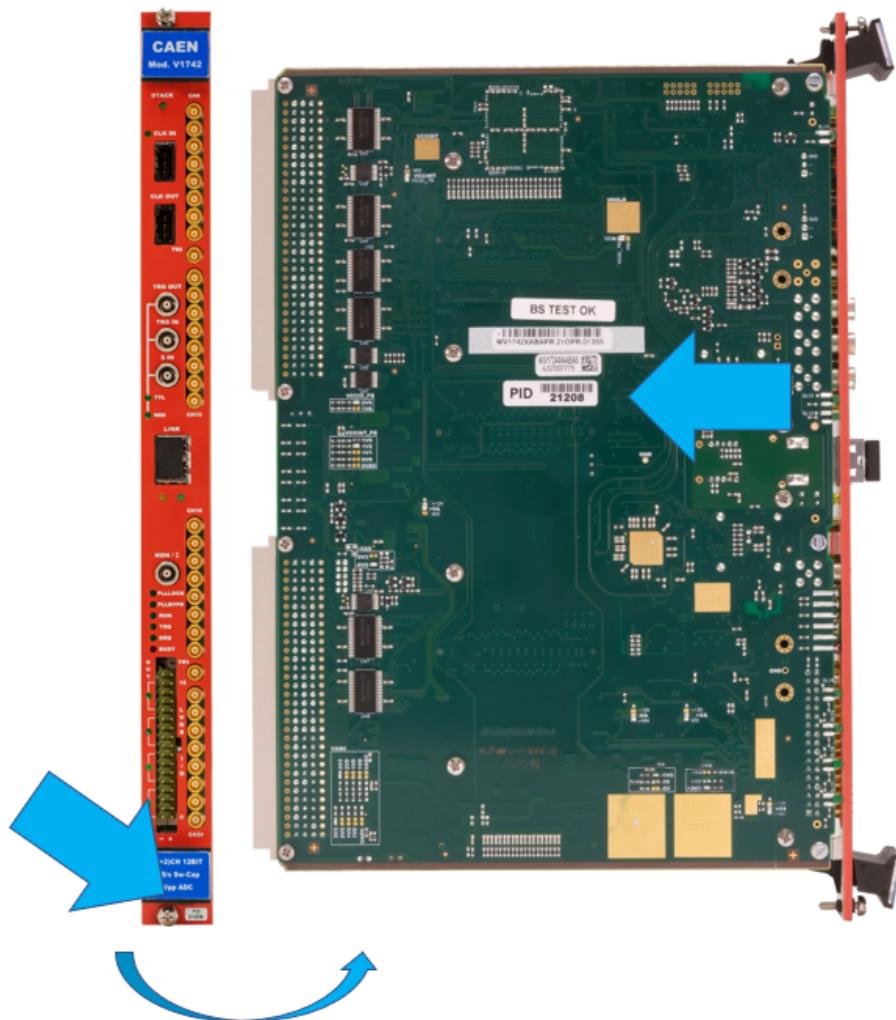

## 5 PID (Product Identifier)

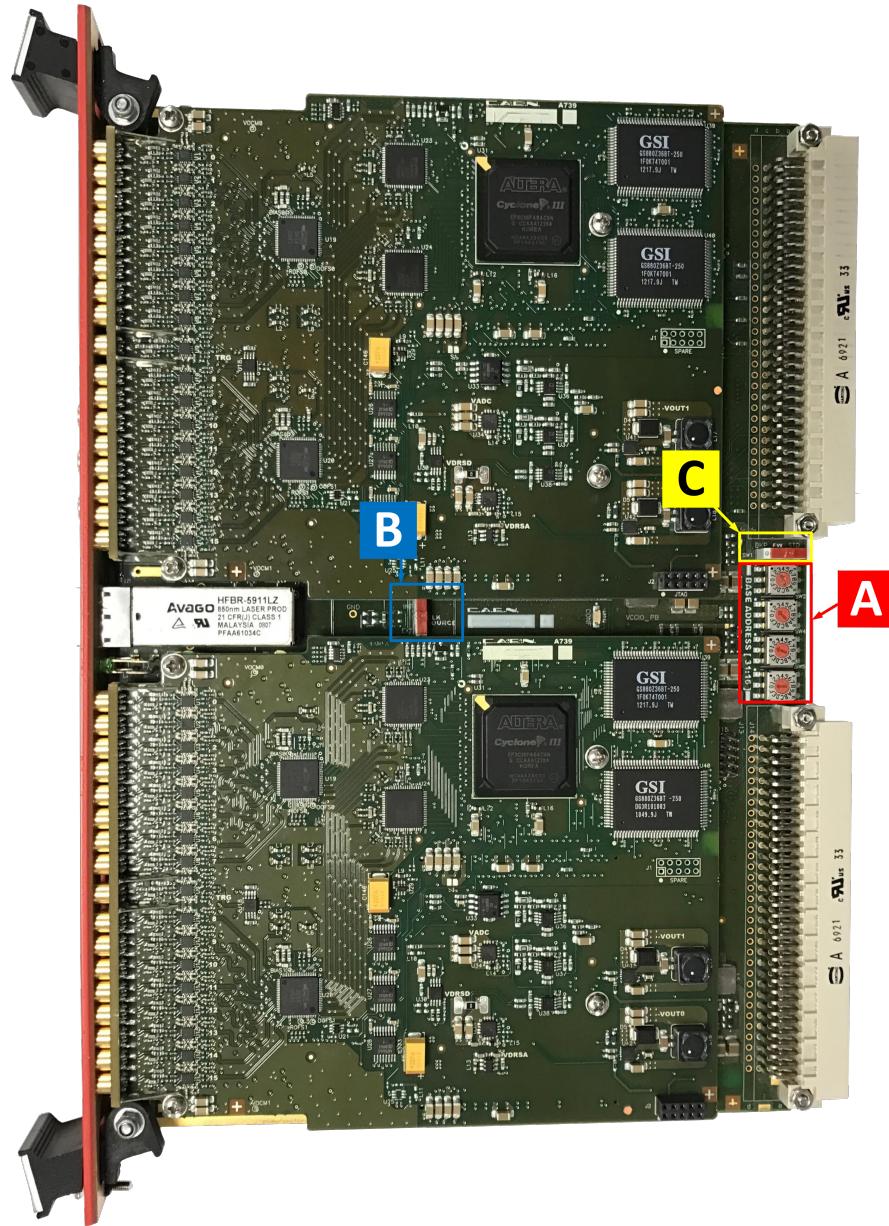

PID is the CAEN product identifier, an incremental number greater than 10000 that is unique for each product<sup>1</sup>. The PID is on a label affixed to the product (Fig. 5.2) and it is even stored in an on-board non-volatile memory readable at bits [7:0] of registers 0xF080 or 0xF084 [RD1]. The PID information is also available through CAENToolbox Software (for more details refer to [RD2]).

**Note:** The serial number is still valid to identify older boards, where the PID label is not present.

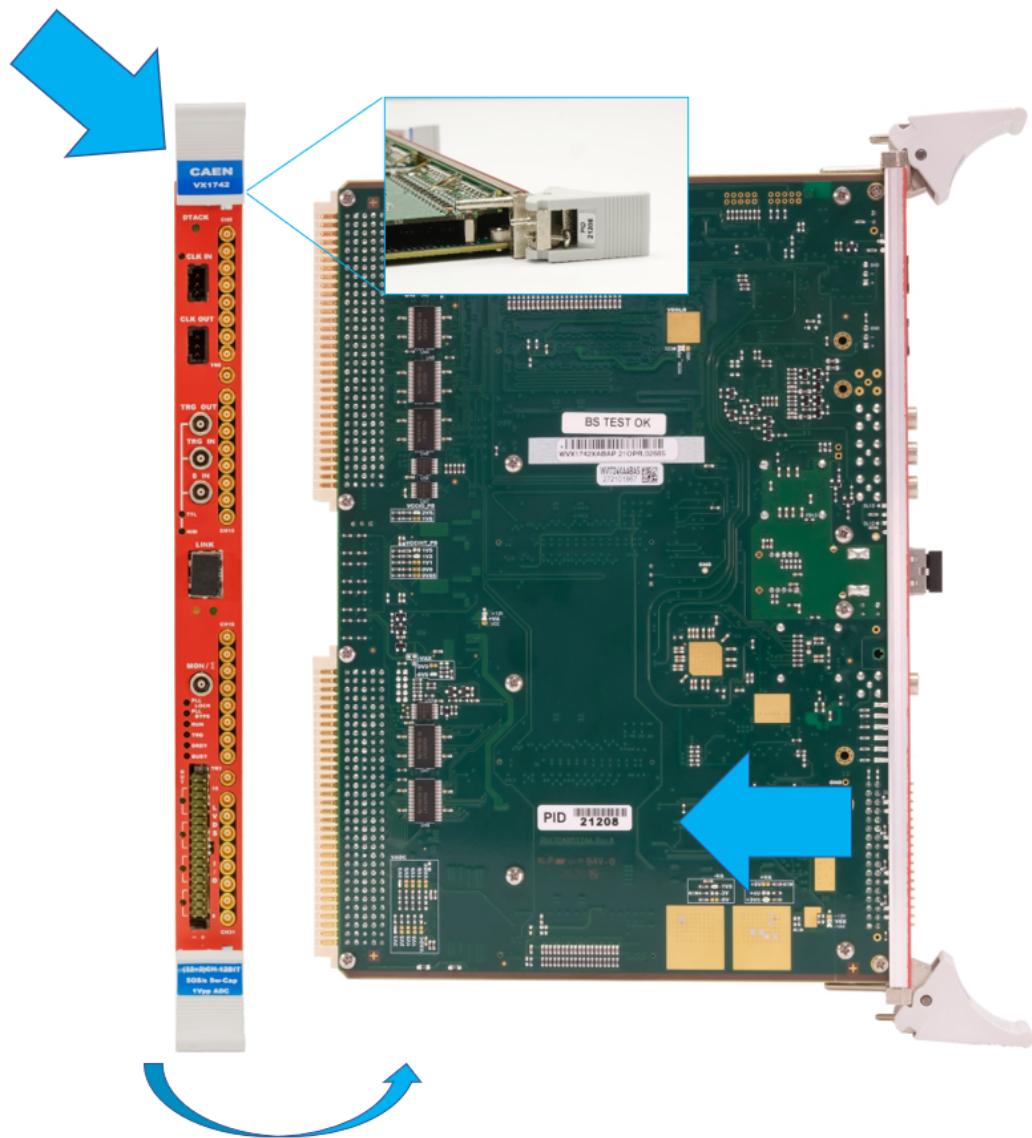

**Fig. 5.1:** PID location on V1742 (the number in the picture is purely indicative)

<sup>1</sup>The PID substitutes the serial number previously identifying the boards.

**Fig. 5.2:** PID location on VX1742 (the number in the picture is purely indicative)

## 6 Power Requirements

The table below resumes the V1742/VX1742 power consumptions per relevant power supply voltage.

| MODULE         | SUPPLY VOLTAGE |       |

|----------------|----------------|-------|

|                | +5 V           | +12 V |

| V1742/VX1742   | 5.5 A          | 85 mA |

| V1742B/VX1742B | 5.5 A          | 85 mA |

**Tab. 6.1:** Power requirements table

**Note:** The declared values are measured in standard operating conditions. In general, they could be subject to slight changes due to the firmware type, the firmware version, and the operating mode.

**Note:** The reported power requirements may be different depending on the motherboard revision numbers, which could be read at 0xF04C register. Please, contact CAEN for old power consumption specifications.

## 7 Cooling Management

The V1742/VX1742 Digitizers can operate in the temperature range  $0^{\circ} \div +40^{\circ}\text{C}$  [RD3].

The VME models must be operated in ventilated crates as recommended in the **Safety Notices**.

**EXTERNAL FANS MUST BE USED WHEN THE BOARD IS INSTALLED IN A SETUP WITH POOR AIR FLOW**

**V1742 DIGITIZERS CANNOT BE OPERATED WITH CAEN CRATES VME8001, VME8002, VME8004, AND VME8004A. OVERHEAT MAY DAMAGE THE MODULE**

The User must take care to provide a proper cooling to the board with external fan if the board is used in an enclosure or if the board is installed in a setup with poor air flow.

Excessive temperature will, in first instance, reduce the performance and the quality of the measurements and can also damage the board.

If the board is stored in cold environment, please check for water condensation before power on.

### 7.1 Cleaning Air Vents

CAEN recommends to occasionally clean the air vents on all vented sides of the board or crate, if present. Lint, dust, and other foreign matter can block the vents and limit the airflow. Be sure to power off the board and disconnect it from the power by physically detach the power chord before cleaning the air vents and follow the general cleaning safety precautions.

**IT IS UNDER THE RESPONSIBILITY OF THE CUSTOMER A NON-COMPLIANT USE OF THE PRODUCT**

## 8 Panels Description

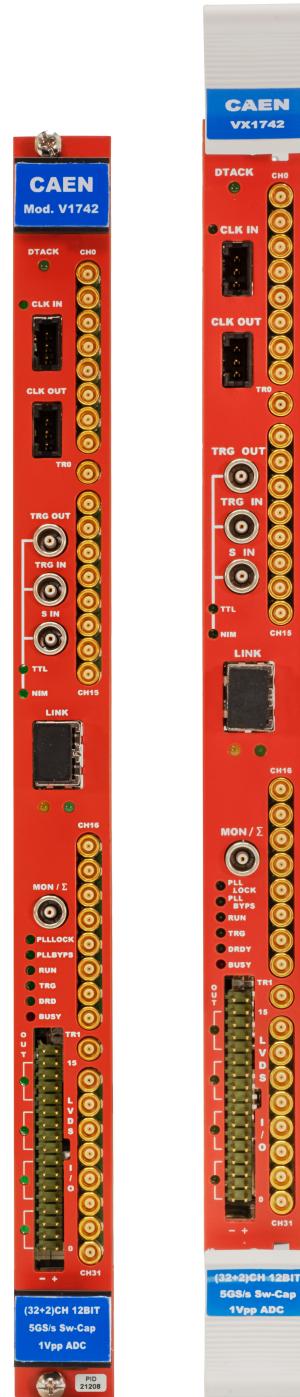

V1742 and VX1742 present the same front panel structure.

**Fig. 8.1:** Front panels view: V1742 on the left, VX1742 on the right

## 8.1 Front Panel

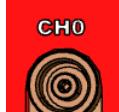

| ANALOG INPUT                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <p><b>DESCRIPTION</b><br/>Analog input connectors.</p> <p><b>FUNCTION</b><br/>CH[i] (i = 0 to 31) receives signals from the detector.<br/>TR[i] (i = 0 to 1) receives the fast (low latency) trigger, that can possibly be digitized.</p> <p><b>ELECTRICAL Specs</b><br/>Input dynamics:</p> <ul style="list-style-type: none"> <li>• 1 V<sub>pp</sub> (default) or 2 V<sub>pp</sub> (by customization) for CHO-CH31;</li> <li>• 2 V<sub>pp</sub> for TR0 and TR1 (PCB Rev <math>\geq 1</math>);</li> <li>• 3 V<sub>pp</sub> for TR0 and TR1 (PCB Rev = 0)</li> </ul> <p>Input impedance (<math>Z_{in}</math>): 50 <math>\Omega</math>.<br/>Absolute max analog input voltage (for any DAC offset in the single-ended configuration):</p> <ul style="list-style-type: none"> <li>• 3 V<sub>pp</sub> (with V<sub>rail</sub> max +3 V or -3 V) for 1V<sub>pp</sub> FSR</li> <li>• 6 V<sub>pp</sub> (with V<sub>rail</sub> max +6 V or -6 V) for 2V<sub>pp</sub> FSR</li> </ul> | <p><b>MECHANICAL Specs</b><br/>Series: MCX connectors.<br/>Type: CS 85MCX-50-0-16 (jack/female).<br/>Manufacturer: SUHNER<br/>Suggested plug/male: MCX-50-2-16.<br/>Suggested cable: RG174 type.</p> |

| CLOCK INPUT/CLOCK OUTPUT                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <p><b>DESCRIPTION</b><br/>Input and output clock connectors.</p> <p><b>FUNCTION</b><br/>CLK-IN accepts an external reference clock.<br/>CLK-OUT propagates the clock externally.<br/>CLK-IN and CLK-OUT can be used to daisy chain the clock in multi-board synchronization (A317 distribution cable available: see <b>Tab. 1.1</b>)</p> <p><b>ELECTRICAL Specs</b><br/>Signal Level:<br/>differential LVDS, ECL, PECL, LVPECL, CML.<br/>Single-ended-to-differential A318 cable adapter available for CLK-IN (see <b>Tab. 1.1</b>).<br/>Coupling:</p> <ul style="list-style-type: none"> <li>• AC (CLK-IN);</li> <li>• DC (CLK-OUT).</li> </ul> <p><math>Z_{diff}</math>: 100 <math>\Omega</math>.<br/>Accuracy &lt; 100 ppm.</p> | <p><b>MECHANICAL Specs</b><br/>Series: AMPMODU connectors.<br/>Type: 3-102203-4 (3-pin).<br/>Manufacturer: AMP Inc.</p> <p><b>PINOUT</b></p>  |

**CLK-IN LED (GREEN):** indicates that the external clock is enabled.

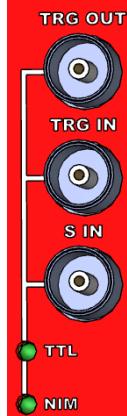

| TRIGGER INPUT/trigger output/SYNC INPUT                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <p><b>DESCRIPTION</b><br/>General purpose digital I/O connectors.</p> <p><b>FUNCTION</b></p> <ul style="list-style-type: none"> <li>• TRG-OUT: optionally provides out: <ul style="list-style-type: none"> <li>- probes from the mezzanines;</li> <li>- S-IN signal.</li> <li>- OR of the over-threshold signals from enabled channels</li> </ul> </li> <li>• TRG-IN: external trigger input.</li> <li>• S-IN: SYNC/START/STOP configurable input as reset of the time stamp (Sec. 9.13.3) or as acquisition start/stop (Sec. 9.8.1).</li> </ul> <p><b>ELECTRICAL Specs</b><br/>Signal Level: single-ended NIM/TTL, SW selectable.<br/>TRG-IN/S-IN input Signal Width: &gt; 17 ns (2 Trigger Clocks).<br/>TRG-IN/S-IN input impedance (<math>Z_{in}</math>): 50 Ω<br/>TRG-OUT requires 50 Ω termination.</p> <p><b>MECHANICAL Specs</b><br/>Series: 101 A 004 connectors.<br/>Type: DLP 101 A 004-28.<br/>Manufacturer: FISCHER.<br/><b>Alternatively:</b><br/>Type: EPL 00 250 NTN.<br/>Manufacturer: LEMO.</p> |

**TTL (GREEN), NIM (GREEN):** indicates the standard TTL or NIM set for TRG-OUT, TRG-IN, and S-IN.

| OPTICAL LINK PORT                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

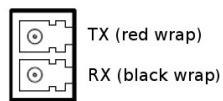

|  | <p><b>DESCRIPTION</b><br/>Optical link port.</p> <p><b>FUNCTION</b><br/>Data readout and flow control through optical link. Daisy chainable. Compliant with optical fibers 50/125 μm OM2 and OM3 (back-compliant with 62.5/125 μm OM1) featuring LC connectors on both sides.</p> <p><b>ELECTRICAL Specs</b><br/>Transfer rate: up to 80 MB/s.</p> <p><b>MECHANICAL Specs</b><br/>Series: SFF Transceivers.<br/>Type: FTLF8519F-2KNL (LC connectors).<br/>Manufacturer: FINISAR.</p> <p><b>PINOUT</b></p>  |

**LINK LEDs (GREEN/YELLOW):** right LED (GREEN) indicates the network presence, while left LED (YELLOW) indicates the data transfer activity

| ANALOG MONITOR                                                                      |                                                                                                   |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

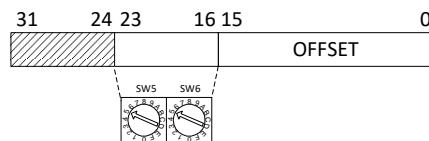

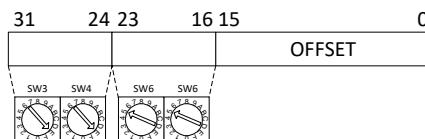

|  | <p><b>DESCRIPTION</b><br/>Analog Monitor LEMO connector</p> <p><b>FUNCTION</b><br/>(not used)</p> |