Rev. 5 - January 28th, 2025

# V4718/VX4718

VME to USB 3.0/Ethernet/Optical Link Bridge

# Purpose of this Manual

This document contains the full hardware description of the V4718/VX4718 VME-to-USB-3.0/Ethernet/Optical Link Bridge.

## Change Document Record

| Date                             | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 30 <sup>th</sup> , 2021   | 00       | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| October 18 <sup>th</sup> , 2021  | 01       | Updated Chap. 12 and 13. Introduced the new CAEN Linux driver usage for the USB connection. Changed the string to connect by USB in the Web Interface.                                                                                                                                                                                                                                                                                                        |

| January 3 <sup>rd</sup> , 2022   | 02       | Updated Sec. <b>First Access by USB</b>                                                                                                                                                                                                                                                                                                                                                                                                                       |

| August 30 <sup>th</sup> , 2022   | 03       | Corrected some bits in the register description                                                                                                                                                                                                                                                                                                                                                                                                               |

| December 13 <sup>th</sup> , 2022 | 04       | Updated Chap. 14. Add a note that specified that the USB connection is based on the IPv6 protocol.                                                                                                                                                                                                                                                                                                                                                            |

| January 28 <sup>th</sup> , 2025  | 05       | Added the register number to the Register Description chapter. Updated the descriptions for the <b>PULSE A WIDTH Register (Addr = 0X14)</b> , <b>PULSE B WIDTH Register (Addr = 0X1B)</b> , <b>SCALER FIFO OUT Register (Addr = 0x32)</b> , and <b>SCALER INSTANTANEOUS OUT Register (Addr = 0x31)</b> reflecting the new firmware changes. Fixed <b>OUT [3] MULTIPLEXER Register (Addr = 0X0A)</b> description. Updated <b>Chapter 16</b> with CAEN Toolbox. |

## Symbols, Abbreviated Terms and Notation

|     |                              |

|-----|------------------------------|

| OS  | Operative System             |

| PCI | Protocol Control Information |

| SoC | System on Chip               |

## Reference Documents

- [RD1] UM11111 – CAEN Toolbox User & Reference Manual

- [RD2] UM1934 - CAENComm User & Reference Manual

- [RD3] UM1935 - CAENDigitizer User & Reference Manual

- [RD4] UM7715 – CAENVMElib User & Reference Manual

- [RD5] UM4413 - A2818 Technical Information Manual

- [RD6] UM3121 - A3818 Technical Information Manual

- [RD7] AN2472 - CONET1 to CONET2 migration

- [RD8] DS7799 - A4818 USB 3.0 to CONET Adapter Datasheet

<https://www.caen.it/support-services/documentation-area/>

## Manufacturer Contacts

**CAEN S.p.A.**

Via Vетraia, 11 55049 Viareggio (LU) - ITALY

Tel. +39.0584.388.398 Fax +39.0584.388.959

[www.caen.it](http://www.caen.it) | [info@caen.it](mailto:info@caen.it)

© CAEN SpA – 2021

## Limitation of Responsibility

If the warnings contained in this manual are not followed, CAEN will not be responsible for damage caused by improper use of the device. The manufacturer declines all responsibility for damage resulting from failure to comply with the

instructions for use of the product. The equipment must be used as described in the user manual, with particular regard to the intended use, using only accessories as specified by the manufacturer. No modification or repair can be performed.

## Disclaimer

No part of this manual may be reproduced in any form or by any means, electronic, mechanical, recording, or otherwise, without the prior written permission of CAEN spa.

The information contained herein has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. CAEN spa reserves the right to modify its products specifications without giving any notice; for up to date information please visit [www.caen.it](http://www.caen.it).

## Made in Italy

We remark that all our boards have been designed and assembled in Italy. In a challenging environment where a competitive edge is often obtained at the cost of lower wages and declining working conditions, we proudly acknowledge that all those who participated in the production and distribution process of our devices were reasonably paid and worked in a safe environment (this is true for the boards marked "MADE IN ITALY", while we cannot guarantee for third-party manufactures).

# Index

|                                                       |           |

|-------------------------------------------------------|-----------|

| Purpose of this Manual.....                           | 1         |

| Change Document Record.....                           | 1         |

| Symbols, Abbreviated Terms and Notation .....         | 1         |

| Reference Documents .....                             | 1         |

| Manufacturer Contacts.....                            | 1         |

| Limitation of Responsibility.....                     | 1         |

| Disclaimer .....                                      | 2         |

| Made in Italy .....                                   | 2         |

| <b>Index.....</b>                                     | <b>3</b>  |

| <b>List of Figures .....</b>                          | <b>5</b>  |

| <b>List of Tables .....</b>                           | <b>5</b>  |

| <b>Safety Notices.....</b>                            | <b>7</b>  |

| <b>1   Introduction .....</b>                         | <b>8</b>  |

| <b>2   Block Diagram .....</b>                        | <b>9</b>  |

| <b>3   Technical Specifications.....</b>              | <b>10</b> |

| <b>4   Packaging and Compliance.....</b>              | <b>11</b> |

| <b>5   Panels Description.....</b>                    | <b>13</b> |

| Front Panel.....                                      | 14        |

| <b>6   Internal Components .....</b>                  | <b>16</b> |

| Switches.....                                         | 16        |

| Product Identification Number (PID) .....             | 17        |

| <b>7   VME Dataway Display .....</b>                  | <b>18</b> |

| <b>8   Programmable Inputs/Outputs .....</b>          | <b>19</b> |

| Timer & Pulse Generator.....                          | 19        |

| Scaler.....                                           | 20        |

| Coincidence .....                                     | 21        |

| Input/Output Register.....                            | 21        |

| <b>9   Optical Link, USB and Ethernet Layout.....</b> | <b>22</b> |

| USB.....                                              | 22        |

| Optical Link.....                                     | 22        |

| Ethernet .....                                        | 24        |

| <b>10   VME Interface .....</b>                       | <b>25</b> |

| VME Bus Requester.....                                | 25        |

| <b>Fair and Demand Request Modes .....</b>            | 25        |

| <b>VME Bus Release .....</b>                          | 26        |

| Addressing Capabilities.....                          | 26        |

| Data Transfer Capabilities .....                      | 26        |

| Interrupt Capabilities.....                           | 27        |

| <b>USB Link .....</b>                                 | 27        |

| <b>Ethernet Link .....</b>                            | 27        |

| <b>Optical Link .....</b>                             | 27        |

| Cycle Terminations.....                               | 27        |

| VME Bus First Slot Detector.....                      | 27        |

| System Controller Functions.....                      | 27        |

| <b>System Clock Driver .....</b>                      | 28        |

| <b>Arbitration Module .....</b>                       | 28        |

| Bus Timer .....                                       | 28        |

| IACK Daisy Chain Driver.....                          | 28        |

| VME64X Cycles.....                                    | 28        |

|                                                               |           |

|---------------------------------------------------------------|-----------|

| Internal Registers.....                                       | 29        |

| <b>STATUS Register (Addr = 0X00).....</b>                     | 30        |

| <b>CONTROL Register (Addr = 0X01) .....</b>                   | 30        |

| <b>FIRMWARE REVISION Register (Addr = 0X02).....</b>          | 31        |

| <b>IRQ STATUS Register (Addr = 0X05).....</b>                 | 31        |

| <b>IRQ MASK Register (Addr = 0X06) .....</b>                  | 31        |

| <b>I/O LEVEL SET Register (Addr = 0X07).....</b>              | 31        |

| <b>I/O POLARITY Register (Addr = 0X08).....</b>               | 32        |

| <b>OUT [2:0] MULTIPLEXER SET Register (Addr = 0X09) .....</b> | 32        |

| <b>OUT [3] MULTIPLEXER Register (Addr = 0X0A).....</b>        | 33        |

| <b>I/O STATUS READ Register (Addr = 0X0B).....</b>            | 33        |

| <b>I/O STATUS SET Register (Addr = 0X0C) .....</b>            | 33        |

| <b>I/O COINCIDENCE Register (Addr = 0X0D) .....</b>           | 33        |

| <b>PULSE A SETUP Register (Addr = 0X10).....</b>              | 34        |

| <b>PULSE A START Register (Addr = 0X11).....</b>              | 34        |

| <b>PULSE A CLEAR Register (Addr = 0X12).....</b>              | 34        |

| <b>PULSE A N CYCLE Register (Addr = 0X13) .....</b>           | 34        |

| <b>PULSE A WIDTH Register (Addr = 0X14) .....</b>             | 34        |

| <b>PULSE A DELAY Register (Addr = 0X15) .....</b>             | 35        |

| <b>PULSE A PERIOD Register (Addr = 0X16).....</b>             | 35        |

| <b>PULSE B SETUP Register (Addr = 0X17) .....</b>             | 35        |

| <b>PULSE B START Register (Addr = 0X18) .....</b>             | 35        |

| <b>PULSE B CLEAR Register (Addr = 0X19) .....</b>             | 35        |

| <b>PULSE B N CYCLE Register (Addr = 0X1A) .....</b>           | 35        |

| <b>PULSE B WIDTH Register (Addr = 0X1B) .....</b>             | 36        |

| <b>PULSE B DELAY Register (Addr = 0X1C) .....</b>             | 36        |

| <b>PULSE B PERIOD Register (Addr = 0X1D).....</b>             | 36        |

| <b>DISPLAY ADDRESS LOW Register (Addr = 0x20).....</b>        | 36        |

| <b>DISPLAY ADDRESS HIGH Register (Addr = 0x21) .....</b>      | 36        |

| <b>DISPLAY DATA LOW Register (Addr = 0x22).....</b>           | 36        |

| <b>DISPLAY DATA HIGH Register (Addr = 0x23).....</b>          | 36        |

| <b>SCALER SETUP Register (Addr = 0x2D).....</b>               | 37        |

| <b>SCALER MAXHITS Register (Addr = 0x2E) .....</b>            | 37        |

| <b>SCALER DWELL TIME Register (Addr = 0x2F) .....</b>         | 38        |

| <b>SCALER SW SETTINGS Register (Addr = 0x30) .....</b>        | 38        |

| <b>SCALER INSTANTANEOUS OUT Register (Addr = 0x31) .....</b>  | 38        |

| <b>SCALER FIFO OUT Register (Addr = 0x32) .....</b>           | 38        |

| <b>11 Hardware Installation .....</b>                         | <b>39</b> |

| Delivered Kit .....                                           | 39        |

| Ethernet Cable A-MCSP60020-R Assmann – 2 m .....              | 39        |

| Safety Notices .....                                          | 40        |

| Power-on.....                                                 | 41        |

| Power-on Status .....                                         | 41        |

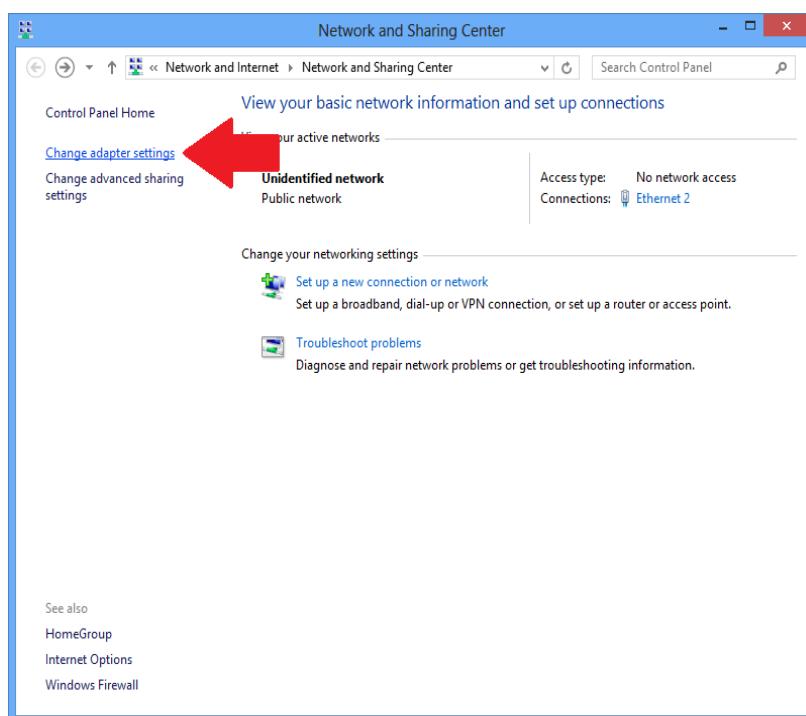

| <b>12 Hardware Detection .....</b>                            | <b>42</b> |

| Ethernet Configuration .....                                  | 42        |

| <b>Windows OS .....</b>                                       | 42        |

| <b>Linux OS.....</b>                                          | 44        |

| USB Configuration.....                                        | 46        |

| <b>Windows OS .....</b>                                       | 47        |

| <b>Linux OS.....</b>                                          | 47        |

| Optical Link Configuration .....                              | 47        |

| <b>Optical Link Drivers.....</b>                              | 48        |

| <b>13 Web Interface .....</b>                                 | <b>49</b> |

| First Access by USB .....                                     | 49        |

| First Access by Ethernet .....                                | 49        |

|                                       |           |

|---------------------------------------|-----------|

| Login .....                           | 50        |

| VME controller .....                  | 50        |

| Firmware update .....                 | 51        |

| <b>Upgrade Procedure</b> .....        | 51        |

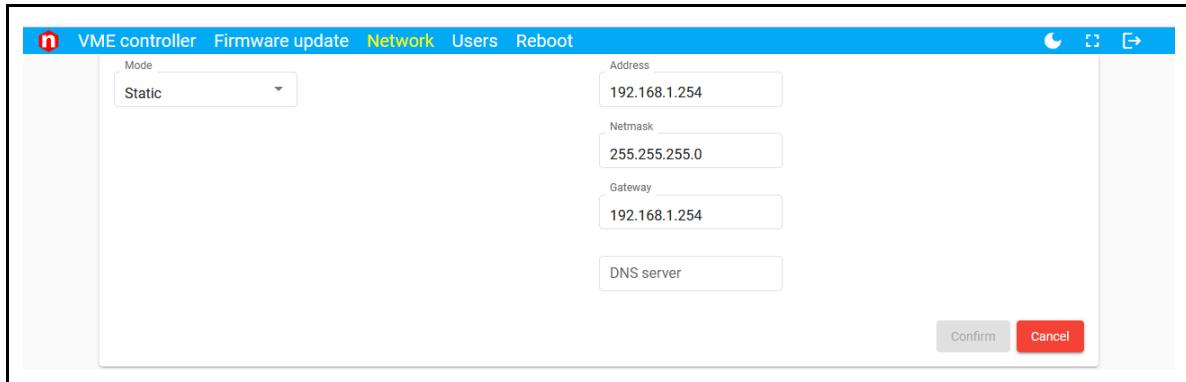

| Network .....                         | 52        |

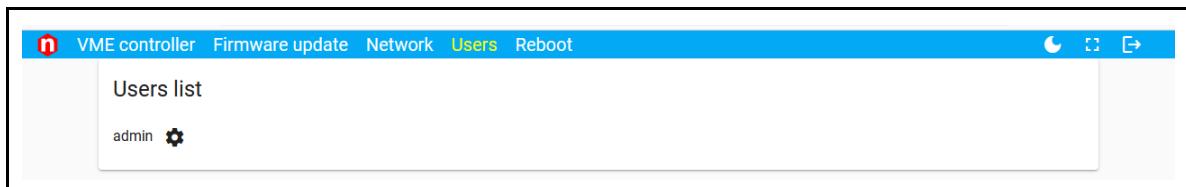

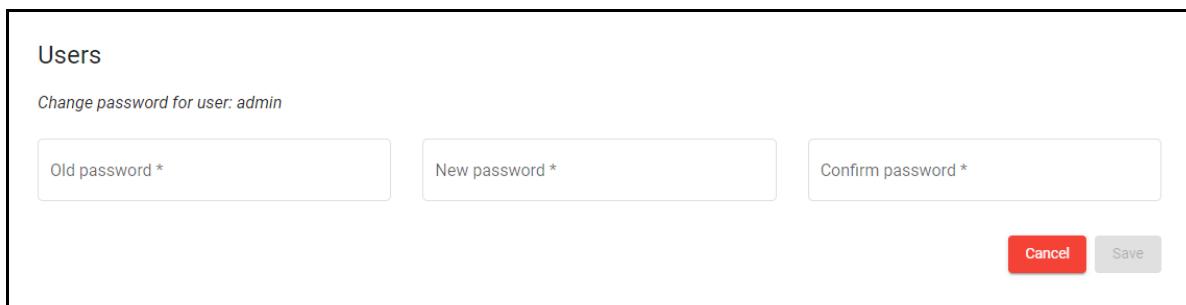

| Users .....                           | 52        |

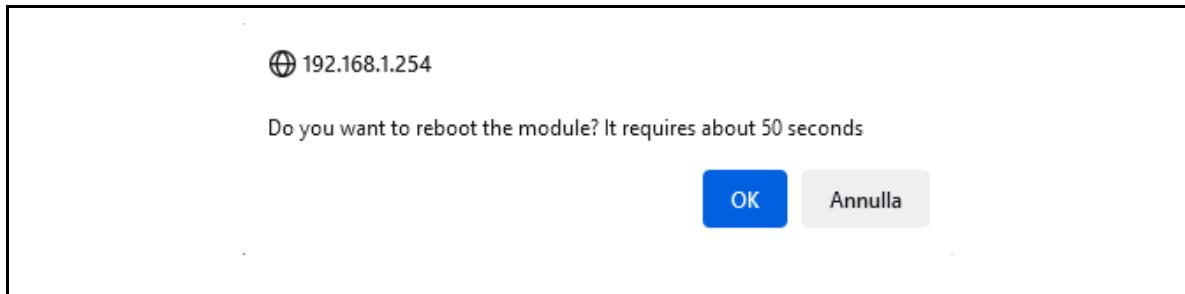

| Reboot .....                          | 52        |

| <b>14 Zynq UltraScale+ SoC</b> .....  | <b>54</b> |

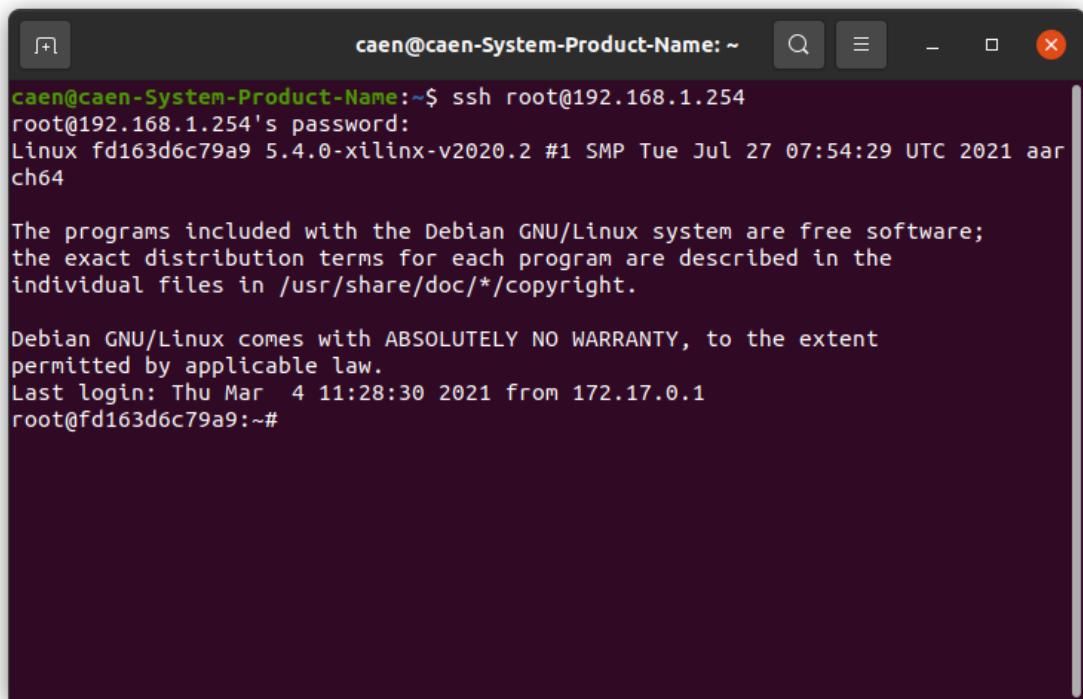

| How to Access the Embedded OS .....   | 54        |

| <b>Windows OS</b> .....               | 54        |

| <b>Linux OS</b> .....                 | 56        |

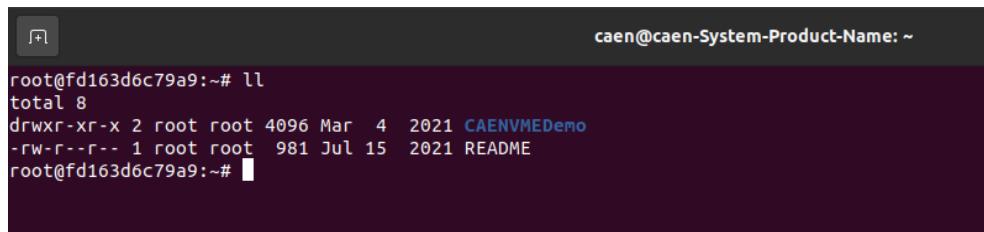

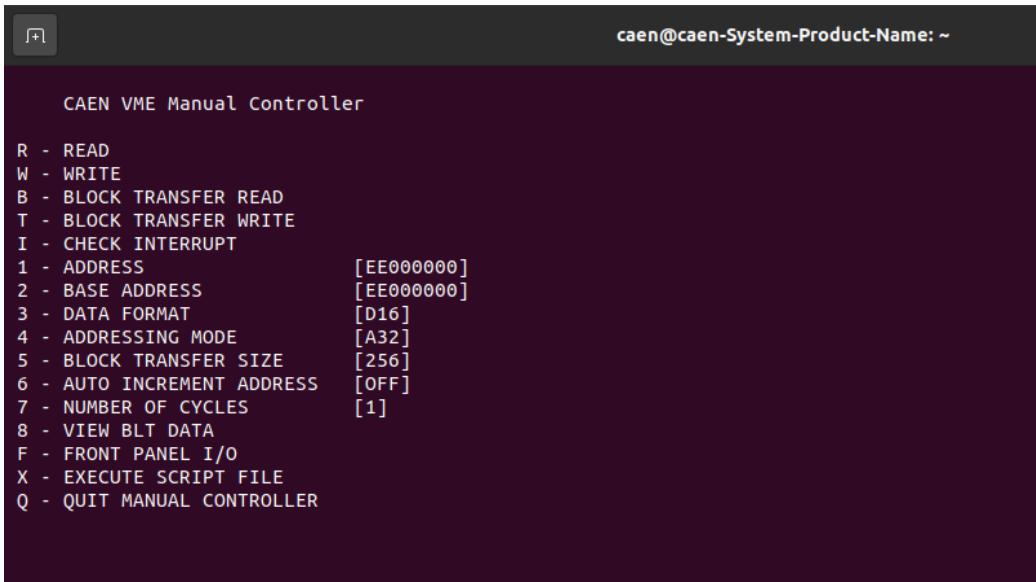

| CAENVMEDemo .....                     | 57        |

| <b>15 Software</b> .....              | <b>60</b> |

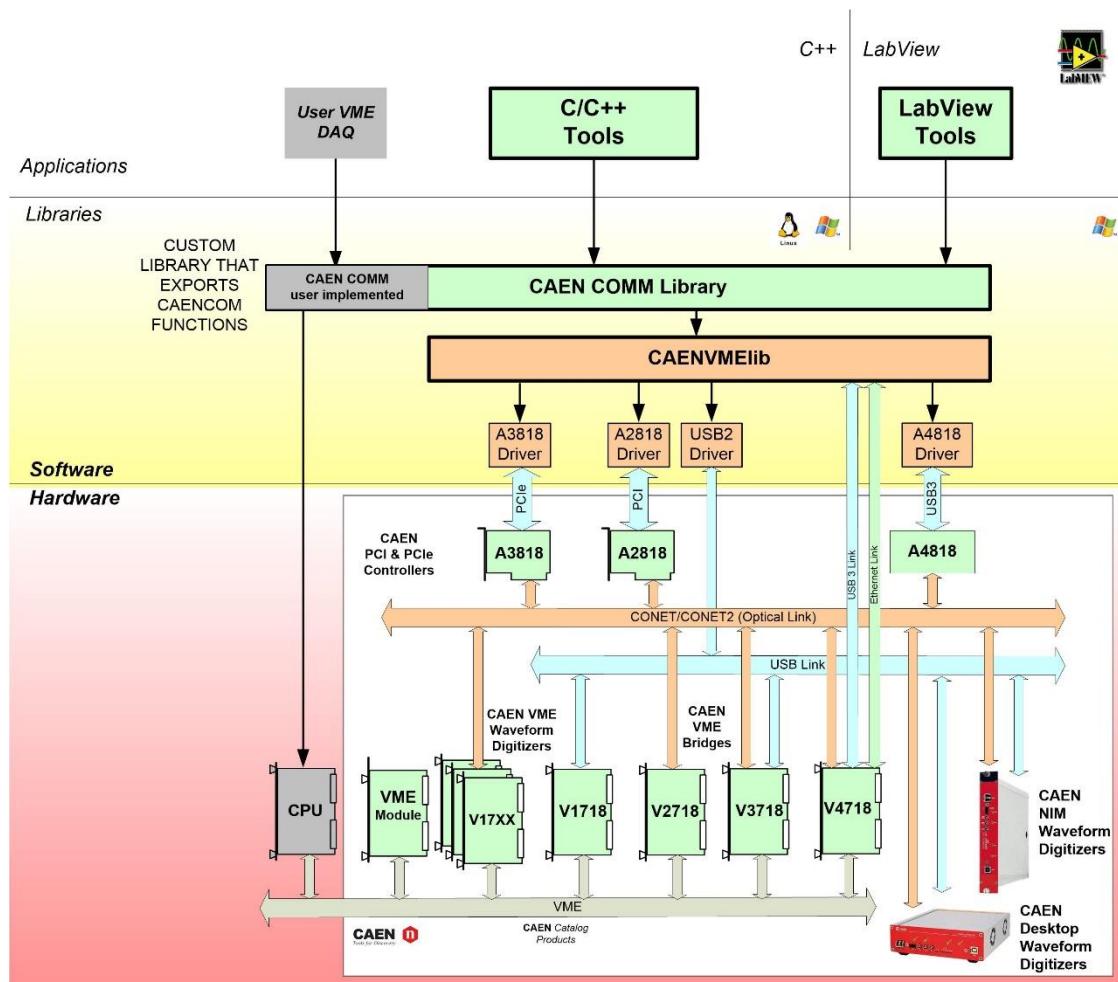

| VMELib Library .....                  | 60        |

| CAEN Toolbox .....                    | 61        |

| <b>16 Firmware and Upgrades</b> ..... | <b>62</b> |

| Firmware File .....                   | 62        |

| Firmware Upgrade .....                | 63        |

| Troubleshooting .....                 | 63        |

| <b>17 Technical Support</b> .....     | <b>65</b> |

## List of Figures

|                                                                                                                                                                                   |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.1: Simplified block diagram .....                                                                                                                                          | 9  |

| Fig. 4.1: Module views .....                                                                                                                                                      | 11 |

| Fig. 5.1: Front panel .....                                                                                                                                                       | 13 |

| Fig. 6.1: Internal components .....                                                                                                                                               | 16 |

| Fig. 6.2: PID label .....                                                                                                                                                         | 17 |

| Fig. 6.3: PID location .....                                                                                                                                                      | 17 |

| Fig. 7.1: Dataway display layout .....                                                                                                                                            | 18 |

| Fig. 8.1: Timer & Pulser Generator main parameters .....                                                                                                                          | 19 |

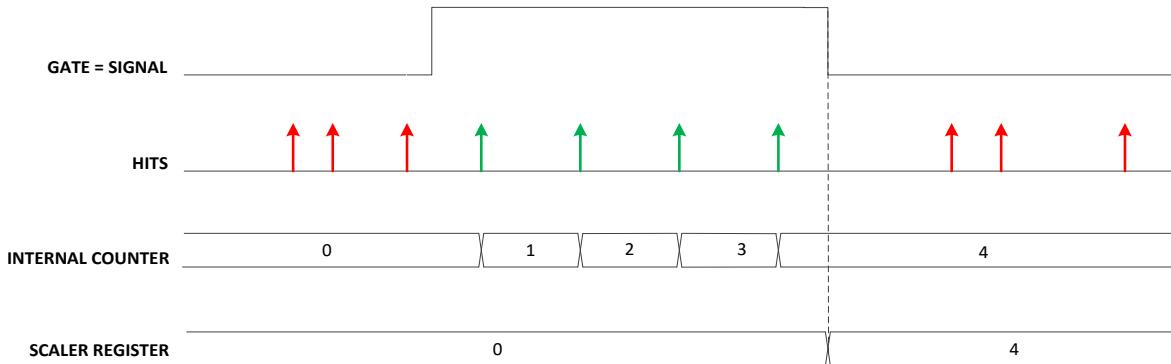

| Fig. 8.2: Gate mode example. The gate is a given signal and only the hits within the gate (in green) are counted .....                                                            | 20 |

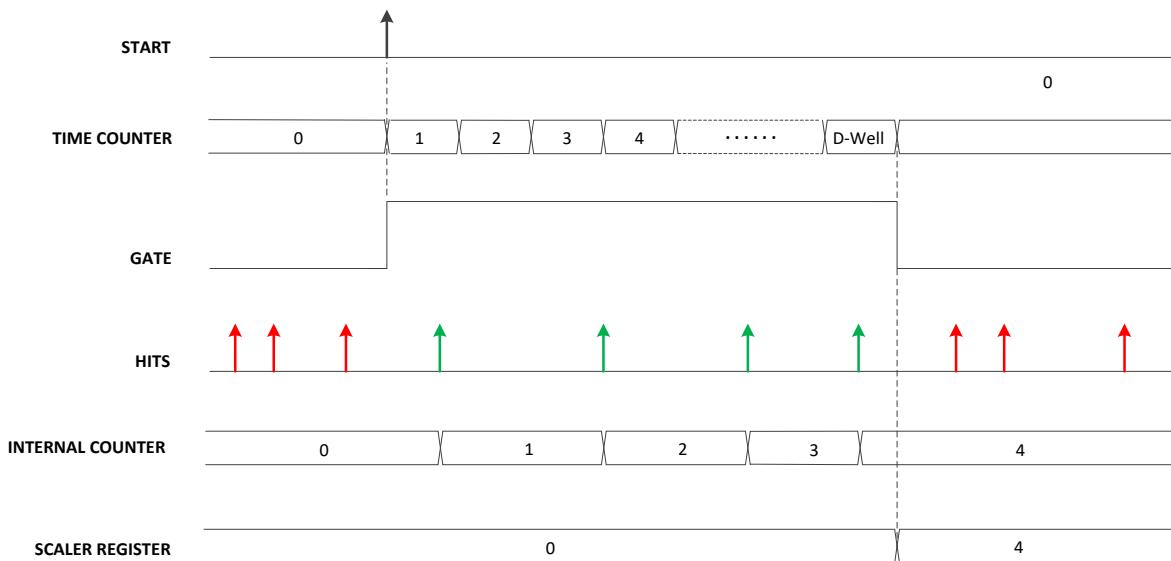

| Fig. 8.3: D-Well mode example. Upon the start signal, the time counter starts counting the hits until the preset D-Well time is reached. Not counted hits are marked in red ..... | 20 |

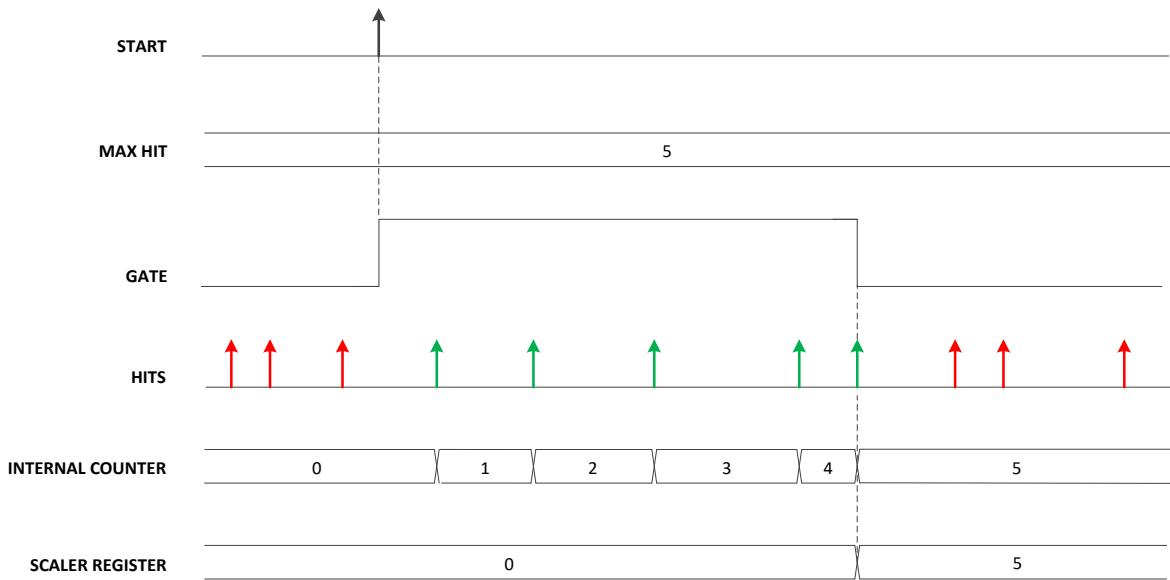

| Fig. 8.4: MaxHit mode example. Upon the start signal, only a programmable maximum number of hits are counted .....                                                                | 21 |

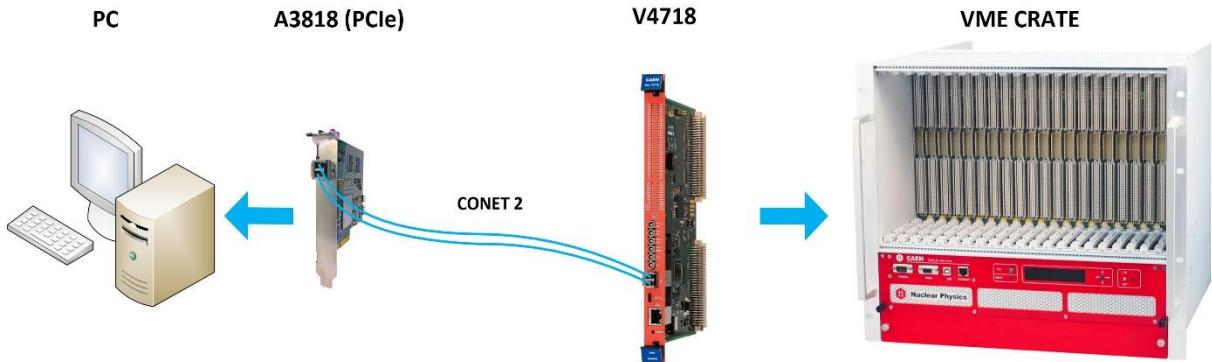

| Fig. 9.1: Example of USB layout .....                                                                                                                                             | 22 |

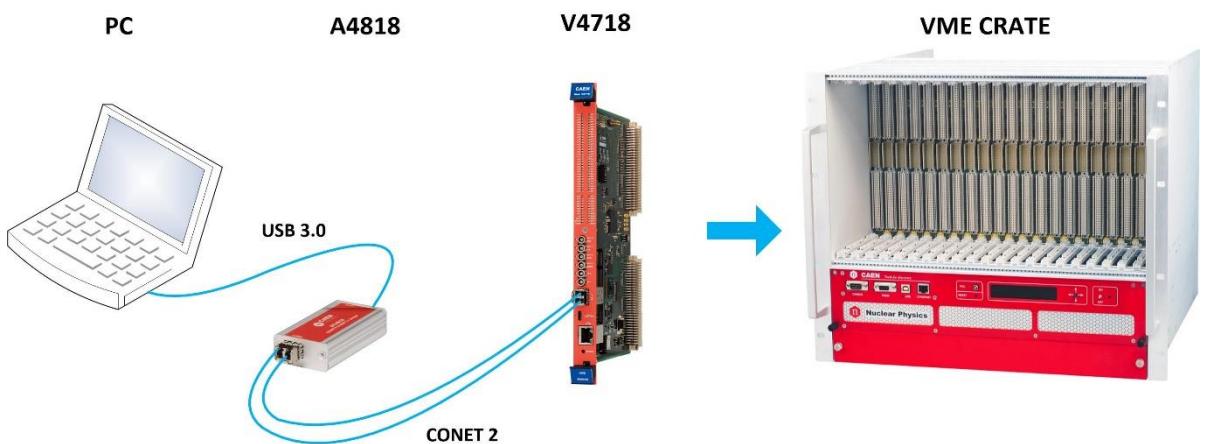

| Fig. 9.2: Example of Optical Link setup through A3818 (or A2818) .....                                                                                                            | 23 |

| Fig. 9.3: Example of Optical Link setup through A4818 .....                                                                                                                       | 23 |

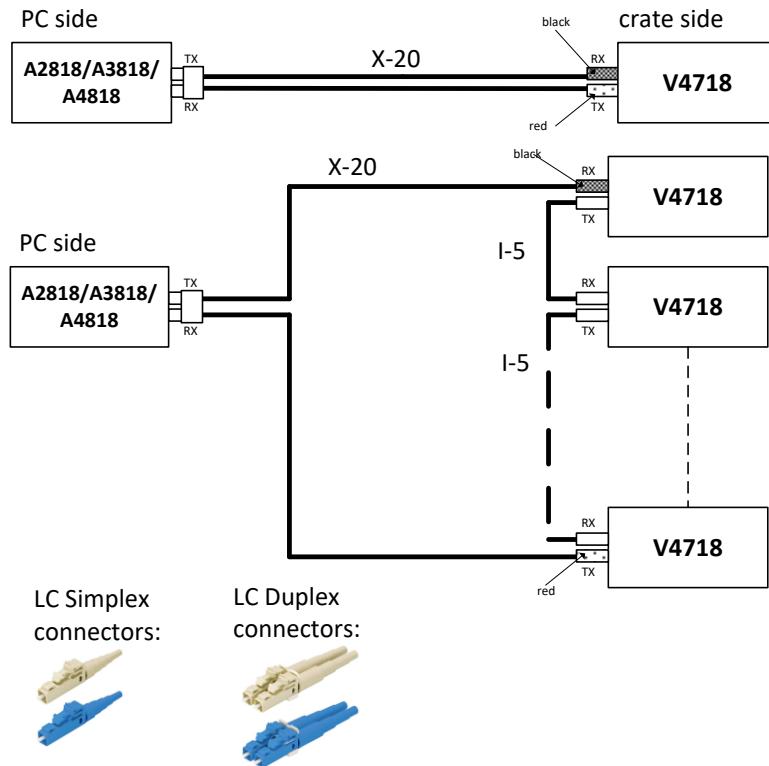

| Fig. 9.4: Example of optical network .....                                                                                                                                        | 24 |

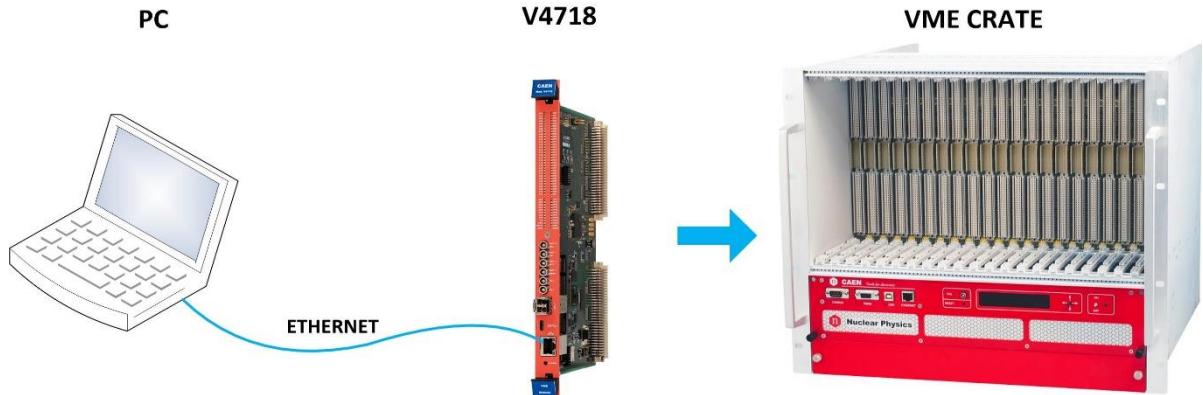

| Fig. 9.5: Example of point-to-point Ethernet connection .....                                                                                                                     | 24 |

| Fig. 10.1: Internal arbitration for VME bus request .....                                                                                                                         | 25 |

| Fig. 11.1: LED Status after V4718 power-on .....                                                                                                                                  | 41 |

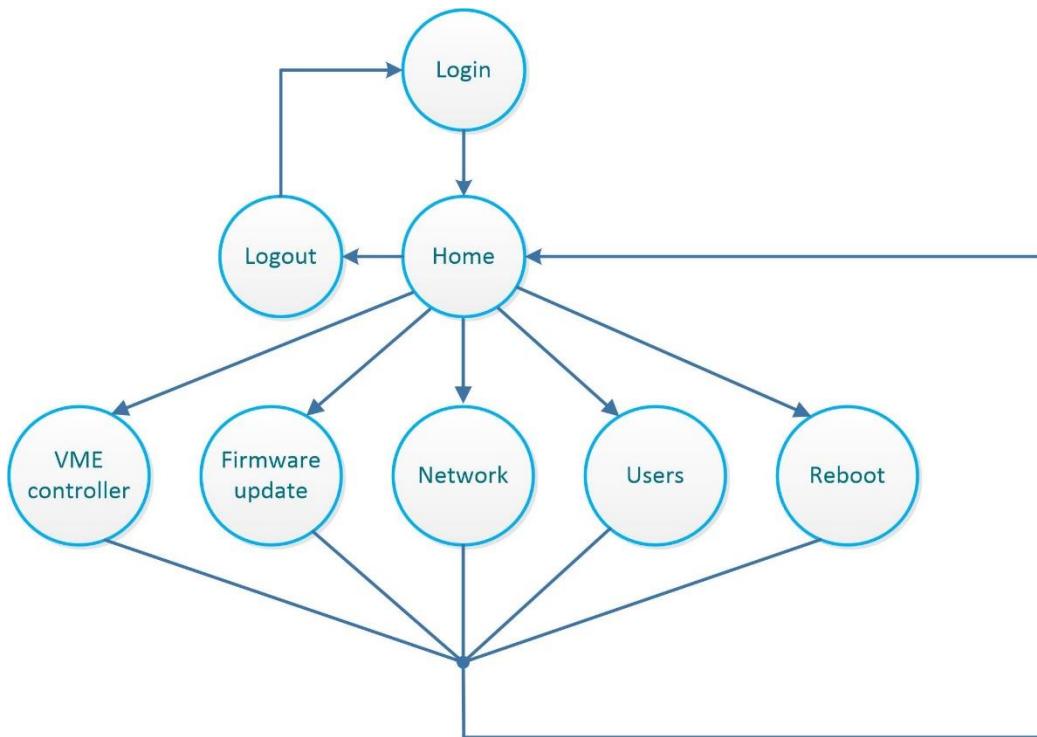

| Fig. 13.1: Flow Diagram of the Web Interface .....                                                                                                                                | 49 |

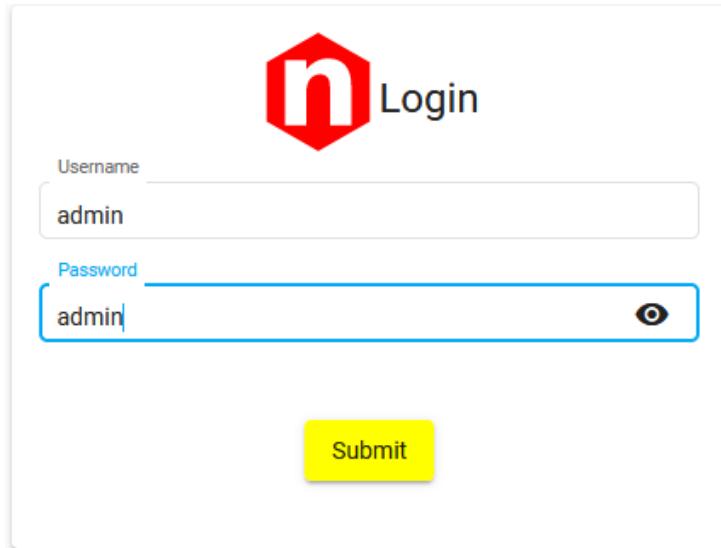

| Fig. 13.2: Login window .....                                                                                                                                                     | 50 |

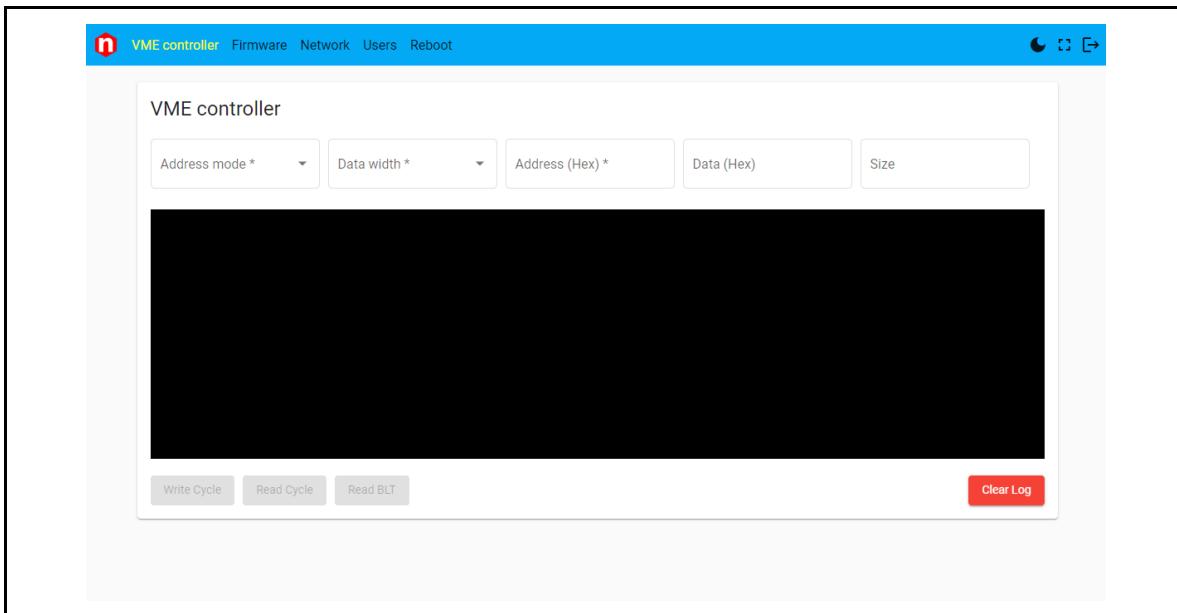

| Fig. 13.3: VME controller page .....                                                                                                                                              | 50 |

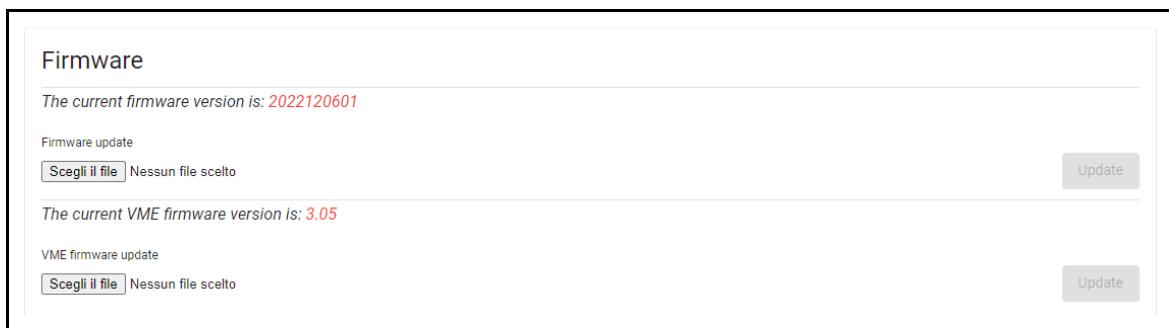

| Fig. 13.4: Firmware update page .....                                                                                                                                             | 51 |

| Fig. 13.5: Network page .....                                                                                                                                                     | 52 |

| Fig. 13.6: Users page .....                                                                                                                                                       | 52 |

| Fig. 13.7: Users page with the fields to change the password .....                                                                                                                | 52 |

| Fig. 13.8: Reboot dialog box .....                                                                                                                                                | 53 |

| Fig. 15.1: Scheme of CAEN hardware and software layers .....                                                                                                                      | 60 |

| Fig. 15.2: CAEN Toolbox Graphical User Interface .....                                                                                                                            | 61 |

| Fig. 16.1: Firmware upgrade settings .....                                                                                                                                        | 63 |

| Fig. 16.2: Get Firmware Release settings .....                                                                                                                                    | 63 |

## List of Tables

|                                                   |    |

|---------------------------------------------------|----|

| Tab. 1.1: Table of models and related items ..... | 8  |

| Tab. 3.1: Specifications table .....              | 10 |

|                                             |    |

|---------------------------------------------|----|

| Tab. 7.1: Dataway display table .....       | 18 |

| Tab. 9.1: CONET cables specifications ..... | 23 |

| Tab. 10.1: Register map.....                | 29 |

# Safety Notices

**CAUTION:** this product needs proper cooling.

**USE ONLY CRATES WITH FORCED COOLING AIR FLOW SINCE

OVERHEATING MAY DEGRADE THE MODULE PERFORMANCES!**

**CAUTION:** this product needs proper handling.

**THIS BRIDGE DOES NOT SUPPORT LIVE INSERTION (HOT SWAP)!

REMOVE OR INSERT THE BOARD WHEN THE CRATE IS POWERED OFF!**

**ALL CABLES MUST BE REMOVED FROM THE FRONT PANEL BEFORE

EXTRACTING THE BOARD FROM THE CRATE!**

CAEN provides the specific document “Precautions for Handling, Storage and Installation” available in the documentation tab of the product web page that the user is mandatory to read before to operate with CAEN equipment.

# 1 Introduction

The V4718 is CAEN VME-to-USB 3.0/Ethernet/Optical Link Bridge implementing a VME master controlled by a PC via USB 3.0, Gigabit Ethernet and CONET Link (CAEN proprietary optical link protocol), including all the functions in a 1-unit wide VME 6U form factor. The V4718 is characterized by an enhanced data rate and extended interfacing capabilities, thanks to the on-board Zynq Ultrascale+ SoC module (including an ARM-based processor running Linux OS).

The Bridge is also available in the VX4718 version with VME64X mechanics (VME64X cycles not implemented). In the present document, the “V4718” term will be used to generally refer to both versions, unless otherwise specified.

The optical link connection between the V4718 and the host PC requires a CAEN optical controller (A3818 PCI Express or the A2818 PCI card) or the A4818 USB 3.0-to-COMET compact adapter, and an optical fiber cable (see **Tab. 1.1**). Multi-crate sessions can be easily performed thanks to the CONET Daisy chain capability: up to eight V4718 units can be controlled by a single link of an A2818/A3818/A4818 building a CONET Optical Network.

The V4718 is compliant with the USB 3.1 Gen1 speed protocol and can be connected to the USB port of the PC running Windows or Linux OS. The V4718 also have a 1 Gigabit Ethernet port allowing high data transfer rate.

The V4718 can perform all cycles foreseen by the VME64 standard except those intended for 3U boards. The Bridge can operate as VME System Controller (normally when plugged in the slot 1) acting as a Bus Arbiter in Multi-Master systems. The activity on the VME bus can be monitored in detail both locally (through an 88-LED DataWay Display) and remotely.

The front panel of the V4718 hosts 6 TTL/NIM programmable I/Os on LEMO connectors: four outputs (default assignment is: DS<sub>n</sub>, AS, DTK, BERR) and two inputs. The I/Os can be programmed via USB, Ethernet and Optical Link to implement functions like Timer, Counter, Pulse generator, I/O register, and others (see **Chap. 8**).

The supported data transfer rate, with a CAEN slave readout in MBLT64 data transfer mode, is up to 60 MB/s by USB 3.0 and Ethernet and up to 80 MB/s by CONET2. Thanks to the 128KB memory buffer, the activity on the VME bus is not slowed down by the transfer rate on the USB port, on the Ethernet or on the CONET one, especially when several V4718 units share the same network.

The V4718 can be integrated into the most common Windows® and Linux® computers and middleware libraries are also provided. Moreover, the presence of an embedded Linux-based CPU gives to the user the chance of running custom software directly on-board.

The Web Interface of the V4718 allows the User to upgrade the firmware of the device, to set the Network parameters for the Ethernet connection, and to perform basic operations via the VME Bus (Read, Write, BLTRead, and BLTWrite).

**THE SOFTWARE SUPPORT OF THE FRONT PANEL I/O PROGRAMMING IS FROM THE CAENVMElib LIBRARY REV.3.3 ON**

| Board Models     |  | Description                                   |

|------------------|--|-----------------------------------------------|

| V4718            |  | V4718 – VME to USB 3.0/Ethernet/CONET Bridge  |

| VX4718           |  | VX4718 – VME to USB 3.0/Ethernet/CONET Bridge |

| Related Products |  | Description                                   |

| A2818            |  | A2818 – PCI Optical Link Controller           |

| A3818A           |  | A3818A – PCIe 1 Optical Link Controller       |

| A3818B           |  | A3818B – PCIe 2 Optical Link Controller       |

| A3818C           |  | A3818C – PCIe 4 Optical Link Controller       |

| A4818            |  | A4818 – USB 3.0 to CONET Adapter              |

| Accessories      |  | Description                                   |

| AI2740           |  | Optical Fibre 40 m simplex                    |

| AI2730           |  | Optical Fibre 30 m simplex                    |

| AI2720           |  | Optical Fibre 20 m simplex                    |

| AI2705           |  | Optical Fibre 5 m simplex                     |

| AI2703           |  | Optical Fibre 30 cm simplex                   |

| AY2730           |  | Optical Fibre 30 m duplex                     |

| AY2720           |  | Optical Fibre 20 m duplex                     |

| AY2705           |  | Optical Fibre 5 m duplex                      |

**Tab. 1.1:** Table of models and related items

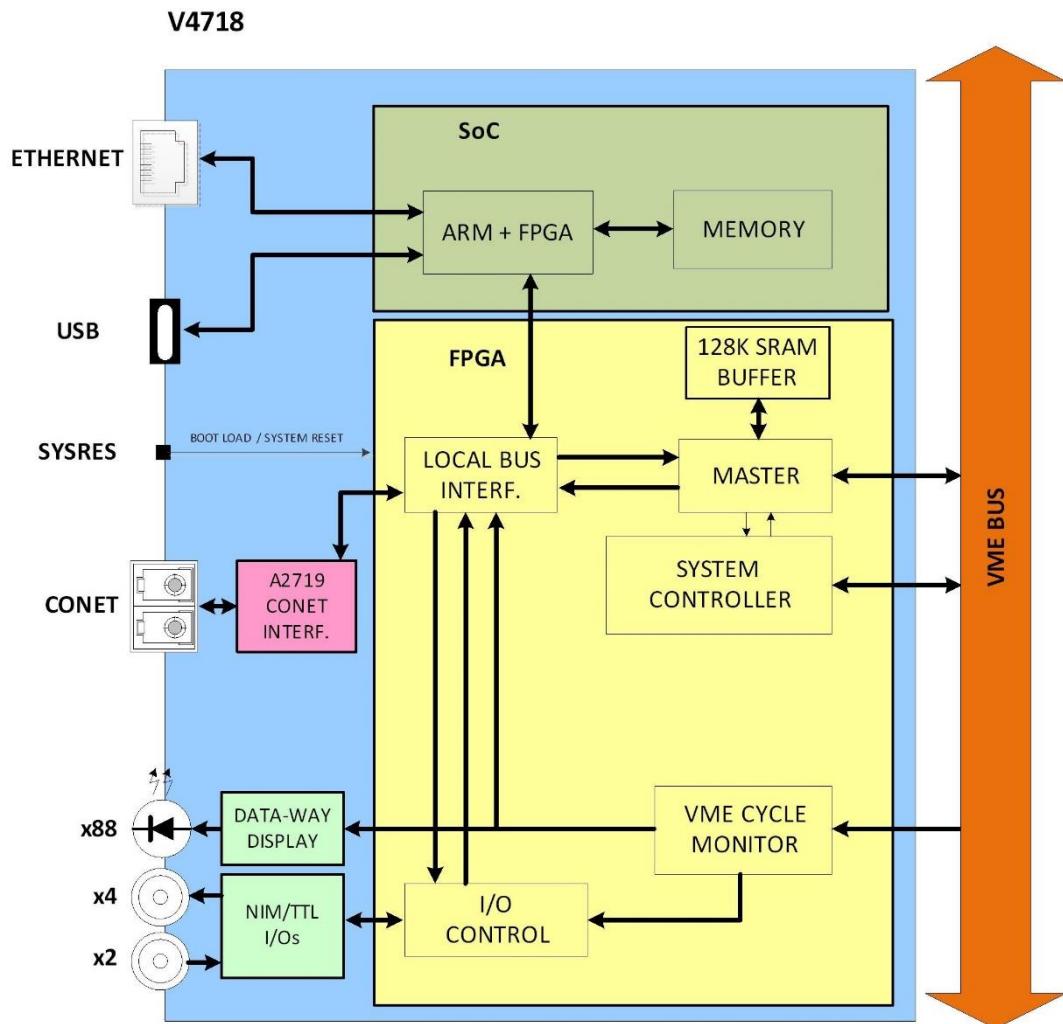

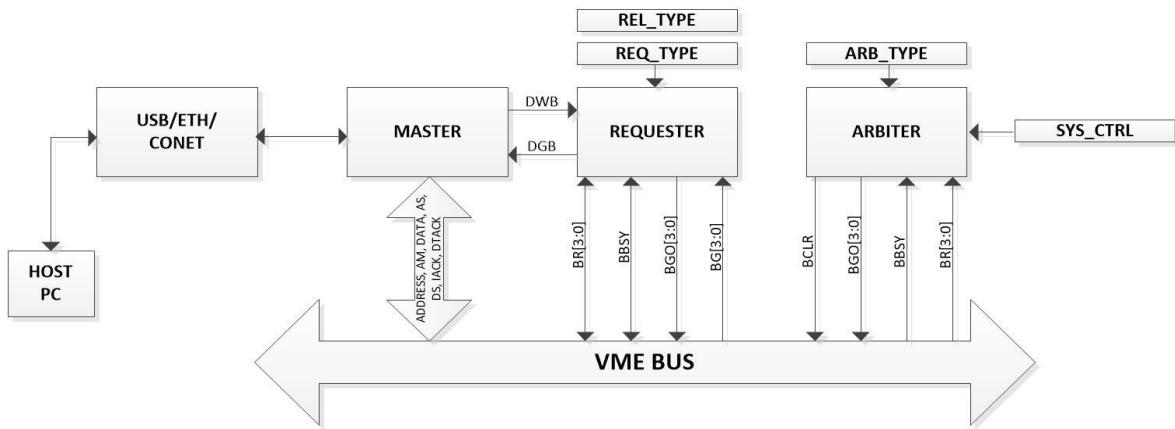

## 2 Block Diagram

Fig. 2.1: Simplified block diagram

The FPGA represents the core of the module, implementing the CONET communication protocols, handling the LED display and I/O connectors on the front side and the VME Master on the back side. The USB 3.0 and Gigabit Ethernet communication protocols are managed by the embedded SoC which communicates with the FPGA local bus interface.

Inside the FPGA, a 128KB buffer permits temporary data storage during VME cycles: the VME data rate is therefore decoupled from the USB, Ethernet and optical link rate and may take place at full speed.

### 3 Technical Specifications

|                                                |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                      |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>PHYSICAL</b>                                | <b>Form Factor</b><br>1-unit wide VME 6U                                                                                                                                                                                                                                                                  | <b>Weight</b><br>350g                                                                                                                                                                                |

| <b>PC INTERFACE</b>                            | <b>USB</b><br>USB 3.0<br>Type-C socket<br><br><b>Ethernet</b><br>Gigabit Ethernet<br>RJ45 connector                                                                                                                                                                                                       | <b>Optical Link</b><br>CONET 2 (CAEN protocol)<br>SFP+ connector                                                                                                                                     |

| <b>TRANSFER RATE</b>                           | Maximum transfer rate with a CAEN slave readout in MBLT64:<br><ul style="list-style-type: none"> <li>Up to 80 MB/s via CONET2</li> <li>Up to 60 MB/s via USB 3.0</li> <li>Up to 60 MB/s via Ethernet</li> </ul>                                                                                           |                                                                                                                                                                                                      |

| <b>ADDRESSING</b>                              | A16, A24, A32, CR/CSR, LCK; ADO, ADOH cycles                                                                                                                                                                                                                                                              |                                                                                                                                                                                                      |

| <b>DATA CYCLES</b>                             | D08, D16, D32 for R/W and RMW; D16, D32 for BLT, D64 for MBLT                                                                                                                                                                                                                                             |                                                                                                                                                                                                      |

| <b>INTERRUPT CYCLES</b>                        | D08, D16, D32, IACK                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                      |

| <b>INTERRUPTS<br/>TRANSFER AND<br/>MONITOR</b> | <b>Optical Link</b><br>VME interrupts IRQ[7:1] passed directly from VME to the PCIe bus via optical link; the host system is notified asynchronously (polling not required)<br><br><b>Ethernet</b><br>VME interrupts are not directly passed to the PC; the host system has to poll IRQ[7:1] via Ethernet | <b>USB</b><br>VME interrupts are not directly passed to the PC; the host system has to poll IRQ[7:1] via USB                                                                                         |

| <b>LED DISPLAY</b>                             | Data bus, address bus, address modifier, interrupt request, control signals                                                                                                                                                                                                                               |                                                                                                                                                                                                      |

| <b>PANEL I/Os</b>                              | <b>OUT[0:3]</b><br>4 signal outputs<br>SW programmable functions<br>Single-ended NIM/TTL ( $R_t = 50 \Omega$ )<br>LEMO 00 female socket                                                                                                                                                                   | <b>IN[0:1]</b><br>2 signal inputs<br>SW programmable functions<br>Single-ended NIM/TTL (HW programmable)<br>$Z_{in} = 50 \Omega$ or $1 \text{ k}\Omega$ hardware selectable<br>LEMO 00 female socket |

| <b>SOFTWARE</b>                                | <ul style="list-style-type: none"> <li>Windows® and Linux® support</li> <li>Drivers for the CONET communication link</li> <li>Middleware C/C++ libraries</li> <li>Web Interface for board control and firmware upgrade</li> <li>Linux OS embedded on ARM processor</li> </ul>                             |                                                                                                                                                                                                      |

| <b>POWER<br/>REQUIREMENTS</b>                  | 1.3 A @ +5V                                                                                                                                                                                                                                                                                               | 0.050 A @ +12V                                                                                                                                                                                       |

|                                                |                                                                                                                                                                                                                                                                                                           | 0.180 A @ -12V                                                                                                                                                                                       |

**Tab. 3.1:** Specifications table

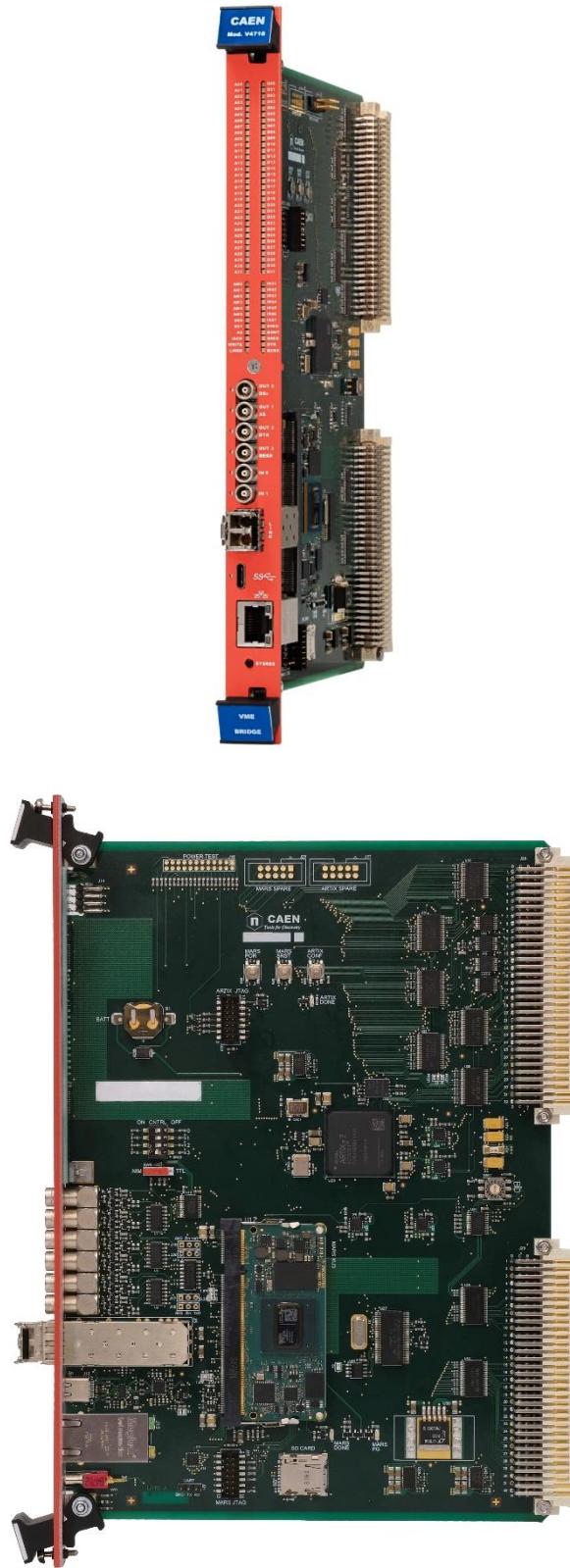

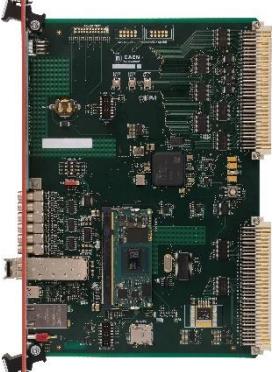

## 4 Packaging and Compliance

V4718/VX4718 are 1-unit wide 6U VME64/VME64X boards.

Fig. 4.1: Module views

**CAUTION:** this product needs proper cooling.

**USE ONLY CRATES WITH FORCED COOLING AIR FLOW SINCE

OVERHEATING MAY DEGRADE THE MODULE PERFORMANCES!**

**CAUTION:** this product needs proper handling.

**THIS BRIDGE DOES NOT SUPPORT LIVE INSERTION (HOT SWAP)!

REMOVE OR INSERT THE BOARD WHEN THE CRATE IS POWERED OFF!**

**ALL CABLES MUST BE REMOVED FROM THE FRONT PANEL BEFORE

EXTRACTING THE BOARD FROM THE CRATE!**

CAEN provides the specific document “[Precautions for Handling, Storage and Installation](#)” available in the documentation tab of the product web page that the user is mandatory to read before to operate with CAEN equipment.

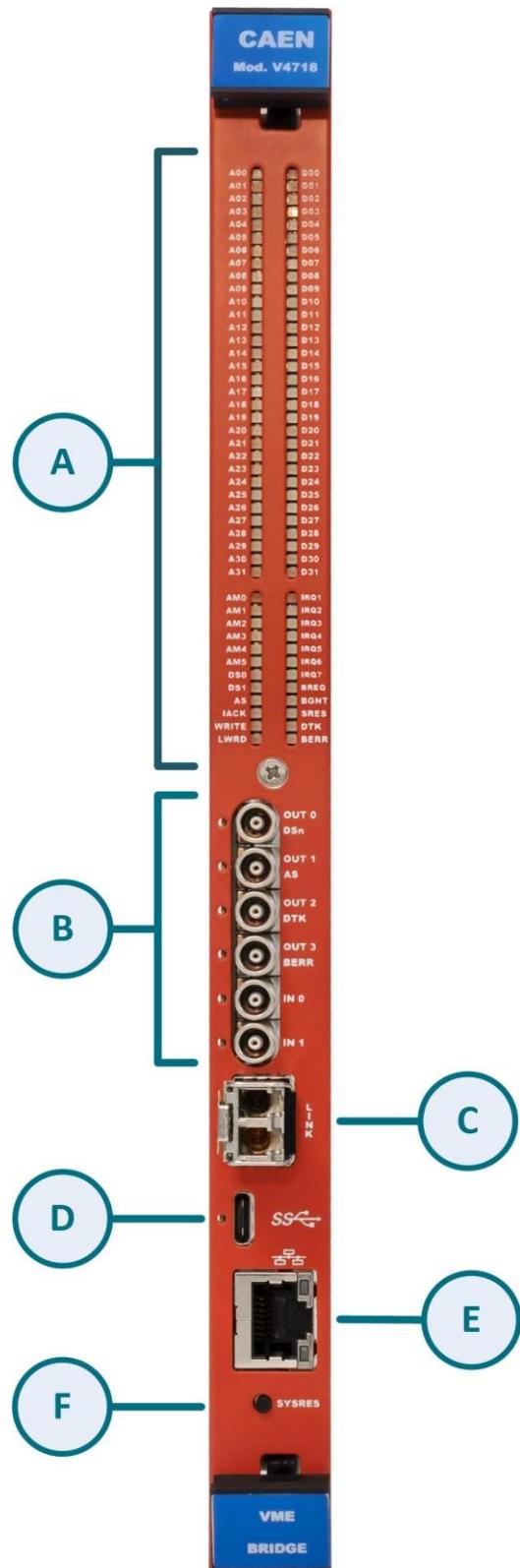

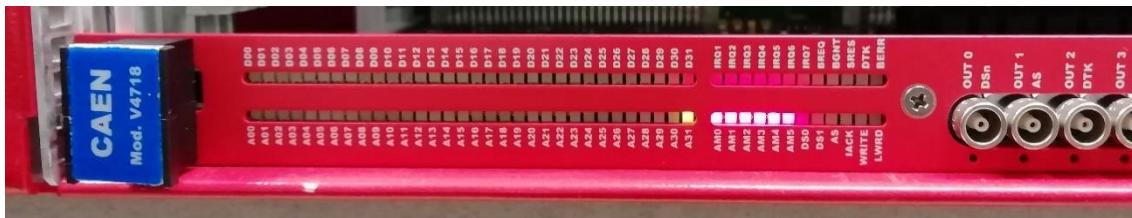

# 5 Panels Description

V4718 and VX4718 share the same panels arrangement.

Fig. 5.1: Front panel

## Front Panel

### DATAWAY DISPLAY

#### FUNCTION

88-LED visual monitor of the activity on the VME bus (data bus, address bus, address modifier, interrupt request, control signals). See Chap. 7.

### DIGITAL INPUTS/OUTPUTS

#### FUNCTION

Four outputs and two inputs, NIM/TLL hardware selectable (see Chap. 8). Inputs are internally terminated at  $50\ \Omega$  or  $1\ k\Omega$  by on-board jumper (see Chap. 6); outputs require  $50\ \Omega$  termination.

Default signals (see also Sec. **Internal Registers**)

- OUT 0 = DS<sub>n</sub>

- OUT 1 = AS

- OUT 2 = DTACK

- OUT 3 = BERR

- IN 0 = Scaler gate

- IN 1 = Scaler Input

#### MECHANICAL SPECS

Series: 101 A 004 connectors.

Type: DLP 101 A 004-28.

Manufacturer: FISCHER.

#### Alternatively:

Type: EPL 00 250 NTN.

Manufacturer: LEMO.

#### INDICATORS

LEDs (GREEN): when on, indicate activity on the relevant I/O channel.

### OPTICAL LINK PORT

#### FUNCTION

Optical LINK connector for data readout and flow control. Daisy chainable. Compliant to Multimode 62.5/125 $\mu$ m cable featuring LC connectors on both sides. Can support a maximum data rate of 80 MB/s.

#### PINOUT

TX (red wrap)

RX (black wrap)

#### MECHANICAL SPECS

Series: SFF Transceivers.

Type: FTLF8524P-2BNV (LC connectors).

Manufacturer: FINISAR.

#### INDICATORS

LEDs (GREEN/ORANGE): GREEN LED indicates the network presence, while ORANGE LED signals the data transfer activity.

### USB PORT

#### FUNCTION

USB connector for data readout and flow control. Compliant to USB 1.1, USB 2.0 and USB 3.0. Can support a maximum data rate of 60 MB/s.

#### MECHANICAL SPECS

Series: USB connectors.

Type: TYPE-C RECEPTACLE (632723300011).

Manufacturer: Wurth.

**INDICATORS**

LED (GREEN): indicates the USB communication is active.

**E**

**ETHERNET PORT**

**FUNCTION**

Ethernet connector (1000 base-T) for data readout and flow control. Can support a maximum transfer rate of 60 MB/s.

**MECHANICAL SPECS**

Series: RJ45 connectors.

Type: 0826-1A1T-23-F.

Manufacturer: Bel Fuse Inc.

**INDICATORS**

LEDs (GREEN/ORANGE): GREEN LED indicates the network presence, while ORANGE LED signals the data transfer activity.

**F**

**SYSTEM RESET BUTTON**

**FUNCTION**

- 1) System Reset: hold the SYSRES button down until the SRES LED flashes on the dataway display (see Chap. 7) to perform a system reset.

- 2) Boot load control: the button allows to alternatively enter the Backup mode or the Safe Mode, to possible recover from a partial or global FLASH issue (see Sec. **Troubleshooting**):

- *No action*: power on the Bridge without any action on the SYSRES button. The Bridge will boot in Standard mode and the VME firmware copy (see Chap. 0) stored in the Standard page of the FLASH is loaded on the FPGA (standard operating).

- *Short pressure*: power on the crate holding the SYSRES button down and release the button as soon as the front panel I/O LEDs light on. The Bridge will boot in Backup mode and the VME firmware copy stored in the Backup page of the FLASH is loaded on the FPGA.

- *Long pressure*: like short-pressure case but release the SYSRES button after the front panel I/O LEDs light off. The Bridge will boot in Safe Mode and the VME firmware copy stored in the Factory page of the FLASH is loaded on the FPGA.

**Note:** The System Reset Button does not allow to recover from partial or global FLASH issues related to the FPGA of the Zinc Ultrascale+ SoC.

# 6 Internal Components

## Switches

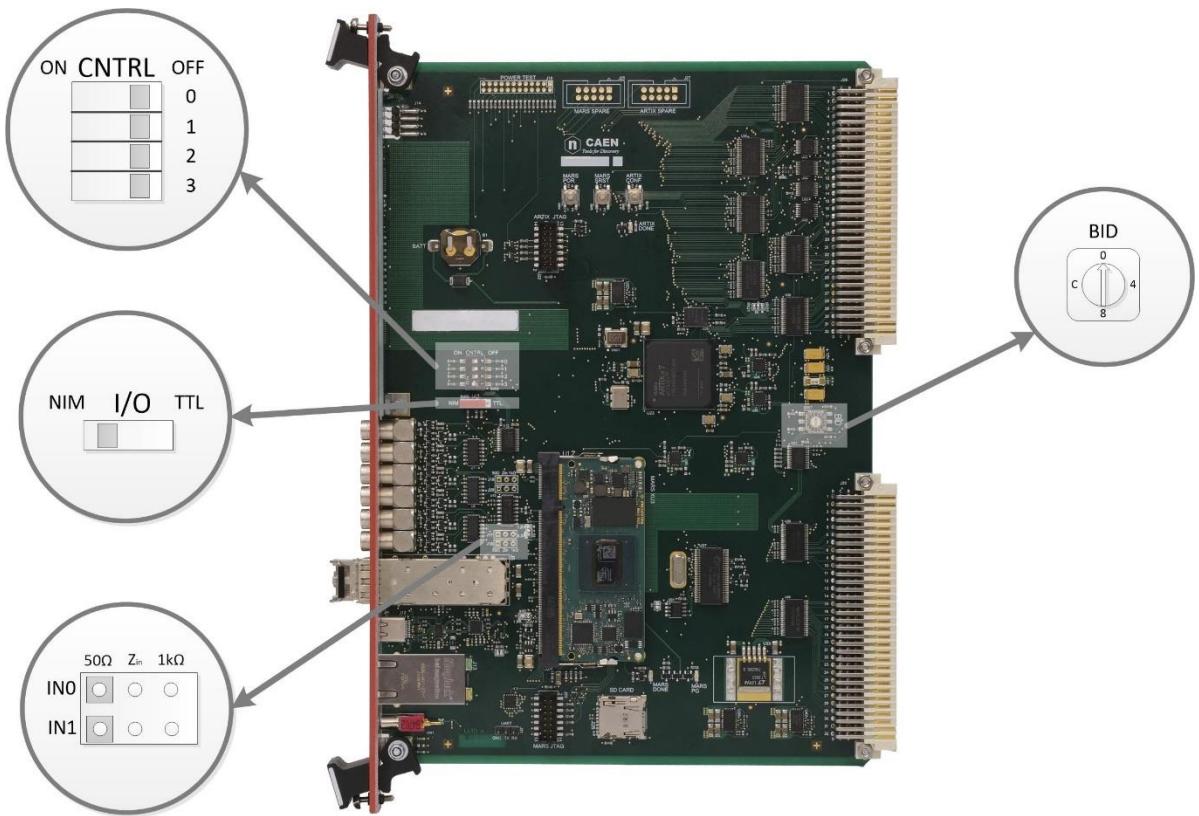

Fig. 6.1: Internal components

### CTRL Dip Switches

Four selectors of VME functions; the status of each switch can be read also in the STATUS Register (see Sec. **Internal Registers**).

- **PROG[0]**: forces the System Controller to be enabled, regardless of the 1<sup>st</sup> Slot detection (ON: SYSTEM CONTROLLER enabled; OFF: don't care).

- **PROG[1]**: forces the System Controller to be disabled, regardless of the 1<sup>st</sup> Slot detection (ON: SYSTEM CONTROLLER disabled; OFF: don't care).

- **PROG[2]**: when this switch is ON, the master initiates the VME cycles without waiting for the Bus Grant from the arbiter; this setting must be used only for test purposes, since conflicts may occur when more VME masters are present (ON: requester bypassed; OFF: don't care).

- **PROG[3]**: *not used*.

**NOTE:** if PROG[0] is set to ON, then PROG[1] must be set to OFF and vice versa.

### I/O Dip Switch

Common selector between NIM and TTL signals for the front panel I/Os (LEMO). The status of this switch can be read also in the STATUS Register (see Sec. **Internal Registers**).

### INPUT Z<sub>in</sub> Jumper

Selector of the input impedance for IN 0 and IN 1 front panel inputs: 50Ω default.

### BID Rotary Switch

Board identifier (Board ID).

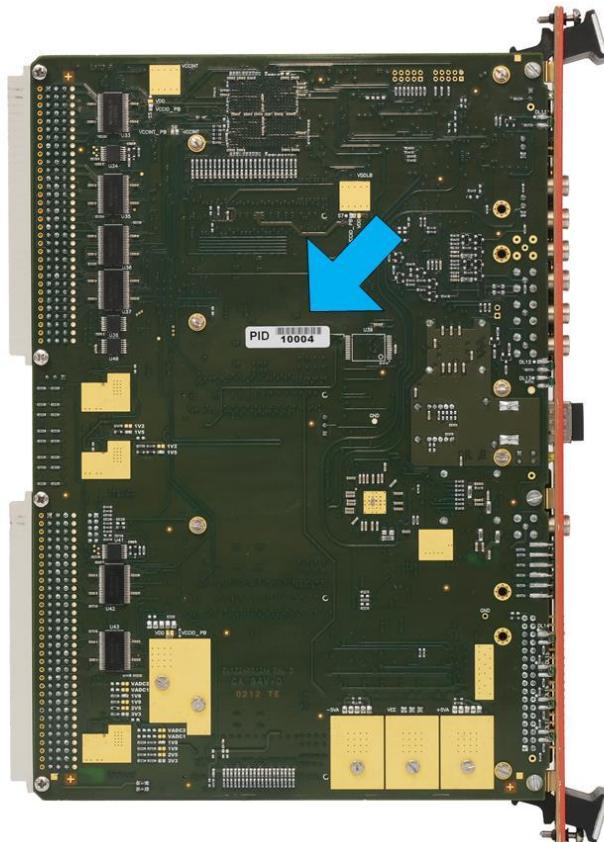

## Product Identification Number (PID)

The PID is the unique CAEN product identification number composed of a prefix followed by an incremental number greater than 10000 (Fig. 6.2).

Fig. 6.2: PID label

The PID label is placed in the B-side of the V4718 board (Fig. 6.3).

Fig. 6.3: PID location

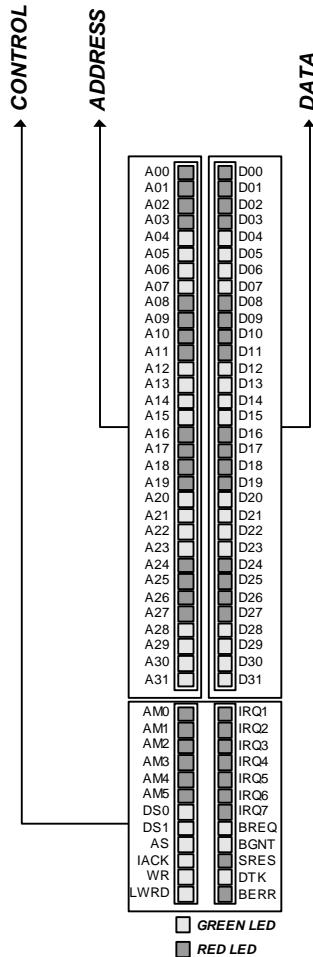

## 7 VME Dataway Display

Fig. 7.1: Dataway display layout

The V4718 is provided with an 88-LED Dataway Display. The LEDs report the VME Bus status (address, data and control lines) related to the latest cycle.

| NAME                                         | FUNCTION                                                                                                                                                                                                                                             |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[31:0]<br>AM[5:0]<br>IACK<br>WRITE<br>LWORD | These LEDs are frozen on the AS leading edge and remain stable until the next cycle                                                                                                                                                                  |

| D[31:0]                                      | These LEDs are frozen either on the DS leading edge during the write cycles or on the DTACK (or BERR) leading edge during the read cycles; the datum remains stable until the next cycle; in case of BLT cycles, the last read datum remains visible |

| DS0<br>DS1                                   | These LEDs turn on as the signal is active during the cycle just executed; they remain stable until the next cycle                                                                                                                                   |

| AS                                           | This LED flashes on the AS leading edge; it is used for signaling a cycle execution                                                                                                                                                                  |

| BGR                                          | This LED flashes as any Bus Grant line (BG[3:0]) is active                                                                                                                                                                                           |

| BRQ                                          | This LED flashes as any Bus Request line (BR[3:0]) is active                                                                                                                                                                                         |

| SRES                                         | This LED flashes as the SYSRES is active (see Sec. <b>Front Panel</b> )                                                                                                                                                                              |

| DTK                                          | This LED turns on if the cycle just executed was terminated with a DTACK asserted by a slave; it remains on until the next cycle                                                                                                                     |

| BERR                                         | This LED turns on if the cycle just executed was terminated with a BERR; it remains on until the next cycle                                                                                                                                          |

Tab. 7.1: Dataway display table

# 8 Programmable Inputs/Outputs

As described in Chap. 5, the V4718 houses six software programmable GPIOs on the front panel: four outputs and two inputs. The signals can be either NIM or TTL, selectable by onboard dip switch (see Chap. 6). Six green LEDs (one per connector) light up as the relevant signal is active.

The allowed programmable functions are the topic of this chapter, while the available registers are described in Sec. **Internal Registers**.

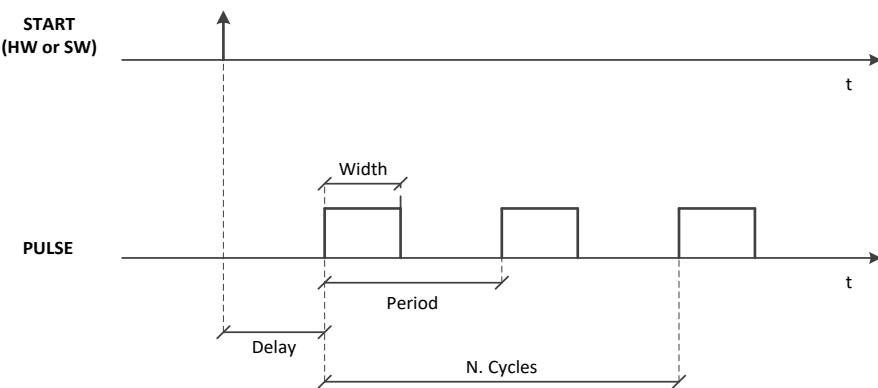

## Timer & Pulse Generator

There are two modules implemented (Pulser A and Pulser B), which work independently. Each module produces a burst of  $N$  pulses ( $N$  can be infinite, then the pulses are continuously generated) upon a start signal which can be HW from a GPIO or SW from a register. The delay from the start signal, the pulser period  $T$ , and the pulse width  $W$  are programmable. The Pulser output can be directed to a GPIO. The stop, which can be HW from a GPIO or SW from a register, will interrupt the sequence and set to zero the outputs.

A schematic view of the main parameters is shown in **Fig. 8.1**.

**Fig. 8.1:** Timer & Pulser Generator main parameters

By these modules, for example, it is possible to implement functions as:

- Clock Generator

- Burst Generator

- Monostable

- Gate and Delay Generator

- Set-Reset Flip-Flop

## Scaler

There is a single scaler module implemented that can work in different modes. It allows counting a given signal in a previously set acquisition window that can be either a gate signal (Gate mode), or a preset time (D-Well Time mode), or a maximum number of hits (MaxHits mode). Whichever the mode, an analog signal can be generated on an output GPIO as soon as the end of the acquisition window is reached.

In Gate mode, the signal to count can be either an input GPIO (IN0, IN1), or a combination of the two input GPIO (coincidence signal: IN0 AND IN1; OR signal: IN0 OR IN1), or a VME signal (i.e. Data Strobe, Address Strobe, Data Acknowledge, Bus Error). The gate signal can be given by an input GPIO (IN0, IN1) or a software register. At the end of the gate, the number of counts is written in a register and an internal memory.

Fig. 8.2: Gate mode example. The gate is a given signal and only the hits within the gate (in green) are counted

In D-Well Time mode, an internal time gate (called D-Well Time), with a resolution of 1 ms, is applied to the scaler. At the end of the D-Well Time, the number of counts is written in a register and an internal memory.

Fig. 8.3: D-Well mode example. Upon the start signal, the time counter starts counting the hits until the preset D-Well time is reached. Not counted hits are marked in red

In MaxHits mode, hits are counted until a hit number is reached.

**Fig. 8.4:** MaxHit mode example. Upon the start signal, only a programmable maximum number of hits are counted

The Start Acquisition can be set either by an external signal (on level), or register, or front panel SYSRES button.

During the acquisition, the counter can be reset either by an external signal, or register, or front panel SYSRES button.

The run mode can be “Single Run” or “Continuous Run”. In the former case, as soon as the end of the first gate (in Gate mode), or the Dwell Time (in D-Well Time mode), or the number of hits (in MaxHits mode) is reached, the acquisition is stopped. In the latter case, the acquisition continues until the start signal is active.

## Coincidence

This module makes the coincidence between two inputs. The coincidence signal is provided on the output when both the inputs are set to “1”. The output can be connected either to the input of other units or to an output GPIO.

## Input/Output Register

The output signals can be programmed via an Output Register, while the input signals can be monitored via an Input Register.

# 9 Optical Link, USB and Ethernet Layout

The V4718 houses a USB3.0 compliant port with a maximum transfer rate of 60 MB/s, a Daisy chainable Optical Link (communication path which uses optical fibre cables as physical transmission line and CONET2 serial protocol) with a maximum transfer rate of 80 MB/s and an Ethernet port with a maximum transfer rate of 60 MB/s.

## USB

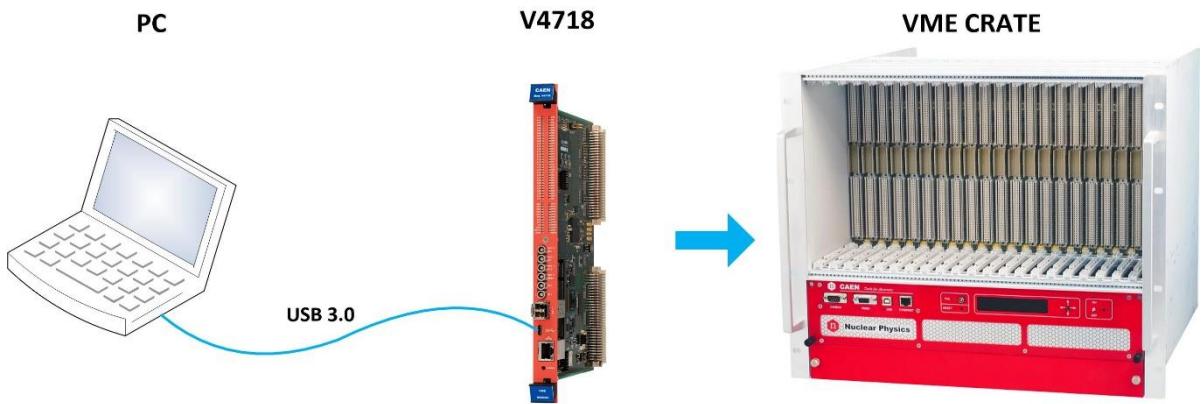

A Point-to-point direct connection between the host PC and the V4718 Bridge is supported on any USB 3.0 compatible port.

**Fig. 9.1: Example of USB layout**

## Optical Link

Optical link connection between the V4718 Bridge and the host PC is based on CONET2 protocol and requires A2818 or A3818 CAEN Controller with a CONET2 firmware, or the A4818 Adapter board (see **Tab. 1.1**). Detailed information and documentation can be found on CAEN website in the relevant product web page [\[RD4\]](#)[\[RD6\]](#).

The parameters for read/write accesses via Optical Link are the same used by VME cycles (Address Modifier, Base Address, Data Width, etc.); wrong parameter settings cause Bus Error.

**Note:** CONET2 is CAEN proprietary serial protocol developed to allow the optical link communication between the host PC, equipped with an A2818 or an A3818 Controller, and a CAEN CONET slave. CONET2 is 50% more efficient in the data transfer rate than the previous CONET1 version. The two protocol versions are not compliant to each other and before migrating from CONET1 to CONET2, it is recommended to read the instructions provided by CAEN in the dedicated Application Note [\[RD7\]](#).

**CONET1 IS SUPPORTED ONLY BY THE A2818 PCI CONTROLLER!**

**IT IS SO STRICTLY REQUIRED TO UPGRADE THE A2818 WITH A CONET2 FIRMWARE BEFORE COMMUNICATING WITH THE V4718!**

Fig. 9.2: Example of Optical Link setup through A3818 (or A2818)

Fig. 9.3: Example of Optical Link setup through A4818

The CAEN Optical Link features Daisy chain capabilities: up to eight CONET slave nodes can be connected in Daisy chain to the link of the A2818 or A4818, and to each link of a multi-link A3818 version. The A3818C (4-links) can support up to 32 CONET slave nodes in Daisy chain. For this purpose, various types of cables are available (see **Tab. 9.1**).

| Cable | Length | Connector                  |

|-------|--------|----------------------------|

| X-30  | 30 m   | 1 LC Duplex + 2 LC Simplex |

| X-20  | 20 m   | 1 LC Duplex + 2 LC Simplex |

| X-5   | 5 m    | 1 LC Duplex + 2 LC Simplex |

| I-40  | 40 m   | 2 LC Simplex               |

| I-30  | 30 m   | 2 LC Simplex               |

| I-20  | 20 m   | 2 LC Simplex               |

| I-5   | 5 m    | 2 LC Simplex               |

| I-3   | 30 cm  | 2 LC Simplex               |

Tab. 9.1: CONET cables specifications

If the network is composed by one A2818, A3818 or A4818, and only one V4718, then it is suggested to use X-type cables: such cables have a duplex connector on the A2818/A3818/A4818 side and two simplex connectors on the crate side; the simplex connector with the black wrap is for the RX line and the one with the red wrap is for the TX. If more than one V4718 are present, the best solution is to use the X-type cable for connecting the A2818/A3818/A4818 with the first and the last module, and the I-type for connecting intermediate modules. An example is given in **Fig. 9.4**.

Fig. 9.4: Example of optical network

## Ethernet

The V4718 Ethernet connector allows the user either to perform a point-to-point connection between the host PC and the module (see [Fig. 9.5](#)) or to connect to it via a LAN network.

Fig. 9.5: Example of point-to-point Ethernet connection

# 10 VME Interface

The V4718 provides all the addressing and data transfer modes documented in the VME64 specification (except A64 and those intended to improve 3U applications, like A40 and MD32). The V4718 is also compatible with all VME bus modules compliant to pre-VME64 specifications. As VME bus master, the V4718 supports Read-Modify-Write (RMW), and Address-Only-with-Handshake (ADOH) but does not accept RETRY\* as a termination from the VME bus slave. The ADOH cycle is used to implement the VME bus Lock command allowing the PC Host to lock VME bus resources.

## VME Bus Requester

Fig. 10.1: Internal arbitration for VME bus request

When the V4718 operates as VME bus Requester, the functional sequence is as follows:

- The USB/ETH/CONET sends a VME bus access request.

- The Master asserts DWB (Device Want Bus) and waits for DGB (Device Grant Bus).

- The Requester requests the bus to the Arbiter, via VME (whether the Arbiter is the V4718 itself or not); when the Arbiter has granted the bus, the Requester asserts DGB and BBSY (on the bus).

- The Master performs the VME cycle, then releases DWB.

- If REL\_TYPE is RWD (Release When Done), then the Requester releases BBSY.

### Fair and Demand Request Modes

The V4718 produces requests on all VME bus request levels: BR3\*, BR2\*, BR1\*, and BR0\*. The default setting is for level 3 VME bus request. The request level is a global programming option set through the Bus Request field in the Control register (see Sec. Internal Registers).

The programmed request level is used by the VME bus Master Interface regardless of the channel currently accessing the VME bus Master Interface.

The Requester may be programmed for either Fair or Demand mode. The request mode is a global programming option set through the Requester Type bit in the Control register.

In Fair mode, the V4718 does not request the VME bus until there are no other VME bus requests pending at its programmed level. This mode ensures that every requester on an equal level has access to the bus.

In Demand mode, the requester asserts its bus request regardless of the state of the BRn\* line. By requesting the bus frequently, requesters far down the daisy chain may be prevented from ever obtaining bus ownership. This is referred to as “starving” those requesters. Note that, to achieve fairness, all bus requesters in a VME bus system must be set to Fair mode.

## VME Bus Release

The Requester can be configured as either RWD (Release When Done) or ROR (release on request) using the Release Type bit in the Control register (see Sec. [Internal Registers](#)). The default setting is for RWD: the bus is released as soon as the VME access is terminated; in case of BLT/MBLT cycles, the access is terminated either when the N required bytes are transferred (although the cycle is divided into several blocks according to the VME boundaries) or when BERR\* is asserted. ROR means the master releases BBSY\* only if a bus request is pending from another VME bus master and once the channel that is the current owner of the VME bus Master Interface is done. Ownership of the bus may be assumed by another channel without re-arbitration on the bus if there are no pending requests on any level on the VME bus.

# Addressing Capabilities

The V4718 generates A16, A24, A32, CR/CSR and LCK address phases on the VME bus. Address Modifiers of any kind (supervisor/non-privileged and program/data) are also programmed through USB, Ethernet or CONET: the V4718 does not handle the AM; the HOST PC passes them via USB or Ethernet as VME cycle parameters. The AM broadcasting depends on the PC drivers.

The master generates Address-Only-with-Handshake (ADOH) cycles in support of lock commands for A16, A24, and A32 spaces.

### Supported addressing:

|                       |                             |

|-----------------------|-----------------------------|

| A16, A24, A32, CR/CSR | for R/W, RMW, ADO and ADOH  |

| A16, A24, A32         | for BLT                     |

| A16, A24, A32         | for MBLT                    |

| ADO                   | Address Only                |

| ADOH                  | Address Only with Handshake |

## Data Transfer Capabilities

The V4718 supports the following cycles:

### Cycle Type

|      |                            |

|------|----------------------------|

| R/W  | Single Read/Write          |

| RMW  | Read Modify Write          |

| BLT  | Block Transfer             |

| MBLT | Multiplexed Block Transfer |

## Data sizing

D08(EO), D16, D32 for R/W, RMW, BLT

D64 for MBLT

- BLT/MBLT cycles may be performed with either address increment or with fixed address (FIFO mode)

- BLT/MBLT cycles are split at hardware level when the boundary (BLT = Nx256 bytes; MBLT = Nx2 Kbytes) is met: AS is released and then re-asserted, the VME bus is not re-arbitrated. The boundaries are neglected in FIFO operating mode.

- Non-aligned accesses are not supported

It is then possible to perform data cycles (single and BLT) with hardware byte swapping. The “Swapped” cycles are called: D16\_swapped, D32\_swapped and D64\_swapped. Such cycles will return “swapped” data, in the following way:

D16 swapped: Byte0  $\leftrightarrow$  Byte1, Byte1  $\leftrightarrow$  Byte0

D32 swapped: Byte0  $\leftrightarrow$  Byte3, Byte1  $\leftrightarrow$  Byte2, Byte2  $\leftrightarrow$  Byte1, Byte3  $\leftrightarrow$  Byte0

D32\_swapped: Byte0  $\leftrightarrow$  Byte7, Byte1  $\leftrightarrow$  Byte6, Byte2  $\leftrightarrow$  Byte5, Byte3  $\leftrightarrow$  Byte4, Byte4  $\leftrightarrow$  Byte3, Byte5  $\leftrightarrow$  Byte2, Byte6  $\leftrightarrow$  Byte1, Byte7  $\leftrightarrow$  Byte0

## Interrupt Capabilities

### USB Link

The USB link does not allow transferring an interrupt to the PC, so the communication between the PC and the V4718 is always started by the PC. The VME interrupts are activated by reading the IRQ lines status from the PC and, if one line is active, then a IACK cycle can be executed.

The V4718 supports the following IACK cycles:

IACK: D08, D16, D32

### Ethernet Link

The Ethernet link does not allow transferring an interrupt to the PC, so the communication between the PC and the V4718 is always started by the PC. The VME interrupts are activated by reading the IRQ lines status from the PC and, if one line is active, then a IACK cycle can be executed.

The V4718 supports the following IACK cycles:

IACK: D08, D16, D32

### Optical Link

The VME Bus interrupts are transferred to the PCI/PCIe BUS through the CONET. The interrupt latency (i.e. the interval between the interrupt appearance on the VME bus and the time the interrupt is activated on the PCI bus) is always shorter than 5  $\mu$ s.

The V4718 supports the following IACK cycles:

IACK: D08, D16, D32

The VME Bus Interrupts can be individually masked for each V4718 in the chain.

The CAENVMLib library (see Chap. 15) makes available specific functions like the first-to-be-used *IRQEnable()* which enables the generation of PCI bus interrupts following VME bus interrupts, and the *IRQWait()* that must be then called to wait for the interrupt. When the *IRQWait()* returns, the VME bus interrupts are disabled, so an IACK can be performed in order to obtain the vector and, for RORA interrupts, the access to the interrupter must be performed in order to stop the interrupt generation. If it is necessary to receive other VME bus interrupts, the *IRQEnable* must be called again. Find detailed description in the library documentation [\[RD4\]](#).

## Cycle Terminations

The V4718 accepts BERR\* or DTACK\* as cycle terminations. BERR\* is handled as cycle termination whether it is produced by the V4718 itself or by another board. The Status word broadcasted as the cycle is acknowledged, informs the HOST PC about the cycle termination type (BERR\* or DTACK\*).

## VME Bus First Slot Detector

The First Slot Detector module samples BG3IN\* immediately after reset to determine whether the V4718 resides in slot 1. The VME bus specification requires the BG[3:0]\* lines to be driven high during reset. This means that, if a board is preceded by another board in the VME bus system, it will always sample BG3IN\* high after reset. BG3IN\* can only be sampled low after reset by the first board in the crate (there is no preceding board to drive BG3IN\* high). If BG3IN\* is sampled at logic low immediately after reset (due to the master internal pull-down), then the V4718 is in slot 1 and becomes SYSTEM CONTROLLER; otherwise, the SYSTEM CONTROLLER module is disabled. This mechanism may be overridden via dip switch setting: the SYSTEM CONTROLLER bit is “forced” to one by setting to ON PROG\_0, and is “forced” to zero by setting to ON PROG\_1; note that such switches must always be in “opposite” positions (see Chap. 6).

## System Controller Functions

When located in Slot 1 of the VME crate, the V4718 assumes the role of SYSTEM CONTROLLER and sets the SYSTEM CONTROLLER status bit in the STATUS register (see Sec. [Internal Registers](#)). In accordance with the VME64 specification, as SYSTEM CONTROLLER the V4718 provides:

- a system clock driver

- an arbitration module

- an IACK Daisy Chain Driver (DCD)

- a bus timer

## System Clock Driver

The V4718 provides a 16MHz SYSCLK signal when configured as SYSTEM CONTROLLER.

## Arbitration Module

When the V4718 is SYSTEM CONTROLLER, the Arbitration Module is enabled. The Arbitration Module supports the following arbitration modes:

- Priority Based (PRI),

- Round Robin Select (RRS) (default setting).

These modes can be set in the CONTROL register (see Sec. [Internal Registers](#)).

In the Priority Based Mode (PRI), the order of priority is BR[3], BR[2], BR[1], and BR[0] as defined by the VME64 specification. The Arbitration Module issues a Bus Grant (BGO[3:0]) to the highest requesting level. If a Bus Request of higher priority than the current bus owner becomes asserted, the Arbitration Module asserts BCLR until the owner releases the bus (BBSY is negated).

Round Robin Select mode (RRS) arbitrates all levels in a round robin mode, repeatedly scanning from levels 3 to 0. Only one grant is issued per level and one owner is never forced from the bus in favour of another requester (BCLR is never asserted). Since only one grant is issued per level on each round robin cycle, several scans will be required to service a queue of requests at one level.

## Bus Timer

A programmable bus timer allows users to select a VME bus time-out period. The time-out period is configurable as 50  $\mu$ s or 400  $\mu$ s through the Bus Timeout bit in the Control register (see Sec. [Internal Registers](#)). The VME bus Timer module asserts BERR if a VME bus transaction times out (indicated by one of the VME bus data strobes remaining asserted beyond the time-out period).

## IACK Daisy Chain Driver

The V4718 can operate as IACK Daisy Chain Driver: it drives low the IACKOUT line of the first slot, thus starting the chain propagation, as soon as it detects an Interrupt Acknowledge cycle by an Interrupt Handler (that could be the V4718 itself).

## VME64X Cycles

The VME64X cycles are not implemented in this board.

## Internal Registers

| NAME                 | ADDRESS | TYPE       | Nbit | FUNCTION                                 |

|----------------------|---------|------------|------|------------------------------------------|

| STATUS               | 0x00    | read       | 16   | Status register                          |

| CONTROL              | 0x01    | read/write | 16   | VME control register                     |

| FIRMWARE_REVISION    | 0x02    | read       | 16   | FW revision register                     |

| IRQ_STATUS           | 0x05    | read       | 16   | IRQ status register                      |

| IRQ_MASK             | 0x06    | read/write | 16   | IRQ mask register                        |

| IO_LEVEL             | 0x07    | Read/write | 16   | I/O level set register                   |

| IO_POLARITY          | 0x08    | read/write | 16   | I/O polarity register                    |

| OUT_2_0_MUX_SET      | 0x09    | read/write | 16   | OUT[2:0] Multiplexer set register        |

| OUT3_MUX_SET         | 0x0A    | read/write | 16   | OUT[3], IN[1:0] Multiplexer set register |

| IO_STATUS_READ       | 0x0B    | read/write | 16   | I/O status read register                 |

| IO_STATUS_SET        | 0x0C    | read/write | 16   | I/O status set register                  |

| IO_COINC             | 0x0D    | read/write | 16   | I/O coincidence mask register            |

| PULSE_A_SETUP        | 0x10    | read/write | 16   | Pulser A source register                 |

| PULSE_A_START        | 0x11    | read/write | 16   | Pulser A start register                  |

| PULSE_A_CLEAR_(STOP) | 0x12    | read/write | 16   | Pulser A clear (stop) register           |

| PULSE_A_NCIRCLE      | 0x13    | read/write | 16   | Pulser A n cycles register               |

| PULSE_A_WIDTH        | 0x14    | read/write | 16   | Pulser A width register                  |

| PULSE_A_DELAY        | 0x15    | read/write | 16   | Pulser A delay register                  |

| PULSE_A_PERIOD       | 0x16    | read/write | 16   | Pulser A period register                 |

| PULSE_B_SETUP        | 0x17    | read/write | 16   | Pulser B source register                 |

| PULSE_B_START        | 0x18    | read/write | 16   | Pulser B start register                  |

| PULSE_B_CLEAR_(STOP) | 0x19    | read/write | 16   | Pulser B clear (stop) register           |

| PULSE_B_NCIRCLE      | 0x1A    | read/write | 16   | Pulser B n cycles register               |

| PULSE_B_WIDTH        | 0x1B    | read/write | 16   | Pulser B width register                  |

| PULSE_B_DELAY        | 0x1C    | read/write | 16   | Pulser B delay register                  |

| PULSE_B_PERIOD       | 0x1D    | read/write | 16   | Pulser B period register                 |

| DISPLAY_ADDRESS_LOW  | 0x20    | read       | 16   | Display AD[15:0] register                |

| DISPLAY_ADDRESS_HIGH | 0x21    | read       | 16   | Display AD[31:16] register               |

| DISPLAY_DATA_LOW     | 0x22    | read       | 16   | Display DT[15:0] register                |

| DISPLAY_DATA_HIGH    | 0x23    | read       | 16   | Display DT[31:16] register               |

| SCALER_SETUP         | 0x2D    | read/write | 16   | Scaler source register                   |

| SCALER_MAXHITS       | 0x2E    | read/write | 16   | Scaler end counter register              |

| SCALER_DWELL_TIME    | 0x2F    | read/write | 16   | Scaler dwell time register               |

| SCALER_SW_SETTING    | 0x30    | read/write | 16   | Scaler gate and reset signal register    |

| SCALER_INST_OUT      | 0x31    | read/write | 16   | Scaler instantaneous out register        |

| SCALER_FIFO_OUT      | 0x32    | read/write | 16   | <i>To be implemented</i>                 |

Tab. 10.1: Register map

## STATUS Register (Addr = 0X00)

This register contains information on the status of the module.

| Bit     | Description                                                              |

|---------|--------------------------------------------------------------------------|

| [0]     | SYSTEM RESET:<br>0 = Inactive<br>1 = Active                              |

| [1]     | SYSTEM CONTROL:<br>0 = Disabled<br>1 = Enable                            |

| [3:2]   | <i>reserved</i>                                                          |

| [4]     | DTACK:<br>1 = Last cycle terminated with DTACK<br>0 = Any other case     |

| [5]     | BERR:<br>1 = Last cycle terminated with BERR<br>0 = Any other case       |

| [7:6]   | <i>reserved</i>                                                          |

| [8]     | Status of Dip Switch 0:<br>0 = Switch set to OFF<br>1 = Switch set to ON |

| [9]     | Status of Dip Switch 1:<br>0 = Switch set to OFF<br>1 = Switch set to ON |

| [10]    | Status of Dip Switch 2:<br>0 = Switch set to OFF<br>1 = Switch set to ON |

| [11]    | Status of Dip Switch 3:<br>0 = Switch set to OFF<br>1 = Switch set to ON |

| [12]    | <i>reserved</i>                                                          |

| [13]    | NIM/TTL STATUS:<br>0 = NIM<br>1 = TTL                                    |

| [15:14] | <i>reserved</i>                                                          |

## CONTROL Register (Addr = 0X01)

This register allows performing some general settings of the module.

| Bit     | Description                                                                  |

|---------|------------------------------------------------------------------------------|

| [0]     | <i>reserved</i>                                                              |

| [1]     | ARBITER TYPE:<br>0 = Fixed Priority<br>1 = Round Robin                       |

| [2]     | REQUESTER TYPE:<br>0 = Fair<br>1 = Demand                                    |

| [3]     | RELEASE TYPE:<br>0 = Release When Done (RWD)<br>1 = Release On Request (ROR) |

| [5:4]   | BUS REQUEST LEVEL                                                            |

| [6]     | INTERRUPT REQUEST                                                            |

| [7]     | SYSTEM RESET (SysRes)                                                        |

| [8]     | BUS TIMEOUT:<br>0 = 50 µs<br>1 = 400 µs                                      |

| [9]     | ADDRESS INCREMENT DURING BLT:<br>0 = enabled<br>1 = disabled (FIFO mode)     |

| [10]    | SINGLE CYCLE SEQUENCE                                                        |

| [15:11] | <i>reserved</i>                                                              |

## FIRMWARE REVISION Register (Addr = 0X02)

This register contains the firmware revision number coded over 16 bits as X.Y.

| Bit    | Description               |

|--------|---------------------------|

| [7:0]  | MINOR REVISION NUMBER (Y) |

| [15:8] | MAJOR REVISION NUMBER (X) |

## IRQ STATUS Register (Addr = 0X05)

This register monitors the status of the IRQ lines.

| Bit    | Description                               |

|--------|-------------------------------------------|

| [0]    | IRQ LINE 1:<br>0 = inactive<br>1 = active |

| [1]    | IRQ LINE 2:<br>0 = inactive<br>1 = active |

| [2]    | IRQ LINE 3:<br>0 = inactive<br>1 = active |

| [3]    | IRQ LINE 4:<br>0 = inactive<br>1 = active |

| [4]    | IRQ LINE 5:<br>0 = inactive<br>1 = active |

| [5]    | IRQ LINE 6:<br>0 = inactive<br>1 = active |

| [6]    | IRQ LINE 7:<br>0 = inactive<br>1 = active |

| [15:7] | <i>reserved</i>                           |

## IRQ MASK Register (Addr = 0X06)

This register sets the IRQ mask.

| Bit    | Description     |

|--------|-----------------|

| [6:0]  | IRQ LINE [6:0]  |

| [15:7] | <i>Reserved</i> |

## I/O LEVEL SET Register (Addr = 0X07)

This register allows setting the TTL/NIM level for the I/O front panel signals.

| Bit    | Description                                                                                           |

|--------|-------------------------------------------------------------------------------------------------------|

| [1:0]  | <i>reserved</i>                                                                                       |

| [2]    | <i>reserved</i> (must be 1)                                                                           |

| [3]    | <i>reserved</i> (must be 1)                                                                           |

| [4]    | <i>reserved</i> (must be 0)                                                                           |

| [5]    | <i>reserved</i> (must be 0)                                                                           |

| [6]    | HW/SW Level selection:<br>0 = selection is HW (see Chap. 6)<br>1 = selection is SW ( <i>default</i> ) |

| [7]    | Level selection:<br>0 = NIM ( <i>default</i> )<br>1 = TTL                                             |

| [15:8] | <i>reserved</i>                                                                                       |

## I/O POLARITY Register (Addr = 0X08)

This register allows inverting the polarity of the front panel I/O signals. Direct means the original polarity, which could be active low or active high. Inverting an active-low I/O then means to set it active high, and vice versa.

| Bit    | Description                                                     |

|--------|-----------------------------------------------------------------|

| [0]    | OUT0 polarity:<br>0 = direct ( <i>default</i> )<br>1 = inverted |

| [1]    | OUT1 polarity:<br>0 = direct ( <i>default</i> )<br>1 = inverted |

| [2]    | OUT2 polarity:<br>0 = direct ( <i>default</i> )<br>1 = inverted |

| [3]    | OUT3 polarity:<br>0 = direct ( <i>default</i> )<br>1 = inverted |

| [4]    | IN0 polarity:<br>0 = direct ( <i>default</i> )<br>1 = inverted  |

| [5]    | IN1 polarity:<br>0 = direct ( <i>default</i> )<br>1 = inverted  |

| [15:6] | <i>reserved</i>                                                 |

## OUT [2:0] MULTIPLEXER SET Register (Addr = 0X09)

This register allows to set the function for OUT0, OUT1, and OUT2 front panel I/Os.

| Bit     | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3:0]   | OUT0 function:<br>0000 = Data Strobe signal ( <i>default</i> )<br>0001 = Address Strobe signal<br>0010 = Data Acknowledge signal<br>0011 = Bus Error signal<br>0100 = Coincidence signal<br>0101 = Pulser A Output<br>0110 = Pulser B Output<br>0111 = Counter End Gate signal<br>1000 = Location Monitor signal<br>1001 = Register Set Status value<br>1010 = Device Grant VME bus signal<br>Others = <i>reserved</i> (OUT0 is set at 0) |

| [7:4]   | OUT1 function:<br>0000 = Data Strobe signal<br>0001 = Address Strobe signal ( <i>default</i> )<br>0010 = Data Acknowledge signal<br>0011 = Bus Error signal<br>0100 = Coincidence signal<br>0101 = Pulser A Output<br>0110 = Pulser B Output<br>0111 = Counter End Gate signal<br>1000 = Location Monitor signal<br>1001 = Register Set Status value<br>1010 = Device Grant VME bus signal<br>Others = <i>reserved</i> (OUT1 is set at 0) |

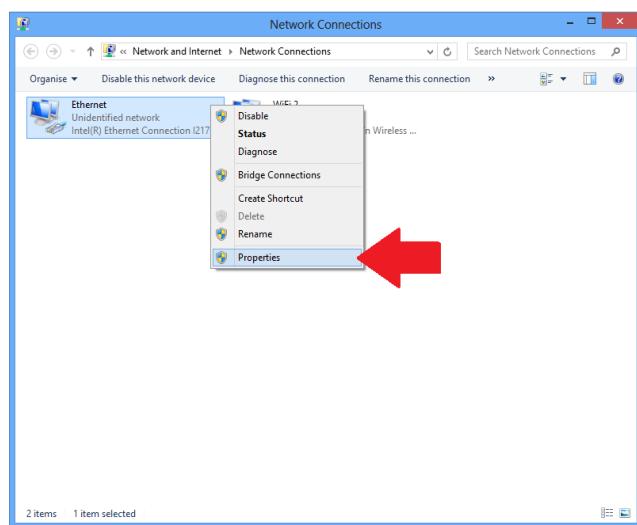

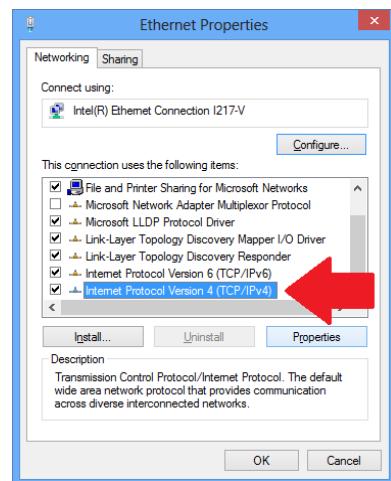

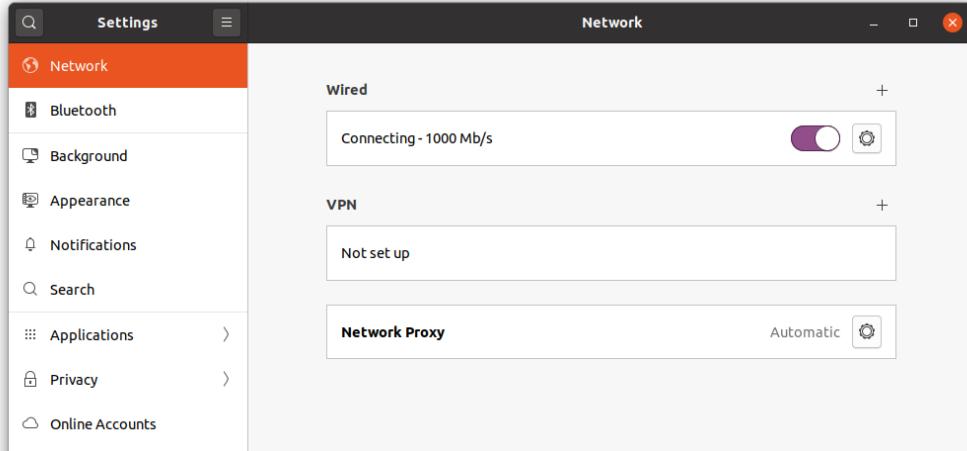

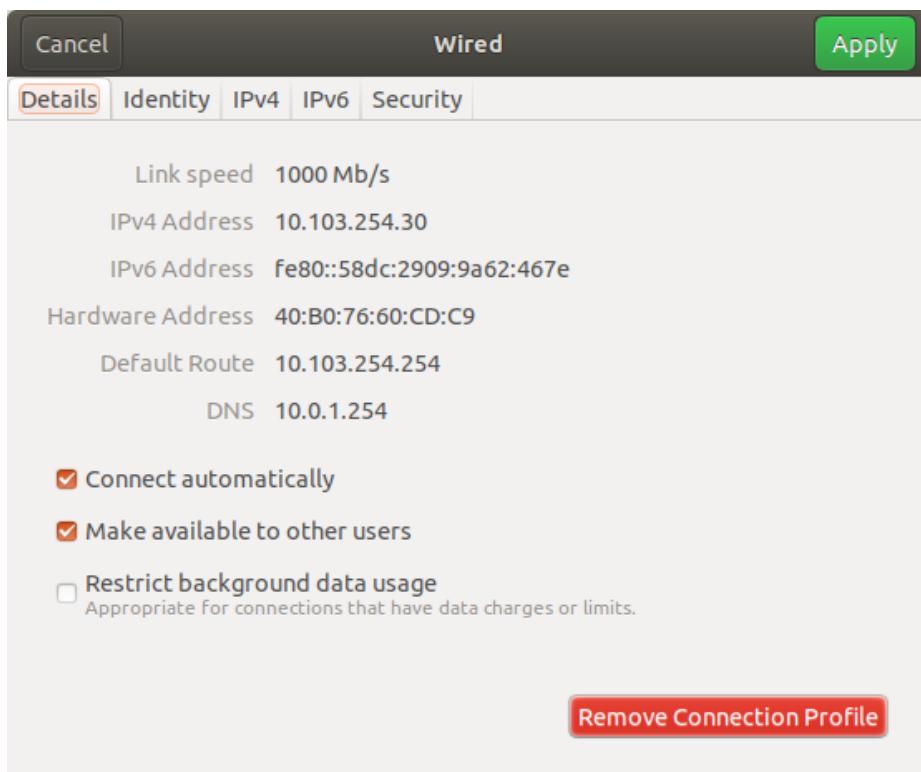

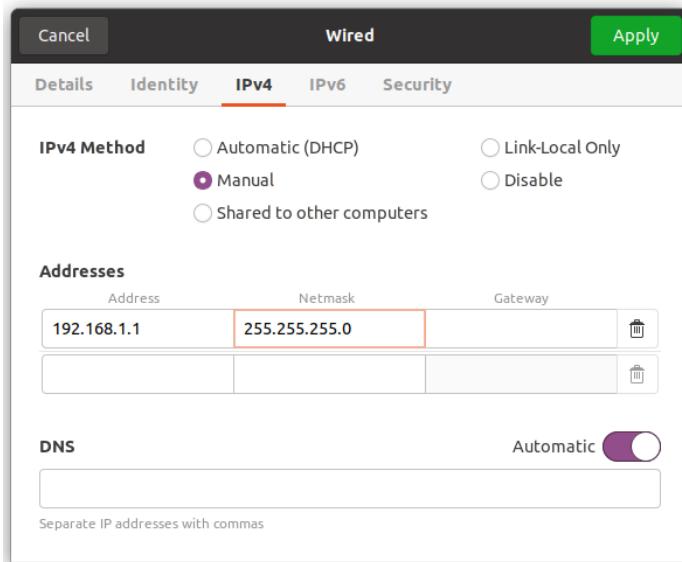

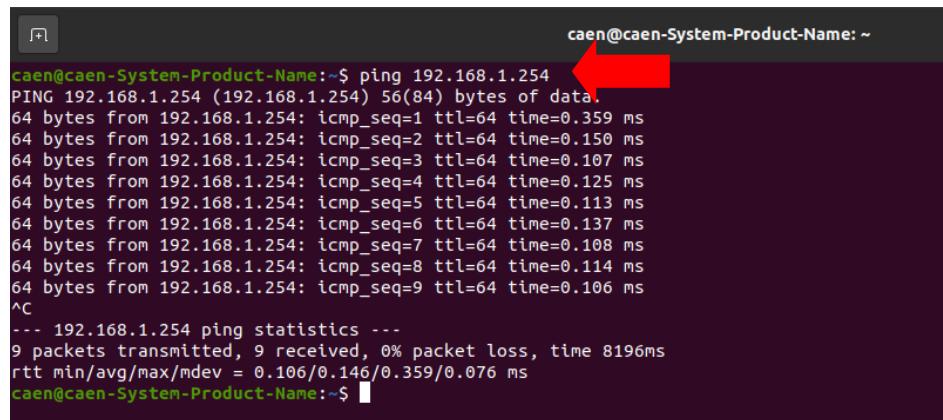

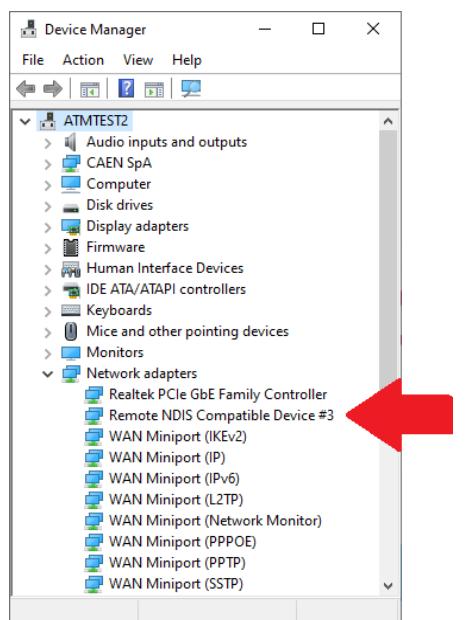

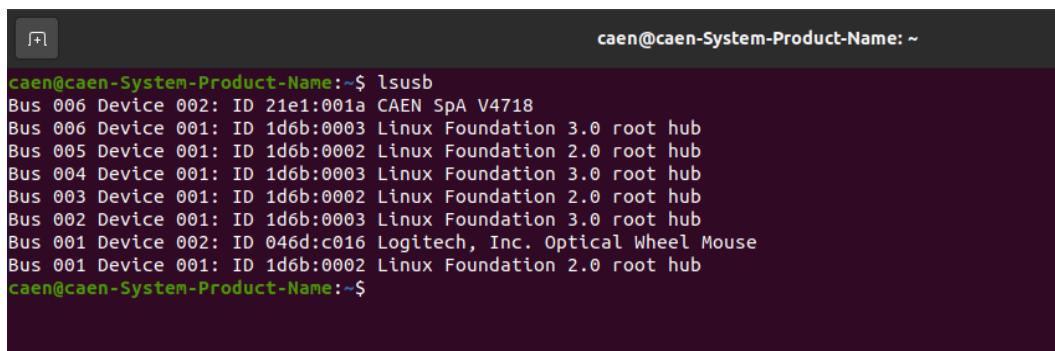

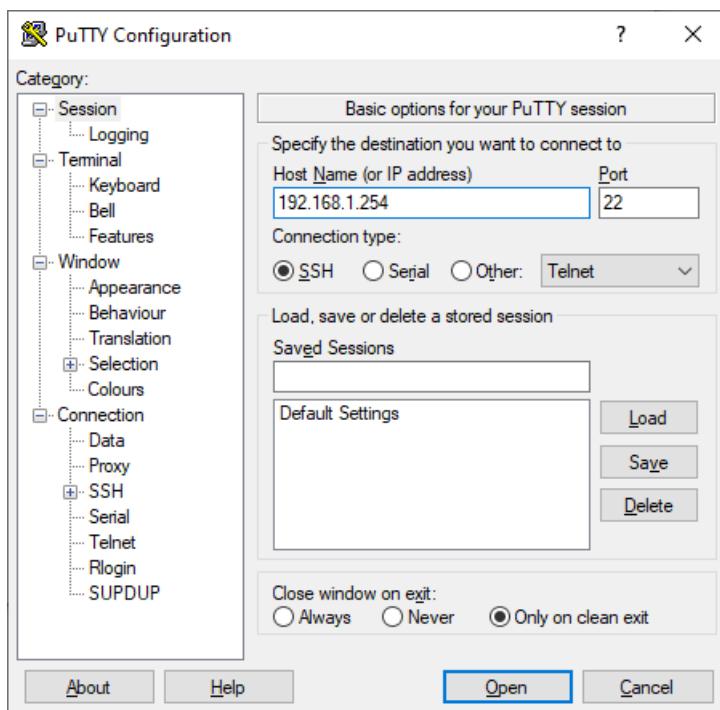

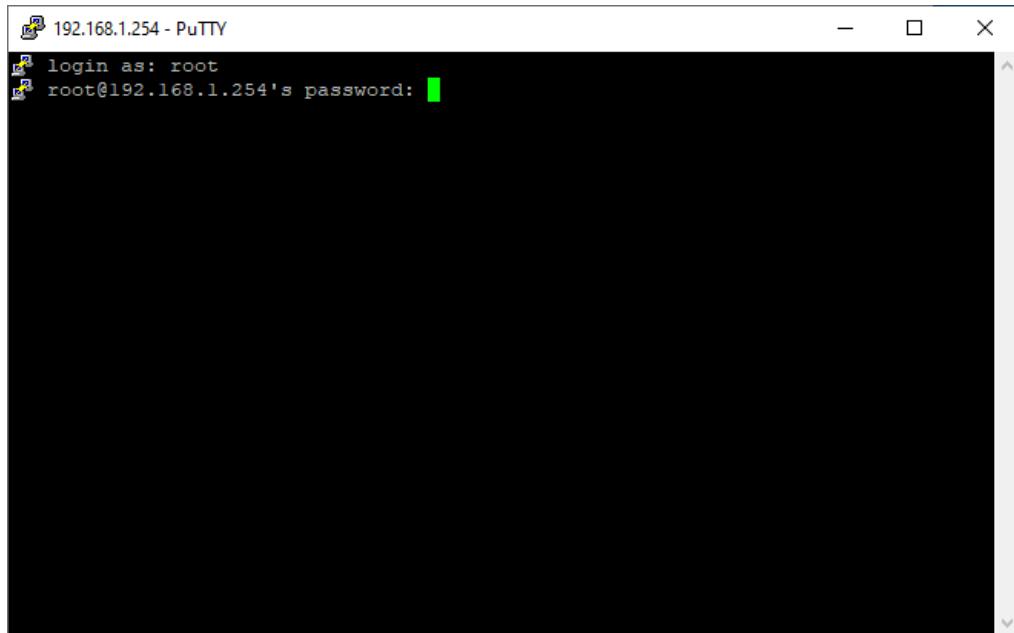

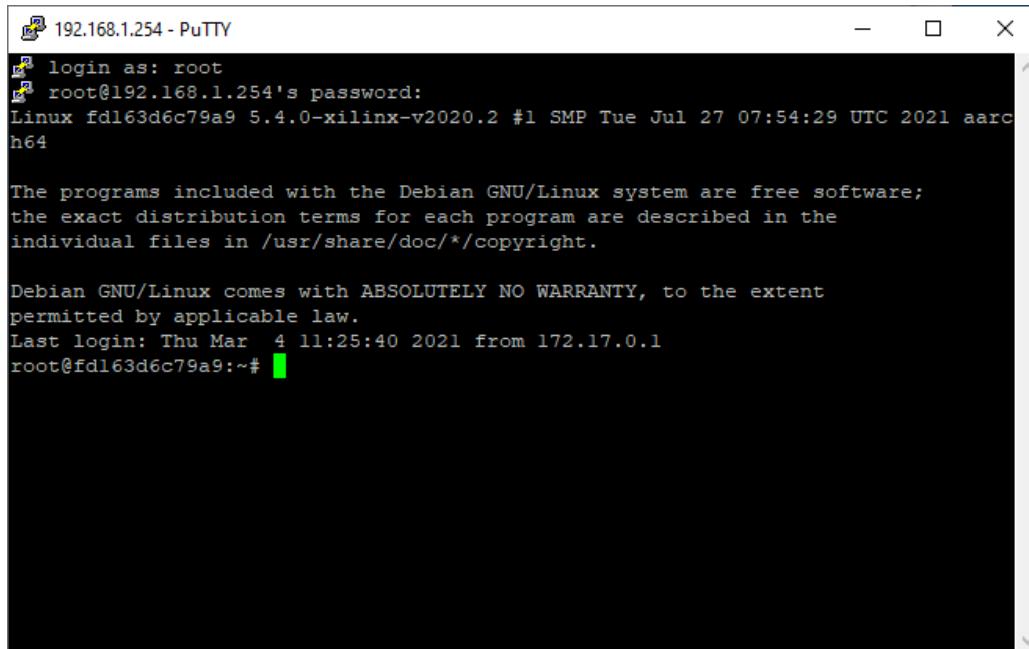

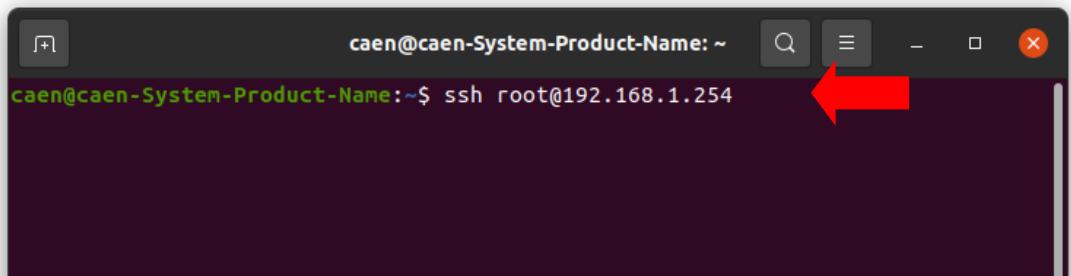

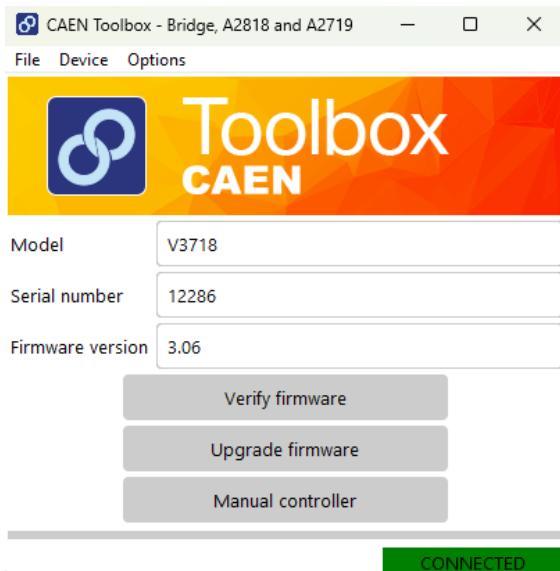

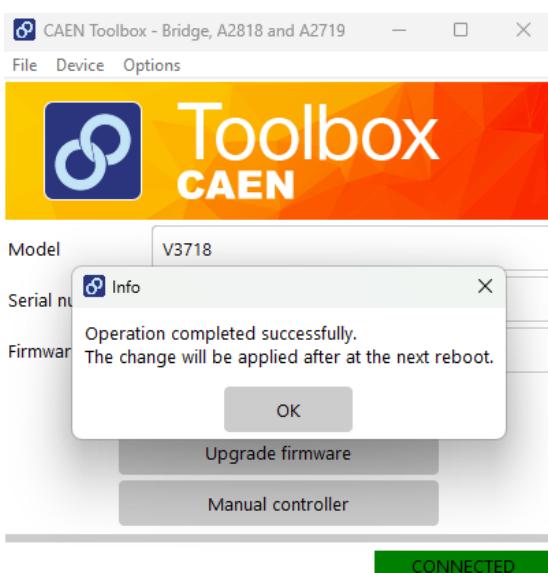

| [11:8]  | OUT2 function:<br>0000 = Data Strobe signal<br>0001 = Address Strobe signal<br>0010 = Data Acknowledge signal ( <i>default</i> )<br>0011 = Bus Error signal<br>0100 = Coincidence signal<br>0101 = Pulser A Output<br>0110 = Pulser B Output<br>0111 = Counter End Gate signal<br>1000 = Location Monitor signal<br>1001 = Register Set Status value<br>1010 = Device Grant VME bus signal<br>Others = <i>reserved</i> (OUT2 is set at 0) |