# Register your device

Register your device to your **MyCAEN+** account and get access to our customer services, such as notification for new firmware or software upgrade, tracking service procedures or open a ticket for assistance. **MyCAEN+** accounts have a dedicated support service for their registered products. A set of basic information can be shared with the operator, speeding up the troubleshooting process and improving the efficiency of the support interactions.

**MyCAEN+** dashboard is designed to offer you a direct access to all our after sales services. Registration is totally free, to create an account go to <https://www.caen.it/become-mycaenplus-user> and fill the registration form with your data.

1

create a MyCAEN+ account

2

register your devices

3

get support and more!

<https://www.caen.it/become-mycaenplus-user/>

# Purpose of this User Manual

This User Manual contains the full description of the DT5550 32-Channels Programmable Readout System and a brief guide to the SCI-55X0 Readout Software.

## Change Document Record

| Date                            | Revision | Changes                                                              |

|---------------------------------|----------|----------------------------------------------------------------------|

| August 31 <sup>st</sup> , 2018  | 00       | Initial release                                                      |

| February 6 <sup>th</sup> , 2019 | 01       | Modified <b>Settings Tab</b> Sec. and <b>Technical Support</b> Chap. |

| June 5th, 2020                  | 02       | Revised Chap. <b>SCI-55X0 Readout Software</b>                       |

## Symbols, abbreviated terms and notation

|      |                               |

|------|-------------------------------|

| ADC  | Analog to Digital Converter   |

| FPGA | Field Programmable Gate Array |

| OS   | Operating system              |

## Reference Document

---

- [RD1] GD6520 - SCI-Compiler Quick Start Guide

- [RD2] UM6519 - SCI-Compiler User Manual

- [RD3] DS6521 – DT5550AFE Datasheet

---

CAEN S.p.A.

Via Vetraia, 11 55049 Viareggio (LU) - ITALY

Tel. +39.0584.388.398 Fax +39.0584.388.959

info@caen.it

www.caen.it

© CAEN SpA – 2020

### Disclaimer

No part of this manual may be reproduced in any form or by any means, electronic, mechanical, recording, or otherwise, without the prior written permission of CAEN spa.

The information contained herein has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. CAEN spa reserves the right to modify its products specifications without giving any notice; for up to date information please visit [www.caen.it](http://www.caen.it).

**MADE IN ITALY:** We remark that all our boards have been designed and assembled in Italy. In a challenging environment where a competitive edge is often obtained at the cost of lower wages and declining working conditions, we proudly acknowledge that all those who participated in the production and distribution process of our devices were reasonably paid and worked in a safe environment (this is true for the boards marked "MADE IN ITALY", while we cannot guarantee for third-party manufacturers).

---

# Index

|                                                                  |           |

|------------------------------------------------------------------|-----------|

| <b>Purpose of this User Manual .....</b>                         | <b>2</b>  |

| <b>Change Document Record .....</b>                              | <b>2</b>  |

| <b>Symbols, abbreviated terms and notation .....</b>             | <b>2</b>  |

| <b>Reference Document .....</b>                                  | <b>2</b>  |

| <b>Index .....</b>                                               | <b>3</b>  |

| <b>List of Figures .....</b>                                     | <b>4</b>  |

| <b>List of Tables .....</b>                                      | <b>4</b>  |

| <b>1 Introduction .....</b>                                      | <b>5</b>  |

| <b>2 Block Diagram .....</b>                                     | <b>6</b>  |

| <b>3 Technical Specifications .....</b>                          | <b>7</b>  |

| <b>4 Packaging and compliancy .....</b>                          | <b>8</b>  |

| SCI-Compiler License .....                                       | 9         |

| <b>5 Power Requirements .....</b>                                | <b>10</b> |

| <b>6 Safety Notices .....</b>                                    | <b>11</b> |

| <b>7 Cooling Management .....</b>                                | <b>12</b> |

| <b>8 Panels Description .....</b>                                | <b>13</b> |

| Front Panel .....                                                | 14        |

| Rear Panel .....                                                 | 15        |

| <b>9 Functional Description .....</b>                            | <b>17</b> |

| <b>Analog Input Stage .....</b>                                  | <b>17</b> |

| Differential Signal Input .....                                  | 18        |

| DT5550AFE: Single-Ended to Differential conversion .....         | 19        |

| Active Single-Ended to Differential conversion .....             | 19        |

| AC-coupled passive Single-Ended to Differential conversion ..... | 20        |

| DC-coupled passive Single-Ended to Differential conversion ..... | 21        |

| <b>Digital Input Stage .....</b>                                 | <b>22</b> |

| <b>Clock Distribution .....</b>                                  | <b>23</b> |

| <b>10 Drivers &amp; Libraries .....</b>                          | <b>24</b> |

| <b>11 Firmware and Upgrade .....</b>                             | <b>25</b> |

| <b>Firmware Framework Structure .....</b>                        | <b>25</b> |

| <b>Firmware design: the processing core .....</b>                | <b>25</b> |

| <b>Default firmware for DT5550 .....</b>                         | <b>26</b> |

| Charge integration .....                                         | 26        |

| Waveform recording .....                                         | 29        |

| Imaging module .....                                             | 30        |

| <b>Firmware Upgrade .....</b>                                    | <b>32</b> |

| <b>12 SCI-55X0 Readout Software .....</b>                        | <b>34</b> |

| <b>Software installation .....</b>                               | <b>34</b> |

| <b>Board connection .....</b>                                    | <b>36</b> |

| <b>Software GUI Description .....</b>                            | <b>37</b> |

| Control Bar .....                                                | 38        |

| Settings Tab .....                                               | 38        |

| Oscilloscope Tab .....                                           | 41        |

| Spectrum Tab .....                                               | 42        |

| Imaging Module .....                                             | 44        |

| <b>How to Perform a Fit .....</b>                                | <b>44</b> |

| <b>How to Save Data .....</b>                                    | <b>45</b> |

| <b>13 Technical Support .....</b>                                | <b>47</b> |

## List of Figures

|                                                                                                                                        |    |

|----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1: DT5550 block diagram.....                                                                                                  | 6  |

| Figure 4.1: general view of the DT5550.....                                                                                            | 8  |

| Figure 4.2: USB cables included in the delivered kit.....                                                                              | 8  |

| Figure 4.3: SCI-Compiler USB Dongle and keys for license activation.....                                                               | 9  |

| Figure 5.1: AC/DC power supply wall adapter provided with the module.....                                                              | 10 |

| Figure 8.1: Front panel view.....                                                                                                      | 13 |

| Figure 8.2: Rear panel view .....                                                                                                      | 13 |

| Figure 9.1: front panel analog connector pinout.....                                                                                   | 17 |

| Figure 9.2: scheme of the analog input stage.....                                                                                      | 18 |

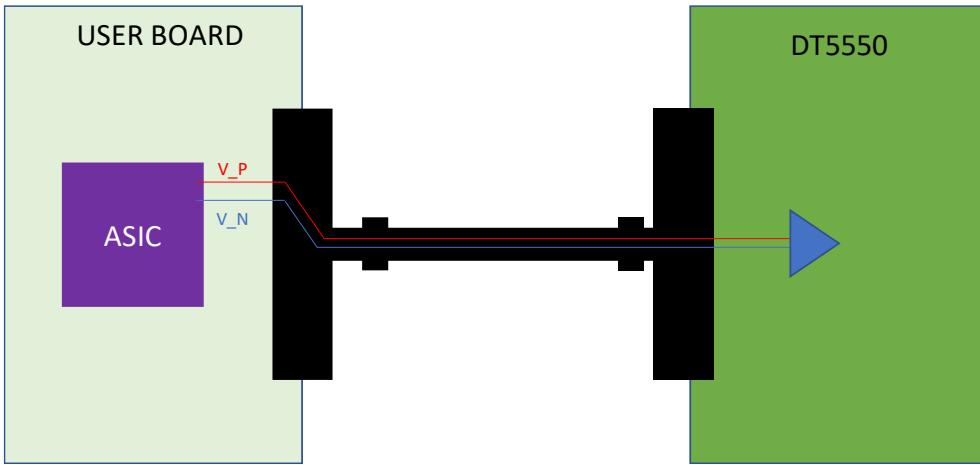

| Figure 9.3: connection of differential outputs of an ASIC to the DT5550. ....                                                          | 19 |

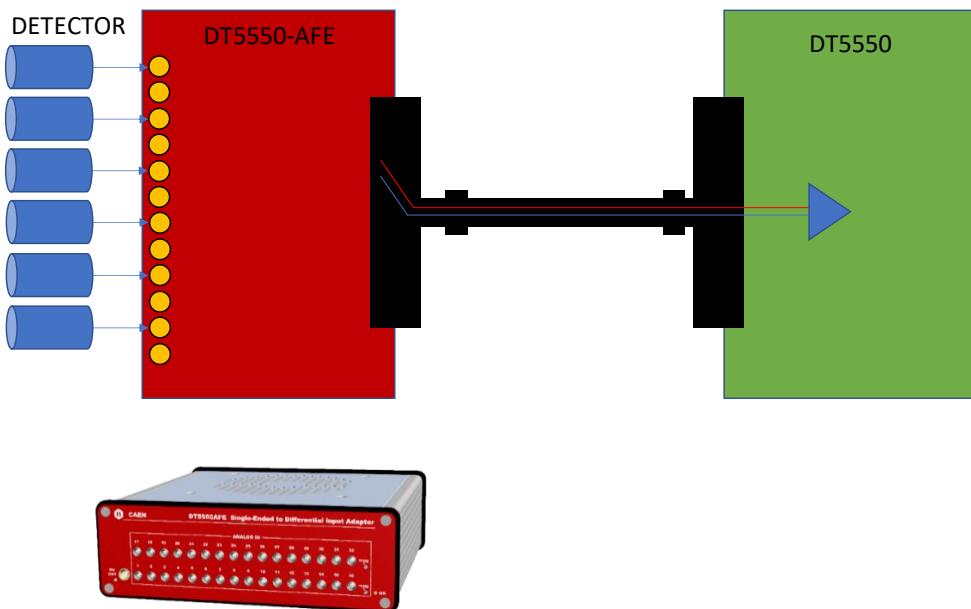

| Figure 9.4: connection of single-ended signals using the DT5550AFE.....                                                                | 19 |

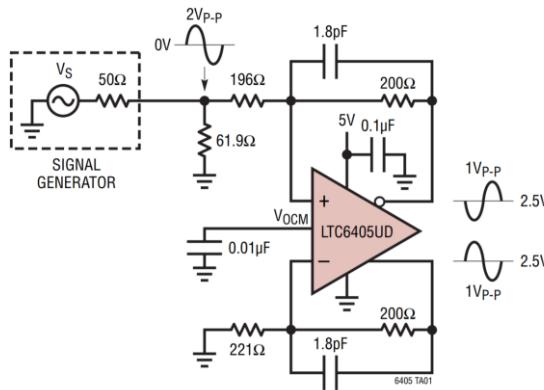

| Figure 9.5: connection of single-ended signals using an active single-ended to differential conversion.....                            | 20 |

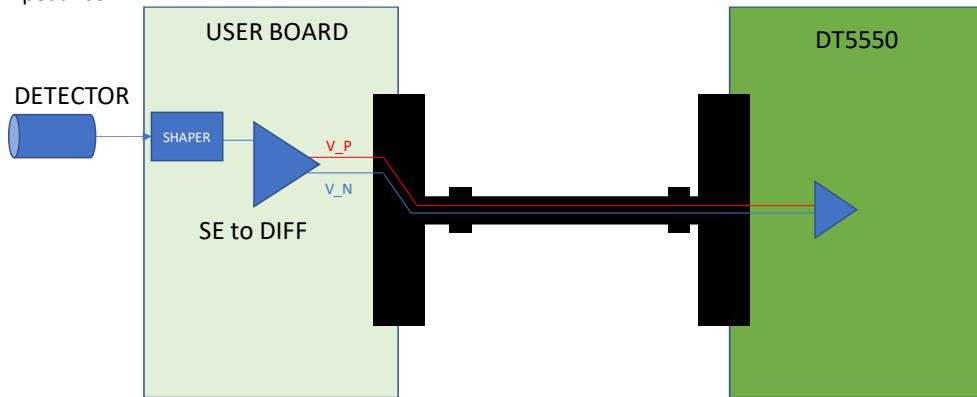

| Figure 9.6: connection of single-ended signals using an AC-coupled passive single-ended to differential conversion. ....               | 20 |

| Figure 9.7: connection of single-ended signals using a passive single-ended to differential conversion. ....                           | 21 |

| Figure 9.8: connection of single-ended signals using a passive single-ended to differential conversion and grounding optimization..... | 21 |

| Figure 9.9: pinout of the digital connectors of the DT5550. ....                                                                       | 22 |

| Figure 9.10: DT5550 voltage selector switch for digital I/Os.....                                                                      | 22 |

| Figure 9.11: scheme of the clock distribution on the DT5550.....                                                                       | 23 |

| Figure 10.1: the Windows Device Manager showing up the DT5550 as FTI FT601 USB3.0 Bridge Device.....                                   | 24 |

| Figure 11.1: scheme of the default firmware for the DT5550. ....                                                                       | 26 |

| Figure 11.2: Firmware hierachic structure in SCI-Compiler.....                                                                         | 27 |

| Figure 11.3: SCI-Compiler scheme for single channel data processing in the default firmware. ....                                      | 27 |

| Figure 11.4: SCI-Compiler scheme of the whole charge integration process for a channel of the DT5550.....                              | 28 |

| Figure 11.5: scheme of the oscilloscope module available in the default firmware for the DT5550. ....                                  | 29 |

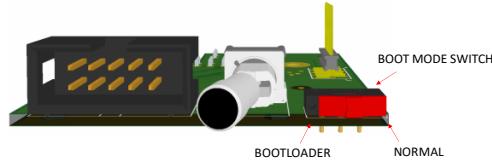

| Figure 11.6: DT5550 Boot Mode Switch positions. ....                                                                                   | 32 |

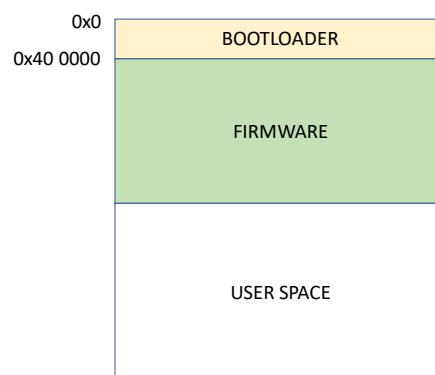

| Figure 11.7: scheme of the DT5550 FPGA memory usage. ....                                                                              | 32 |

| Figure 12.1: the "Connection" window at startup of the SCI-55X0 Readout Software .....                                                 | 37 |

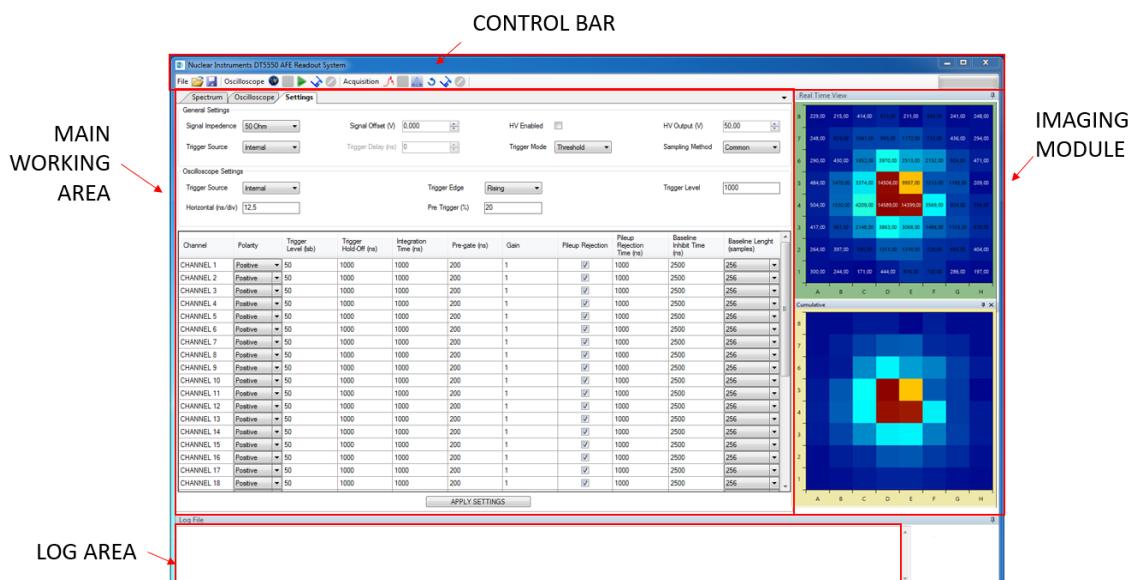

| Figure 12.2: the main window of the SCI-55X0 Readout Software. The main areas are highlighted.....                                     | 37 |

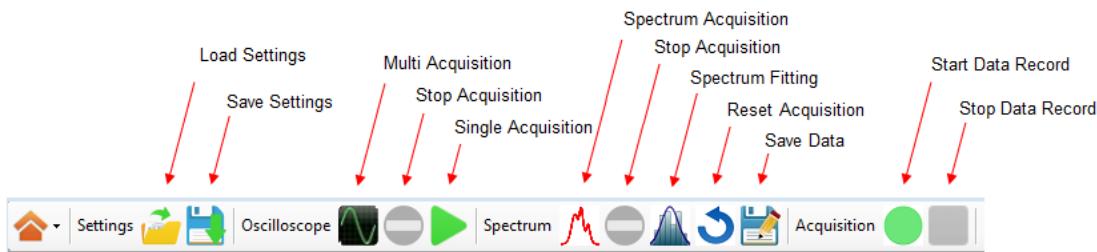

| Figure 12.3: the Control Bar of the SCI-55X0 Readout Software.....                                                                     | 38 |

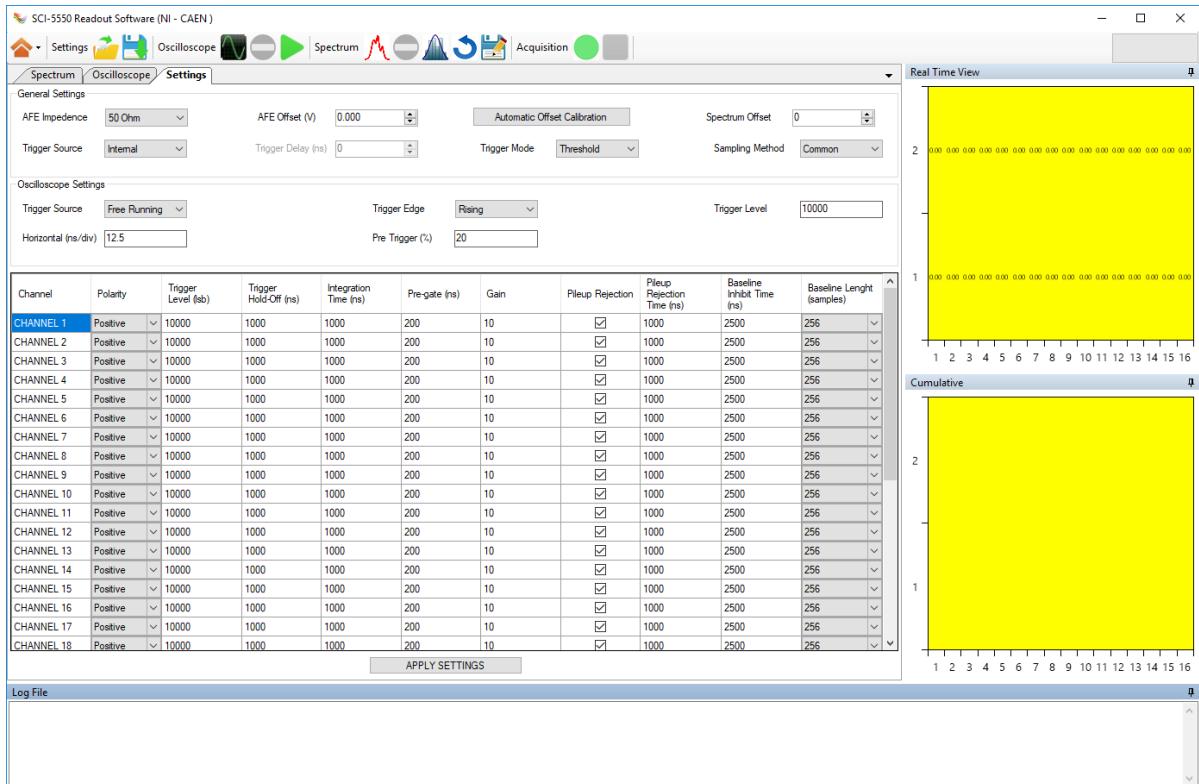

| Figure 12.4: the Settings Tab of the SCI-55X0 Readout Software.....                                                                    | 39 |

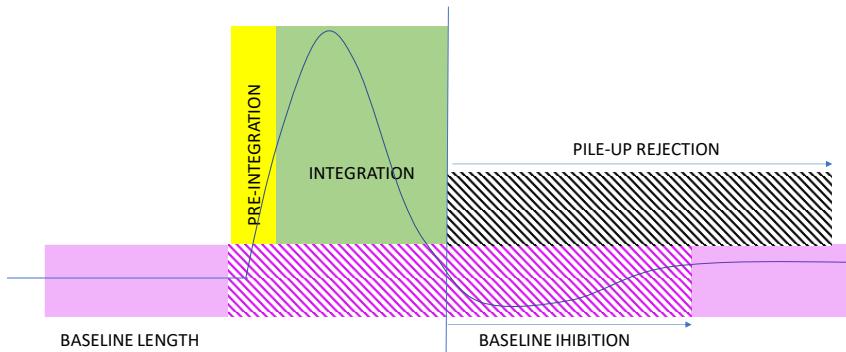

| Figure 12.5: scheme of the charge integration firmware parameters to be set in the SCI-55X0 Readout Software. ....                     | 41 |

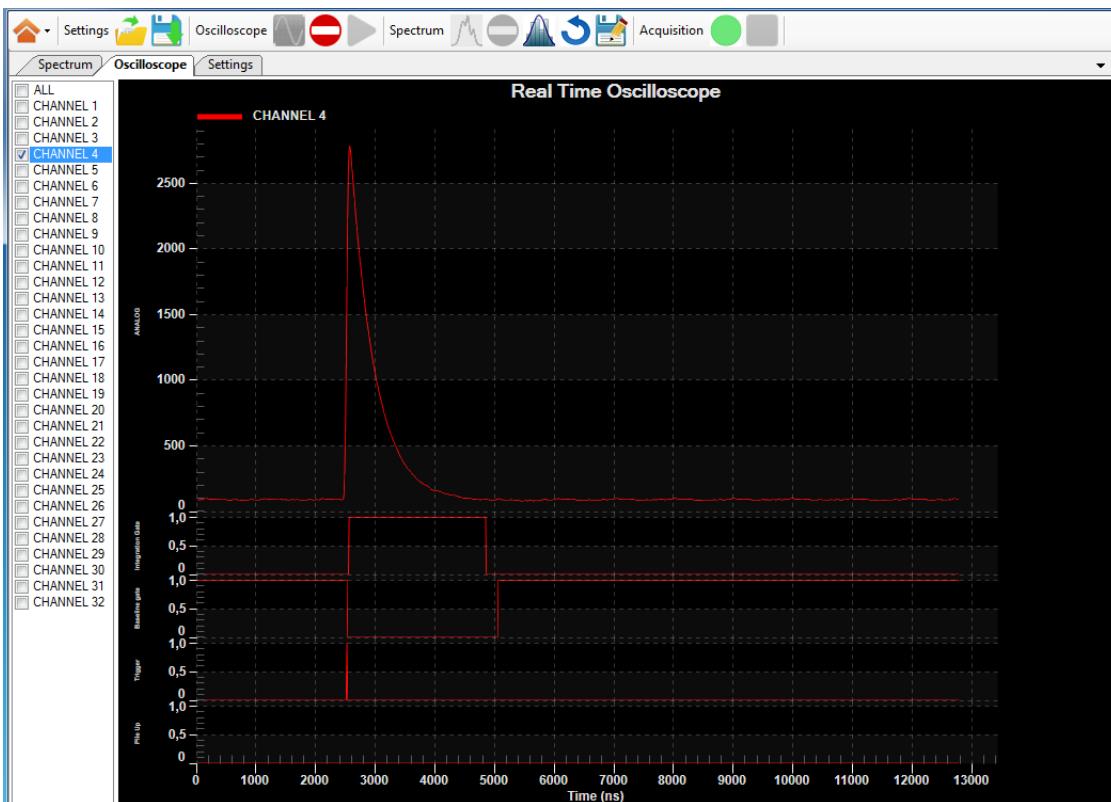

| Figure 12.6: the Oscilloscope Tab of the SCI-55X0 Readout Software. Here only signals for channel 4 are displayed.....                 | 42 |

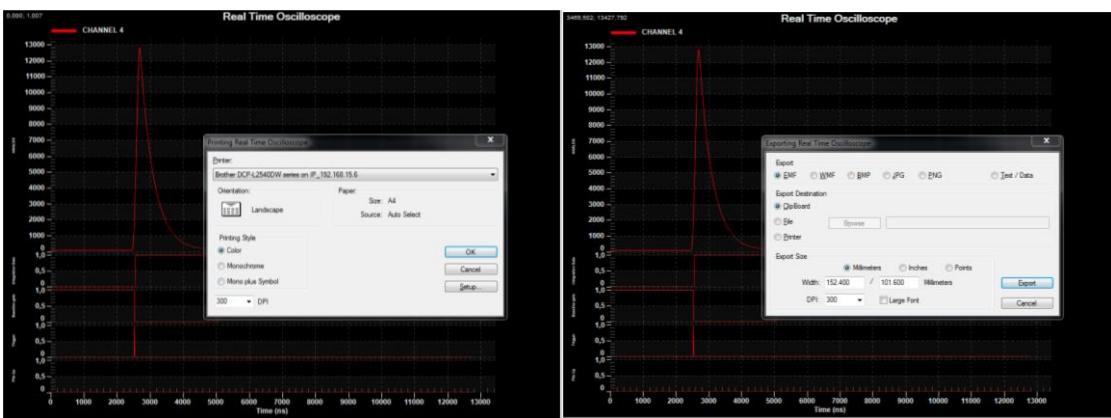

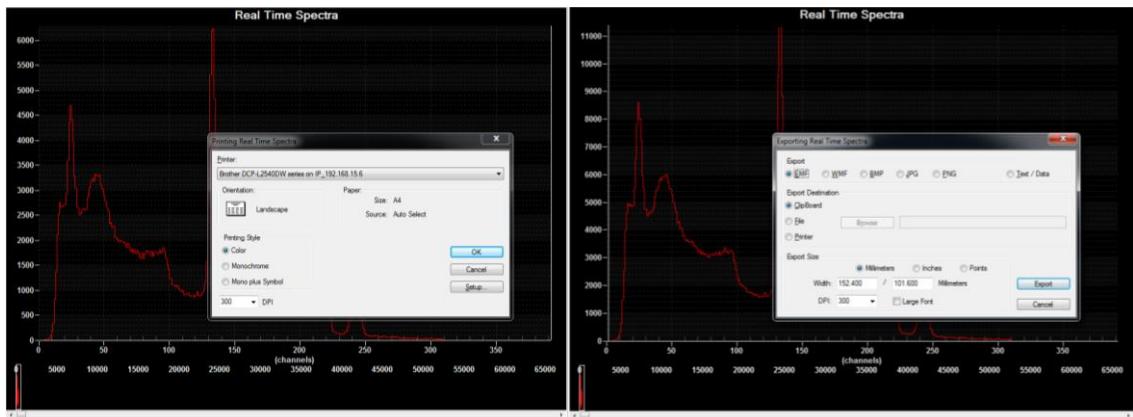

| Figure 12.7: printing (left) and saving to file (right) the current view of the Oscilloscope Tab .....                                 | 42 |

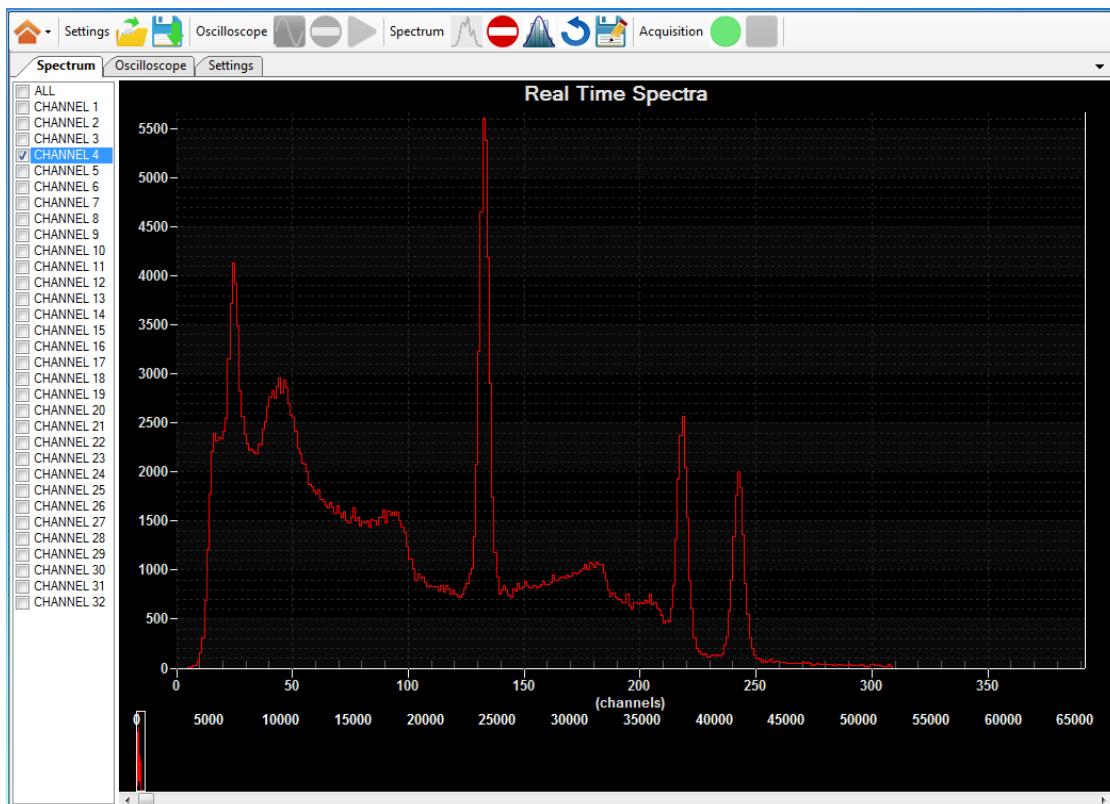

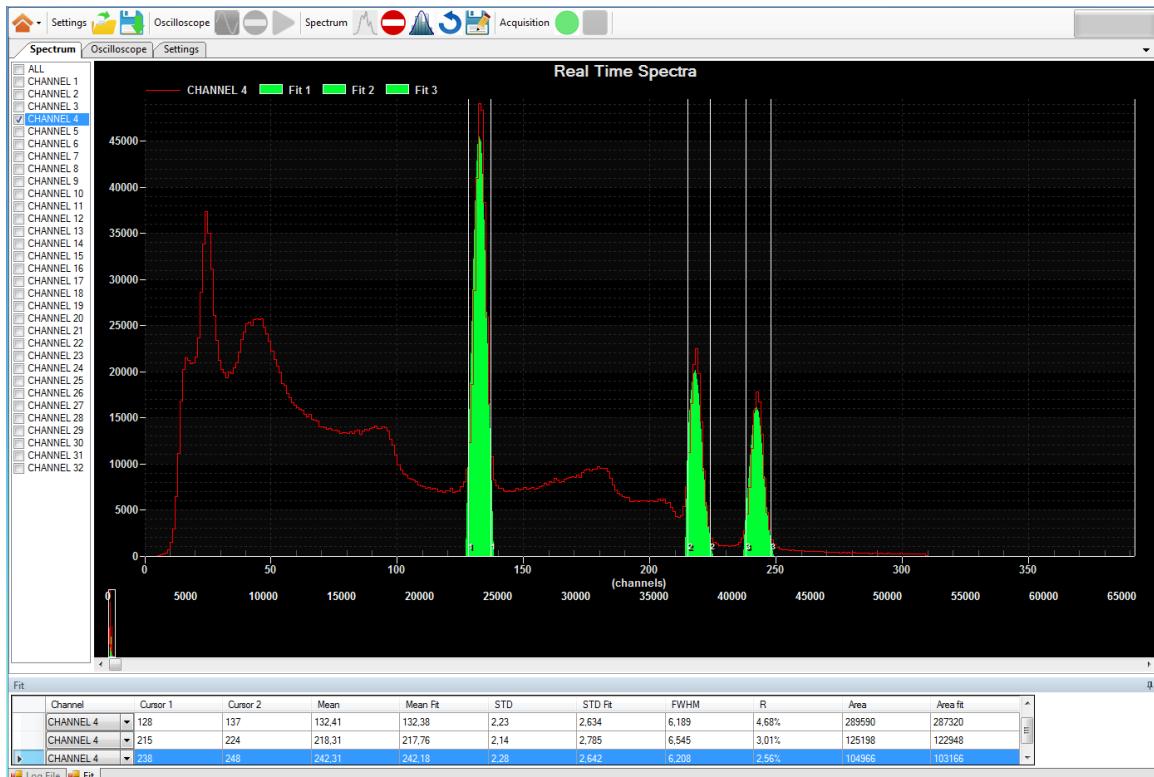

| Figure 12.8: the Spectrum Tab of the SCI-55X0 Readout Software. Here only the spectrum for channel 4 is displayed.....                 | 43 |

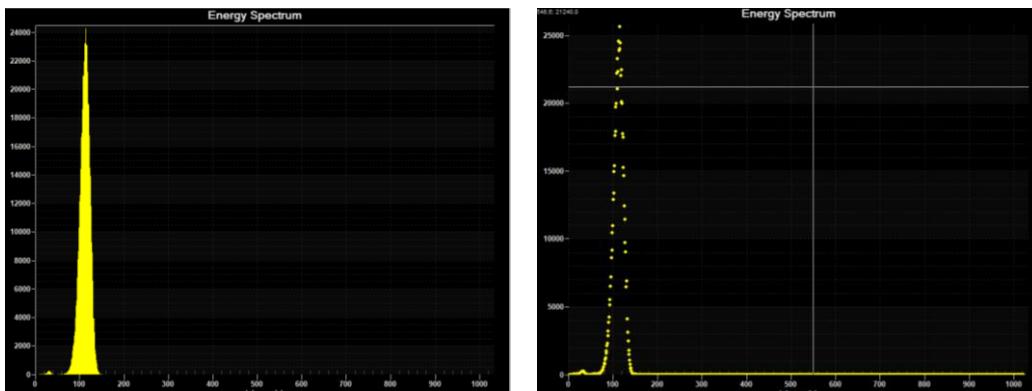

| Figure 12.9: spectra shown in different plot modes (left = Area, right = Dot). ....                                                    | 44 |

| Figure 12.10: printing (left) and saving to file (right) the current view of the Spectrum Tab.....                                     | 44 |

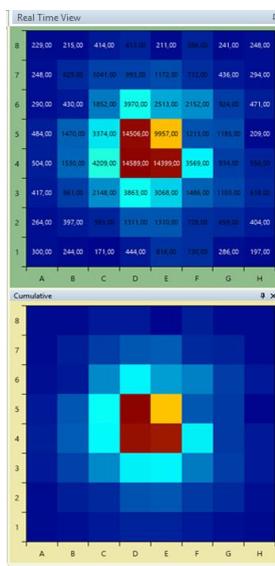

| Figure 12.11: the Imaging Module of the SCI-55X0 Readout Software.....                                                                 | 44 |

| Figure 12.12: the fitting tool of the SCI-55X0 Readout Software. ....                                                                  | 45 |

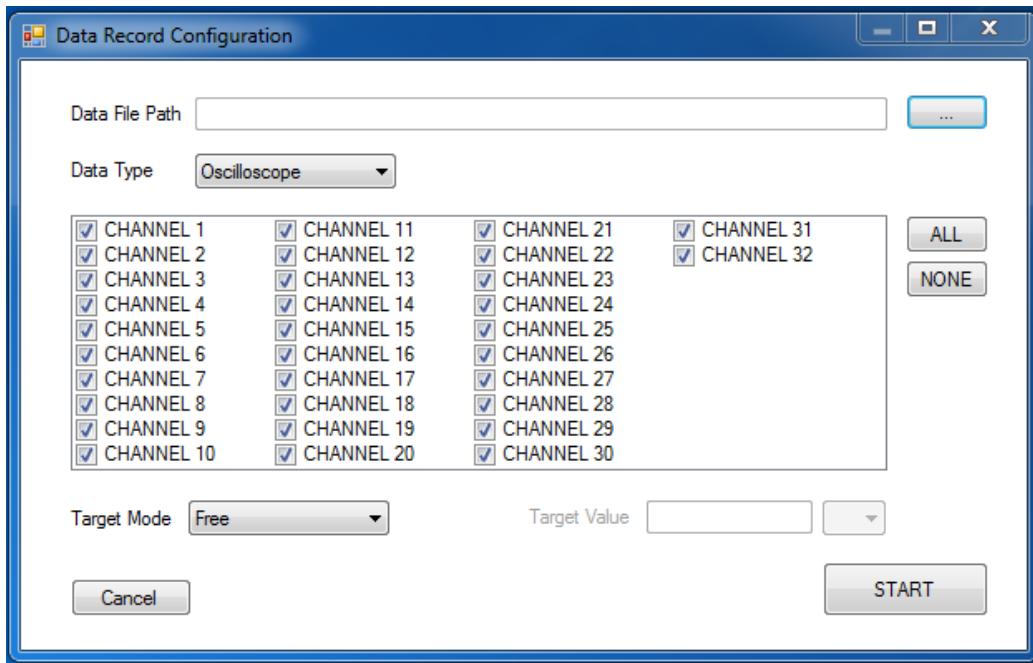

| Figure 12.13: the Data Record Configuration window.....                                                                                | 46 |

## List of Tables

|                                                                        |    |

|------------------------------------------------------------------------|----|

| Table 1.1: table of available board models and accessories. ....       | 5  |

| Table 3.1: technical specifications for the DT5550. ....               | 7  |

| Table 6.1: operating limits for DT5550 connectors. ....                | 11 |

| Table 9.1: differential parameters for the DT5550 analog input.....    | 18 |

| Table 11.1: registers description of the charge integrator module..... | 28 |

# 1 Introduction

The DT5550 is a **Programmable 32-channel Digital Acquisition System** for physics application. It is one of the CAEN programmable board designed to help users in building a customized acquisition system fitting the needs of their detectors and experimental conditions. The applications of the DT5550 range from nuclear spectroscopy to ASICs readout, from neutron physics to Silicon Photmultipliers detection systems. The firmware, the readout software and some design files are distributed for free and open source so that the user can easily customize them in order to implement a full and complex experimental readout system on a single board.

The DT5550 is capable to manage simultaneously a large number of **digital** and **analog** signals to implement many functionalities required by physics experiments: signal digitization, complex trigger logic, Pulse Height Analysis with MCA capabilities, Time Tagging, Pulse Shape Discrimination, Scaler, Counters and so on. The large number of digital I/O and analog inputs make the DT5550 a solution suitable to readout most of the ASICs commonly used in physic, allowing the user to minimize the effort in designing a readout system (only a simple adapter board between the ASIC and the DT5550 I/O connectors is needed). It is possible, for example, to use a DT5550 to readout up to 8 WeeROC Petiroc (analog readout) or up to 8 WeeROC Catiroc.

The DT5550 can be used for the following applications:

- Readout of the following detectors:

- HPGe, Segmented germanium detector

- Array/matrix of PMTs

- Multi anode PMTs

- Array/Matrix of SiPMs

- Position sensing detectors (for application like gamma camera) with realtime position reconstruction

- APD, SPAD, SiPIN and SDD

- Silicon detectors, CCD

- CdTE and CZT detector

- Neutron Detector ( $^3\text{He}$  tubes, position sensing tubes)

- Neutron scintillator detectors with Gamma Neutron discrimination

- Readout of mixed signals ASICs

- Nuclear Spectroscopy

- High Energy Physics

- Imaging with multichannel detectors

The DT5550 is fully supported by **SCI-Compiler**, a Windows-based graphical development system for **easy FPGA programming**. This tool allows to develop and compile the firmware code using graphical blocks which represents the functionalities needed for firmware implementation (for example oscilloscope, TDC, MCA, charge integration, etc). SCI-Compiler automatically generates the VHDL firmware code starting only from logic blocks and virtual instruments that can be connected together in the GUI and, moreover, it generates C/C++/C#/Python Libraries for custom software development in Windows, Linux, MacOS, Android OS (refer to [\[RD1\]](#) for more details).

A complete, ready to use default firmware is provided for free and open source. The default firmware manages the basic waveform digitization and charge integration and it is preloaded on the board. The user can open the default firmware in SCI-Compiler and modify it in order to customize, for example, the trigger logic, the data online processing or integrate it in a larger system.

The SCI-Compiler license and one-year upgrade is included with the DT5550.

The **SCI-55X0 Readout Software** is the free and open source Windows-based software developed to perform acquisitions with the DT5550. It works in conjunction with the DT5550 default firmware and it can be modified by the user according to the custom functions implemented in the firmware and for any other need.

Available board models and accessories are listed below.

| Board       | Description                                                      | Product Code |

|-------------|------------------------------------------------------------------|--------------|

| DT5550      | DT5550 – 32 ch DAQ System with Programmable FPGA and Sequencer   | WDT5550XAAAA |

| Accessories | Description                                                      | Product Code |

| DT5550AFE   | DT5550AFE –Single-Ended to Differential Input Adapter for DT5550 | WDT5550AFEXA |

**Table 1.1:** table of available board models and accessories.

## 2 Block Diagram

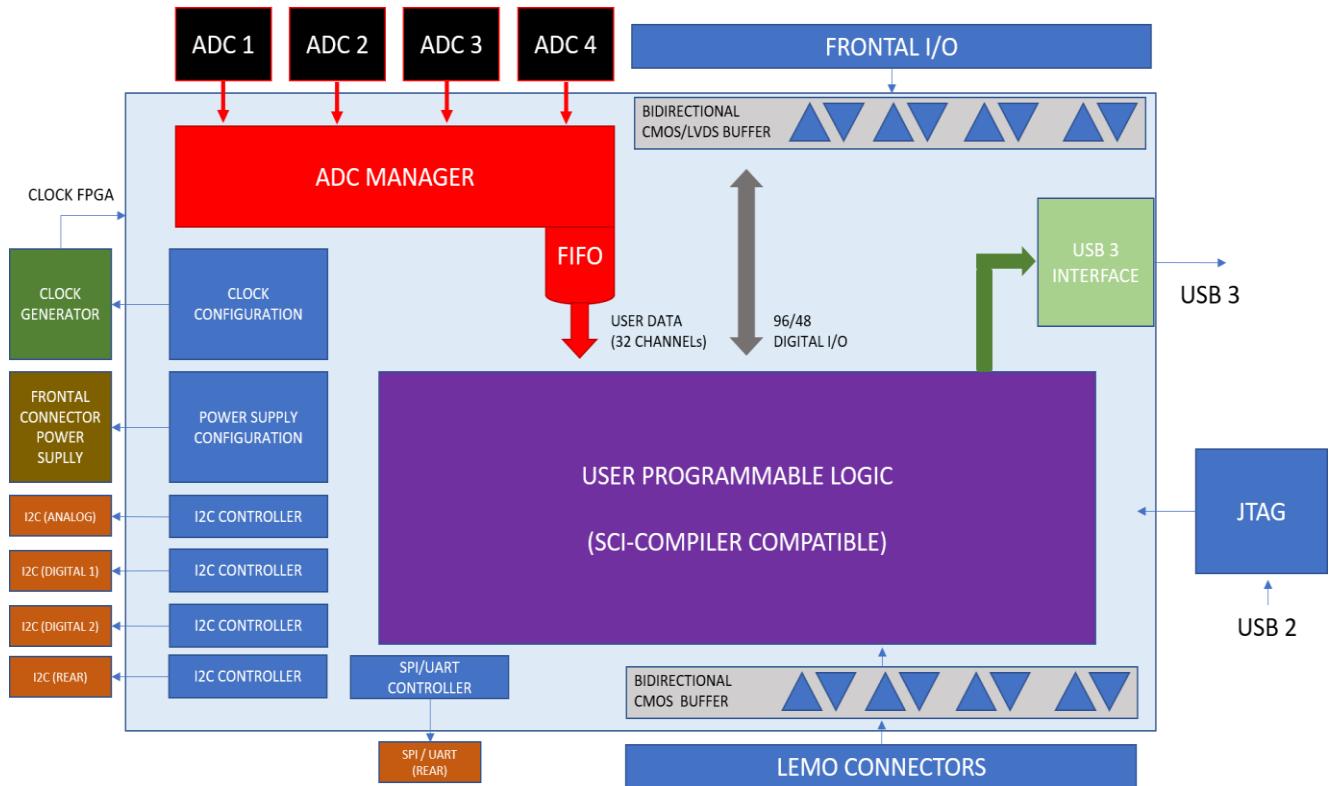

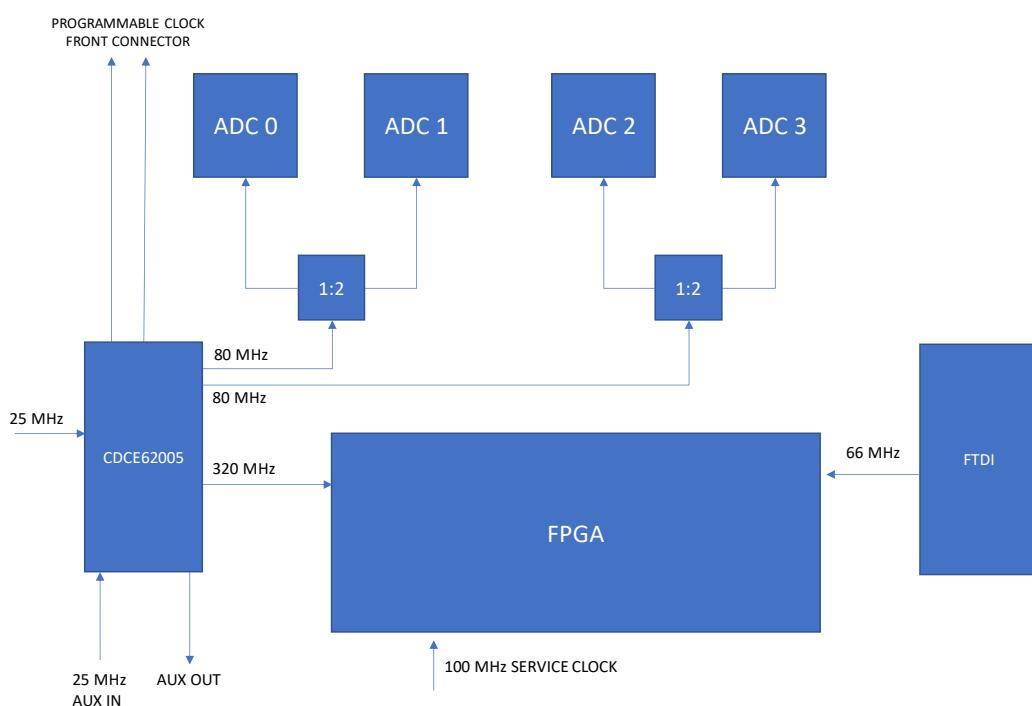

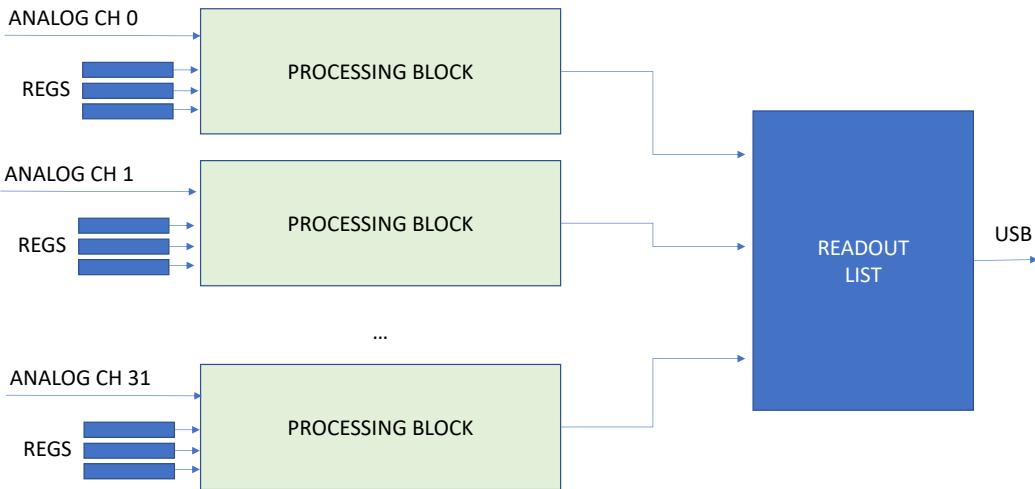

**Figure 2.1:** DT5550 block diagram.

# 3 Technical Specifications

|                                |                                                                                                                                                                                                          |                                                                                                                                                       |                                                                                                              |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| <b>GENERAL</b>                 | <b>Form Factor</b> 163x50x226 mm <sup>3</sup> (WxHxD) Desktop                                                                                                                                            |                                                                                                                                                       |                                                                                                              |

| <b>POWER CONSUMPTION</b>       | 2 A @ 12 V (Typ.)                                                                                                                                                                                        |                                                                                                                                                       |                                                                                                              |

| <b>ANALOG INPUT</b>            | <b>Channels</b><br>32 channels<br>Differential                                                                                                                                                           | <b>Connector</b><br>VHDCI                                                                                                                             | <b>Bandwidth</b><br>31 MHz                                                                                   |

|                                | <b>Impedance</b><br>$Z_{\text{diff}} = 100 \Omega$                                                                                                                                                       | <b>Full Scale Range</b><br>2 V <sub>pp</sub>                                                                                                          |                                                                                                              |

| <b>DIGITAL INPUT</b>           | <b>Channels</b><br>2 x 24 channels<br>Differential                                                                                                                                                       | <b>Connector</b><br>2 x VHDCI                                                                                                                         | <b>Signal Type</b><br>CMOS 3.3V<br>LVCMS 1.8V<br>LVDS<br>BLVDS                                               |

|                                | <b>Impedance</b><br>$Z_{\text{diff}} = 100 \Omega$                                                                                                                                                       | <b>Coupling</b><br>AC                                                                                                                                 |                                                                                                              |

| <b>DIGITAL CONVERSION</b>      | <b>Resolution</b><br>14 bits                                                                                                                                                                             | <b>Sampling Rate</b><br>80 MS/s Simultaneously on each channel                                                                                        |                                                                                                              |

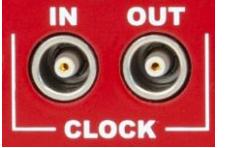

| <b>CLOCK GENERATION</b>        | Clock source: internal/external<br>On-board programmable PLL provides generation of the main board clocks from an internal (25 MHz local Oscillator) or external (rear panel CLK-IN connector) reference |                                                                                                                                                       |                                                                                                              |

| <b>LEMO DIGITAL I/O</b>        | <b>CLOCK-IN (LEMO)</b><br>$Z_{\text{in}} = 50 \Omega$<br>Single-ended, 25 MHz, 3.3V                                                                                                                      | <b>GPIO 1..8 (LEMO)</b><br>General purpose programmable digital I/Os<br>Single-ended, $Z_{\text{in}} / R_{\text{t}} = 50 \Omega$                      |                                                                                                              |

|                                | <b>CLOCK-OUT (LEMO)</b><br>$R_{\text{t}} = 50 \Omega$<br>Single-ended, 25 MHz, 3.3V, 50mA                                                                                                                |                                                                                                                                                       |                                                                                                              |

| <b>MEMORY</b>                  | 16 kS/ch                                                                                                                                                                                                 |                                                                                                                                                       |                                                                                                              |

| <b>TRIGGER</b>                 | <b>Trigger Source</b><br><i>Internal/External</i> : managed by the default firmware<br><i>Complex trigger logic</i> : implementable by the user on the open FPGA                                         | <b>Trigger Propagation</b><br>Through programmable LEMO GPIO 1...8                                                                                    |                                                                                                              |

|                                |                                                                                                                                                                                                          | <b>Trigger Time Stamp</b><br><i>Default FW</i> : 32-bit counter, 12.5 ns resolution, 50 s range;<br><i>Custom FW</i> : defined by the firmware design |                                                                                                              |

| <b>SYNCHRONIZATION</b>         | <b>Clock Propagation</b><br>LEMO CLOCK IN/OUT connectors                                                                                                                                                 | <b>Acquisition Synchronization</b><br>Through programmable LEMO GPIO 1...8                                                                            |                                                                                                              |

| <b>FPGA</b>                    | <b>Open FPGA</b><br>Xilinx XC7K160T (Kintex-7 family)                                                                                                                                                    |                                                                                                                                                       |                                                                                                              |

| <b>COMMUNICATION INTERFACE</b> | <b>USB 3.0</b><br>USB 2.0 back compatibility<br>Up to 240 MB/s transfer rate                                                                                                                             |                                                                                                                                                       |                                                                                                              |

| <b>FIRMWARE</b>                | <b>Default</b><br>Waveform recording and Charge Integration                                                                                                                                              | <b>Custom</b><br>Use SCI-Compiler to develop your own firmware!                                                                                       |  <b>LICENSE INCLUDED</b> |

| <b>FIRMWARE UPGRADE</b>        | Firmware can be upgraded via USB 3.0 or mini-USB debugger (on-fly)                                                                                                                                       |                                                                                                                                                       |                                                                                                              |

| <b>SOFTWARE</b>                | <ul style="list-style-type: none"> <li>- <b>SCI-55X0 Readout Software</b> to manage the default firmware</li> <li>- <b>SCI-Compiler</b> for custom firmware development</li> </ul>                       |                                                                                                                                                       |                                                                                                              |

Table 3.1: technical specifications for the DT5550.

## 4 Packaging and compliancy

The DT5550 is a Desktop board housed in a 163x50x226 mm<sup>3</sup> (WxHxD) alloy box.

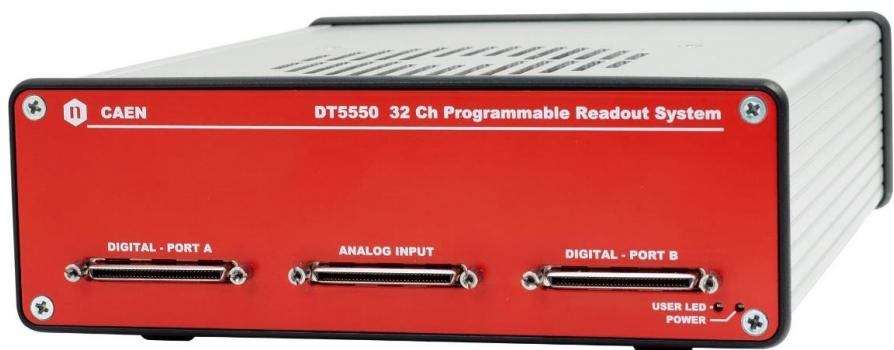

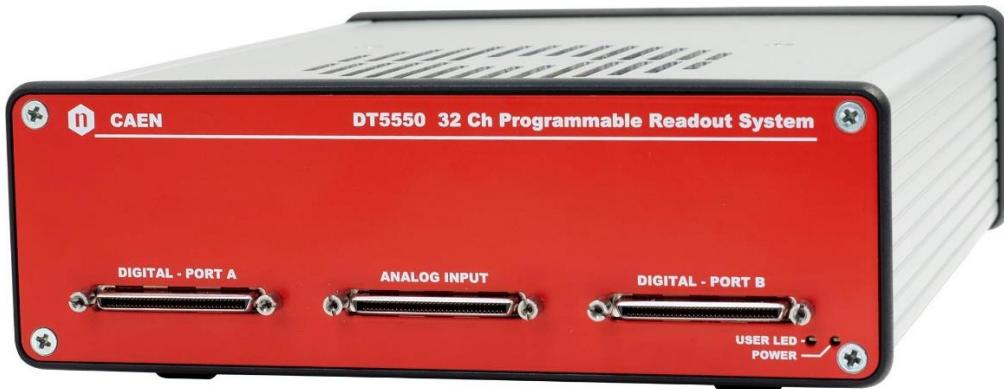

**Figure 4.1:** general view of the DT5550.

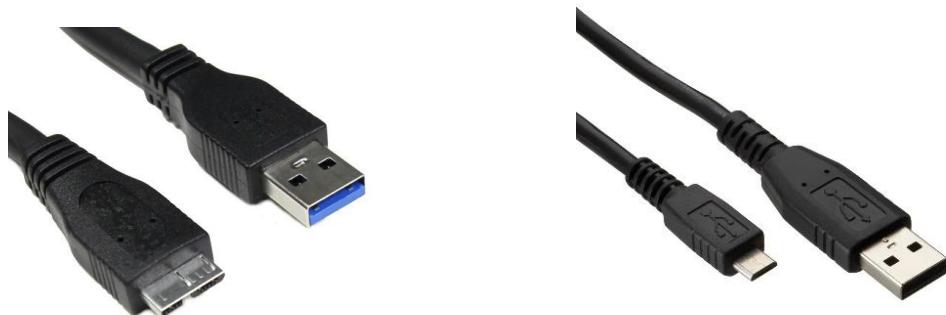

The user is equipped with a USB 3.0 communication cable and a micro-USB programmer cable for the FPGA.

**Figure 4.2:** USB cables included in the delivered kit.

**CAUTION:** to manage the product, consult the operating instructions provided.

**A POTENTIAL RISK EXISTS IF THE OPERATING INSTRUCTIONS ARE NOT FOLLOWED!**

CAEN provides the specific document “Precautions for Handling, Storage and Installation” available in the documentation tab of the product web page that the user is mandatory to read before to operate with CAEN equipment.

## SCI-Compiler License

Purchasing a DT5550, the user receives, included in the price, a full working license for SCI-Compiler, the CAEN **firmware generator** for **easy FPGA programming** developed in collaboration with Nuclear Instruments S.R.L.

SCI-Compiler full version works upon a license and a physical USB Dongle to be plugged in the PC during software usage. The license allows to use SCI-Compiler with no time limit, while the software upgrade is limited to a certain software release which is indicated while running SCI-Compiler. All the software releases, up to the last available for your license, are downloadable from [www.scicompiler.cloud](http://www.scicompiler.cloud).

The license provided with the DT5550 unlocks all the features of SCI-Compiler and includes **one year of free upgrade**.

**Note:** in order to extend your license for further upgrade, contact CAEN or [info@scicompiler.cloud](mailto:info@scicompiler.cloud)

**Note:** a trial version setup for evaluation is available for free on the CAEN website or at [www.scicompiler.cloud](http://www.scicompiler.cloud). It has no time limit but does not generate code and does not allow to save your design

Full version of SCI-Compiler is activated with the SERIAL NUMBER and an ACTIVATION key provided together with the USB Dongle.

**Figure 4.3:** SCI-Compiler USB Dongle and keys for license activation.

The user needs to create an account at [www.scicompiler.cloud](http://www.scicompiler.cloud) and add the serial number and activation key in the "MySciCompiler" area, in order to unlock the license and access the download area. Refer to [RD1] for more details.

**Note:** user is not allowed to use the code generated by the SCI-Compiler on boards different from DT5550. Using also a small part of the code generate by the SCI-Compiler on a custom design board or other products is an explicit violation of the license terms and it is an offense against CAEN S.P.A and Nuclear Instruments S.R.L.

## 5 Power Requirements

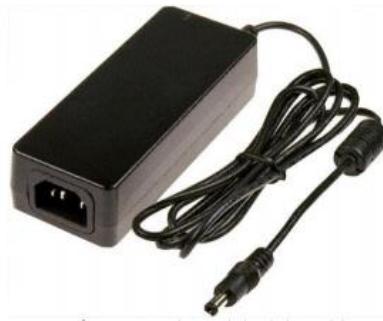

The DT5550 is powered by an external 220V-12V AC/DC stabilized power supply provided with the board and included in the delivered kit.

**Note:** using a different power supply source, like battery or linear type, it is recommended the source to provide +12 V and 2A; the power jack is a 2.1 mm type, a suitable cable is the RS 656-3816 type (or similar)

**WARNING:** the maximum operating voltage is 12.8V while the minimum is 9V.

**Figure 5.1:** AC/DC power supply wall adapter provided with the module.

# 6 Safety Notices

CAEN recommends to always operate the DT5550 within the following safe limits.

**WARNING:** the two digital front connector lines are directly connected to the FPGA I/Os. Violation in maximum absolute rating illustrated in this document will likely destroy the FPGA. There is no buffer or protection on this line. That is necessary because we want to preserve the possibility to operate at different voltages and with both single ended and differential signals: front Digital I/O can operate at 1.8 or 3.3V and can be configured as LVDS.

The following operating limits must be respected:

| Connector   | Net class                 | Unit                              | Min    | Max    |

|-------------|---------------------------|-----------------------------------|--------|--------|

| DC IN       | Power Supply              | Voltage                           | 9 V    | 13 V   |

| LEMO [all]  |                           | Voltage                           | -0.1 V | 3.6 V  |

| DIGITAL I/O | Digital 3.3V              | Voltage (3.3 V I/O bank selected) | 0 V    | 3.5 V  |

|             |                           | Current                           |        | 10 mA  |

|             | Digital 1.8V              | Voltage (1.8 V I/O bank selected) | 0 V    | 1.95 V |

|             |                           | Current                           |        | 10 mA  |

|             | LVDS                      | Voltage                           | 0.5 V  | 2.3 V  |

|             |                           | Current                           |        | 10 mA  |

|             |                           | Common Mode                       | 0.9 V  | 1.75 V |

|             | I2C/Serial                | Voltage                           | 0      | 3.5 V  |

|             | Analog Differential Input | Voltage                           |        | 2 Vpp  |

|             |                           | Common Mode                       | 0.5 V  | 3.8 V  |

|             |                           | V+,V- Absolute Range              | 0.5 V  | 3.8 V  |

|             | Power 5V                  | Current                           |        | 2 A    |

|             | Clock Output              | Differential Impedance            | 80 Ω   | 120 Ω  |

**Table 6.1:** operating limits for DT5550 connectors.

## 7 Cooling Management

The DT5550 board can operate in the temperature range -20 + 50 °C.

On the alloy box is installed a fan on top face. The user must take in care to provide a proper cooling to the board with external fan if the board is used in an enclosure or if the board is installed in a setup with poor air flow.

Excessive temperature will, in first instance, reduce the performance and the quality of the measurements and can also damage the board.

If the board is stored in cold environmental, please check for water condensation before power on.

The board has not been tested for radiation hardness. High energy particle can be source of soft error and can damage the FPGA. If used in strong proton or neutron beams, arrange proper shielding or remote the sensor with a custom cable.

## 8 Panels Description

Figure 8.1: Front panel view

Figure 8.2: Rear panel view

## Front Panel

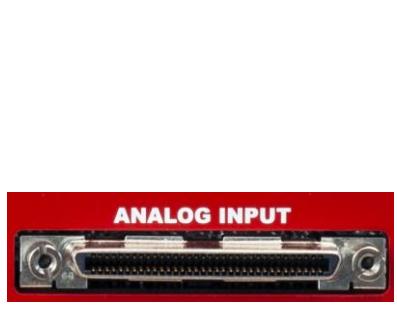

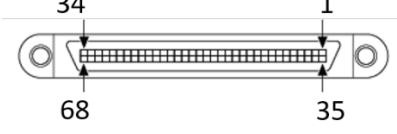

| ANALOG INPUT                                                                        |                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

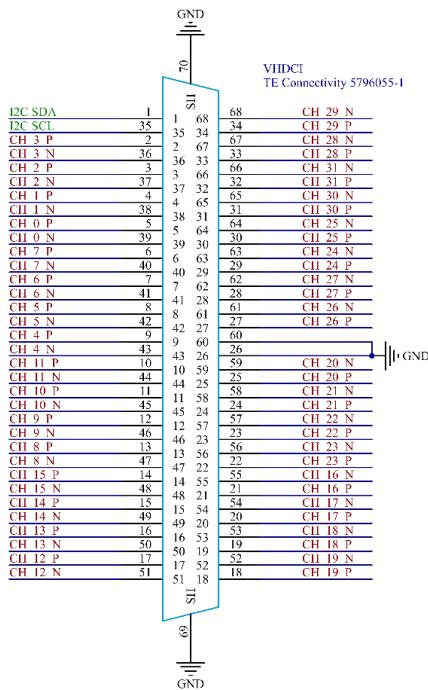

|    | <b>FUNCTION</b><br>68-pin connector carrying 32 differential input analog signals and one I2C (3.3V)<br><br><b>ELECTRICAL Specs</b><br>Differential Input dynamic: 2 V <sub>pp</sub><br>$Z_{diff}$ : 100 Ω                                                                                                                           | <b>MECHANICAL Specs</b><br>Series: VHDCI connector.<br>Type: 71430-0008<br>Manufacturer: TE Connectivity<br>Suggested plug: 68-pin VHDCI<br>Suggested cable: SCSI-5 type. |

|                                                                                     |                                                                                                                                                                                                                                                                                                                                      | <b>PINOUT</b><br>                                                                      |

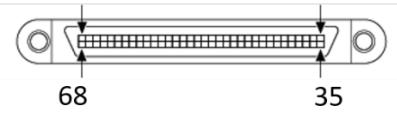

| DIGITAL -PORT A/B                                                                   |                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |

|  | <b>FUNCTION</b><br>68-pin connector carrying 24 differential digital lines, one low jitter clock, one I2C for low speed device configuration and one 2 A programmable voltage power supply<br><br><b>ELECTRICAL Specs</b><br>Sign. type: differential (CMOS 3.3V, LVCMOS 1.8V, LVDS, BLVDS).<br>Coupling: AC.<br>$Z_{diff}$ : 100 Ω. | <b>MECHANICAL Specs</b><br>Series: VHDCI connector.<br>Type: 71430-0008<br>Manufacturer: TE Connectivity<br>Suggested plug: 68-pin VHDCI<br>Suggested cable: SCSI-5 type. |

|                                                                                     |                                                                                                                                                                                                                                                                                                                                      | <b>PINOUT</b><br>                                                                    |

| LEDs                                                                                |                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                           |

|  | <b>FUNCTION</b><br>User LED: user firmware output LED (customizable)<br>POWER: power state on<br><br><b>ELECTRICAL Specs</b><br><i>Not available</i>                                                                                                                                                                                 | <b>MECHANICAL Specs</b><br>Not available                                                                                                                                  |

## Rear Panel

| DC INPUT                                                                            |                                                                                                                                                                                                                           |                                                                                                                                                                           |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | <b>FUNCTION</b><br>Input connector for the DT5550 main power supply from the external AC/DC adapter.<br><br><b>ELECTRICAL Specs</b><br>Typ. Input voltage: +12 VDC.                                                       | <b>MECHANICAL Specs</b><br>Series: CC power supply connectors<br><br><b>PINOUT</b><br> |

|    | <b>FUNCTION</b><br>Panel switch for module power supply ON/OFF:<br>OFF: <b>O</b> → power supply OFF.<br>ON: <b>I</b> → power supply ON.<br><br><b>ELECTRICAL Specs</b><br><i>Not available.</i>                           | <b>MECHANICAL Specs</b><br><i>Not available.</i>                                                                                                                          |

| IDENTIFYING LABEL                                                                   |                                                                                                                                                                                                                           |                                                                                                                                                                           |

|  | <b>FUNCTION</b><br>Board's identifying label indicating its serial number (S/N)                                                                                                                                           |                                                                                                                                                                           |

| CLOCK IN/OUT                                                                        |                                                                                                                                                                                                                           |                                                                                                                                                                           |

|  | <b>FUNCTION</b><br>Digital I/O connectors to synchronize the internal clock PLL with an external clock source.<br><br><b>ELECTRICAL Specs</b><br>CLOCK IN: 25 MHz, 3.3V, 50 Ω impedance<br>CLOCK OUT: 25 MHz, 3.3V, 50 mA |                                                                                                                                                                           |

| GPIO 1...8                                                                          |                                                                                                                                                                                                                           |                                                                                                                                                                           |

|  | <b>FUNCTION</b><br>General purpose digital I/O connectors. Their function is defined at firmware level<br><br><b>ELECTRICAL Specs</b><br>Signal level : NIM or TTL<br>Input impedance ( $Z_{in}$ ) : 50 Ω                 |                                                                                                                                                                           |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <p><b>USB 3.0</b></p>             | <p><b>FUNCTION</b><br/>USB connector for data readout and flow control</p> <p><b>ELECTRICAL SPECS</b><br/>Standard : compliant with USB 3.0<br/>Transfer rate: up to 240 MB/s</p>                                                                                                                                                                                                             |

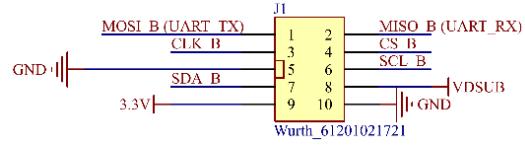

| <p><b>SERIAL</b></p>              | <p><b>FUNCTION</b><br/>Auxiliary connector to expose I2C, UART and SPI interfaces.</p> <p><b>ELECTRICAL SPECS</b><br/><i>Not available</i></p> <p><b>MECHANICAL SPECS</b><br/>Series: 10 ways male header<br/>Type: 61201021721<br/>Manufacturer: Wurth</p> <p><b>PINOUT</b></p>  <p>Wurth_61201021721</p> |

| <p><b>DEBUGGER</b></p>          | <p><b>FUNCTION</b><br/>Connector for direct FPGA access in order to perform fast firmware download and FPGA signals monitor and probing</p> <p><b>ELECTRICAL SPECS</b><br/>Standard: compliant with micro-USB</p> <p><b>MECHANICAL SPECS</b><br/>Series: USB Micro type.</p>                                                                                                                  |

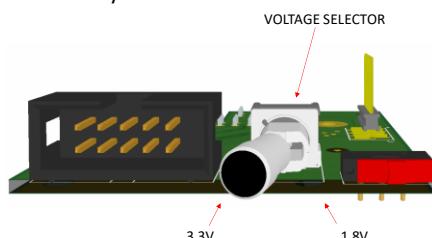

| <p><b>VOLTAGE SELECTOR</b></p>  | <p><b>FUNCTION</b><br/>Switch to select between 3.3 V and 1.8 V bank voltage for digital I/Os</p> <p><b>ELECTRICAL SPECS</b><br/><i>Not available.</i></p> <p><b>WARNING:</b> always remove the power before moving the switch</p>                                                                                                                                                            |

| <p><b>BOOT MODE SWITCH</b></p>  | <p><b>FUNCTION</b><br/>Switch to force the FPGA to boot in bootloader mode in order to upgrade the firmware</p> <p><b>ELECTRICAL SPECS</b><br/><i>Not available.</i></p>                                                                                                                                                                                                                      |

# 9 Functional Description

## Analog Input Stage

The DT5550 is a flexible and compact board meant to be used as a fully-programmable DAQ system for different applications which require to control both analog and digital signals.

The DT5550 has 32 differential analog inputs and hosts 4 ADCs operating in simultaneous sampling at 80 MS/S - 14 bit. Differential signals are used in order to minimize the crosstalk between channels and allows the system to operate minimizing the noise even with long cables carrying the analog inputs from detectors.

It is possible to connect the DT5550 to both single ended and differential output detector pre-amplifier. Differential output pre-amplifier can be connected directly to the DAQ while single ended detector requires the an analog frontend adapter board in order to achieve the best performance in terms of noise, linearity and resolution. CAEN suggest to use one of the following detector analog front end boards:

- **DT5550-AFE:** a 32 channels analog front end voltage mode amplifier (for PMTs, HPGe, etc). The board **converts the pre-amplified single ended signal from the detector in a differential signal.**

- **DT5550-AFES:** a 64 channels analog **front end transimpedance charge amplifier designed for SiPMs** application, with integrated High Voltage bias with channel by channel fine tuning. The DT5550-AFES board is equipped with a ready to use detector board for an 8x8 Hamamatsu SiPM matrix and it can be connected to one or two DT5550 to realize a complete system for waveform recording, imaging and spectroscopy.

The DT5550 has three frontal VHDCI (ULTRA-SCSI) connectors to carry analog and digital signal. The central connector is used for analog signals input. VHDCI connectors and cables are a very common industrial standard and allow connecting a large number of differential interconnection using single shielded cable. Each VHDCI connector carries up to 68 single ended wires or 34 differential couples.

The pinout of the frontal analog connector is shown in figure. Differential analog lines are indicated in red and the polarity is marked by the “\_P” and “\_N” label in the pin name.

Figure 9.1: front panel analog connector pinout.

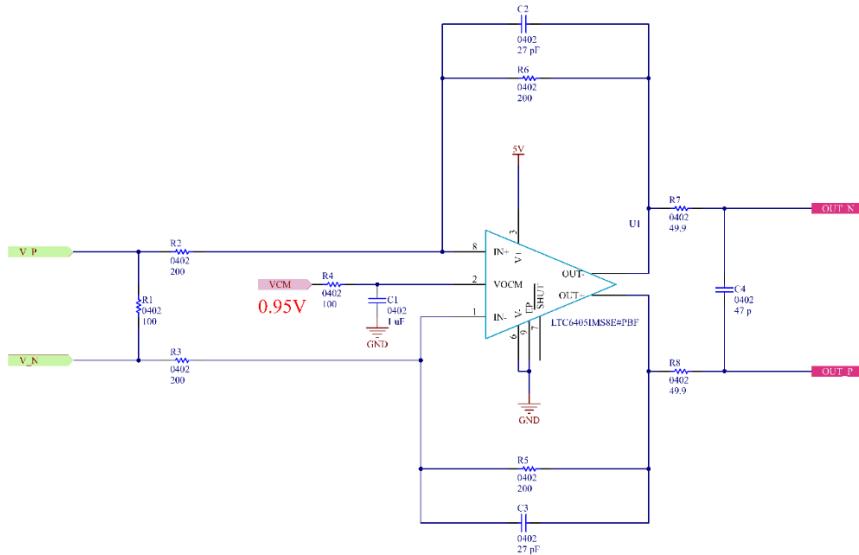

The DT5550 analog connector pins are connected to the analog front-end. An LTC6405 fully differential operational amplifier is used in order to buffer the input signals. The OPamp is not used only as simple buffer but has also the function of common mode isolation. While the ADC require exactly 0.95V as common mode, the front-end can accept any common mode between 0.5V and 3.8V. Moreover, wiring correctly the V\_P and V\_N terminals, the front-end is capable to accept both single ended and differential signals (see subsections below for more details)

The analog front-end has the following characteristics:

- Bandwidth: 31 MHz

- Gain: 1 V/V

- Differential Input Dynamic:  $2 V_{pp}$

- Single Ended Dynamic: +/- 1 V (with  $V_N$  terminals grounded), 2V (with  $V_N$  terminals connected to 1V source)

- Any common mode voltage is accepted if within the absolute maximum rating

- Absolute Input Dynamic: 0.5 V ... 3.8 V

- Differential Input Impedance:  $100 \Omega$

- Single Ended Impedance:  $75 \Omega$

- $50\mu V$  integrated noise

Figure 9.2: scheme of the analog input stage.

As previously said, the DT5550 accepts as input differential analog signal, which have several advantages:

- Immune to common mode noise

- Immune to channel cross-talk

- Immune to RF noise

- Immune to ground-loops

- Immune to ADC clock coupling

- With limited signal swing it is possible to achieve a larger input dynamic

However, if you have single-ended analog signals, CAEN suggests one of the connection explained below in order to adapt the single ended signals to the DT5550

## Differential Signal Input

Differential signal can be directly connected to the DT5550 input. Both  $V_P$  and  $V_N$  must be connected.

| SYMBOL | DESCRIPTION               | MIN | MAX         |

|--------|---------------------------|-----|-------------|

| VCM    | Input common mode         | 0.5 | 3.5         |

| VDIFF  | Input Differential signal | 0   | $2V_{pp}$   |

| $V_P$  | Input positive terminal   | 0.5 | 3.5         |

| $V_N$  | Input negative terminal   | 0.5 | 3.5         |

| RIN    | Input impedance           |     | $100\Omega$ |

Table 9.1: differential parameters for the DT5550 analog input.

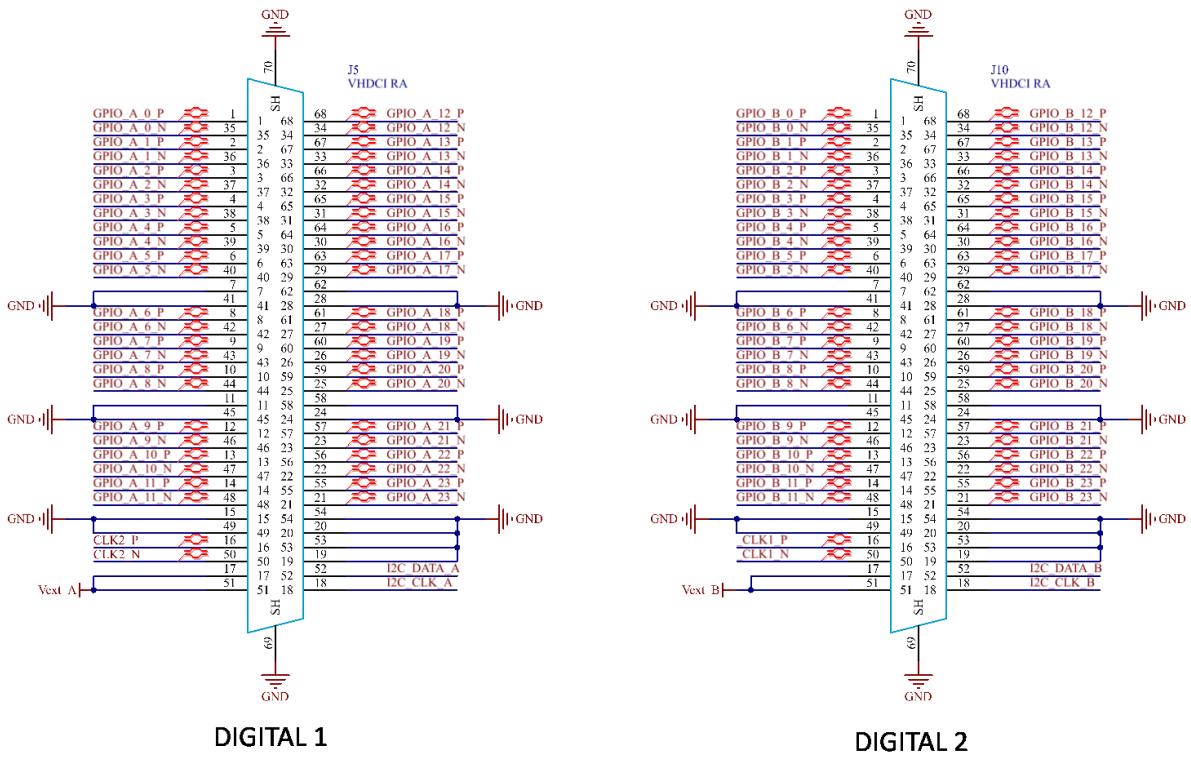

Modern ASICs are designed to have directly a differential signal output.

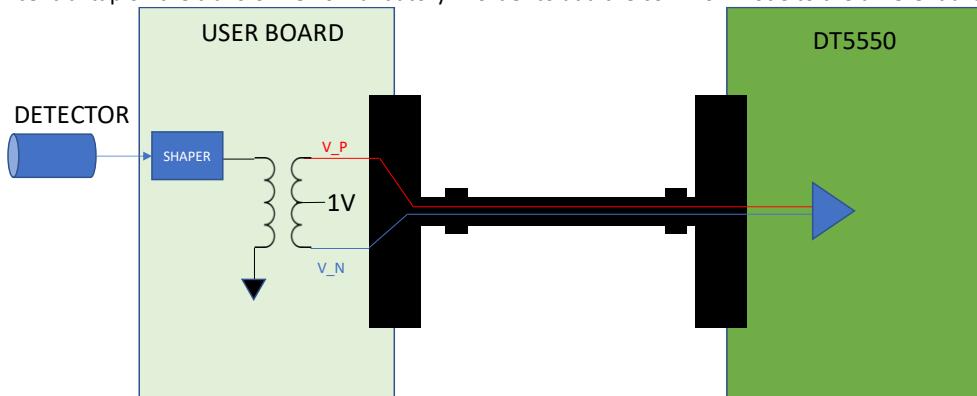

**Figure 9.3:** connection of differential outputs of an ASIC to the DT5550.

### DT5550AFE: Single-Ended to Differential conversion

The **DT5550AFE** is an analog front-end board specifically designed for the DT5550, in order to convert single-ended signals into differential ones. It has 32 analog inputs on MCX connectors and analog differential outputs on a single VHDCI connector. In this way, the converted signals can be carried out by a single VHDCI cable directly to the DT5550 analog input. Thanks to the DT5550AFE it is possible to easily connect detectors to the DT5550 for digitization and pulse processing purposes, as shown in **Figure 9.4**. Refer to **[RD3]** for more details on the DT5550AFE board.

**Figure 9.4:** connection of single-ended signals using the DT5550AFE.

### Active Single-Ended to Differential conversion

Single ended signals can be used as input of the DT5550 using active single ended to differential converter. Single ended to differential converter use a fully differential op-amp in the following configuration:

This configuration works perfectly even with higher resistors (multiply every value x10) in order to increase the input impedance.

**Figure 9.5:** connection of single-ended signals using an active single-ended to differential conversion.

The input of the single ended to differential converter can be a discrete shaper output or an analog output of an ASIC (this is the recommended solution to readout ASICs like Weeroc PETIROC, CITIROC, MAROC, etc.)

The user must take care of respecting the differential output parameters explained in **Table 9.1**

### AC-coupled passive Single-Ended to Differential conversion

A coupled inductor can be used in order to transform a single ended signal in a differential one. The advantage in using a passive transformer is that no extra power is required for the conversion and no noise is added to the input signal. The drawback is that the signal is AC coupled, that means that baseline information will be lost and the baseline fluctuations will depend on the rate.

A central tap on the transformer is mandatory in order to add the common mode to the differential signal

**Figure 9.6:** connection of single-ended signals using an AC-coupled passive single-ended to differential conversion.

## DC-coupled passive Single-Ended to Differential conversion

Several existing ASICs have a single channel dedicated to the analog output. Usually this ASICs have a single ended output in order to reduce the ASIC pinout.

**Figure 9.7:** connection of single-ended signals using a passive single-ended to differential conversion.

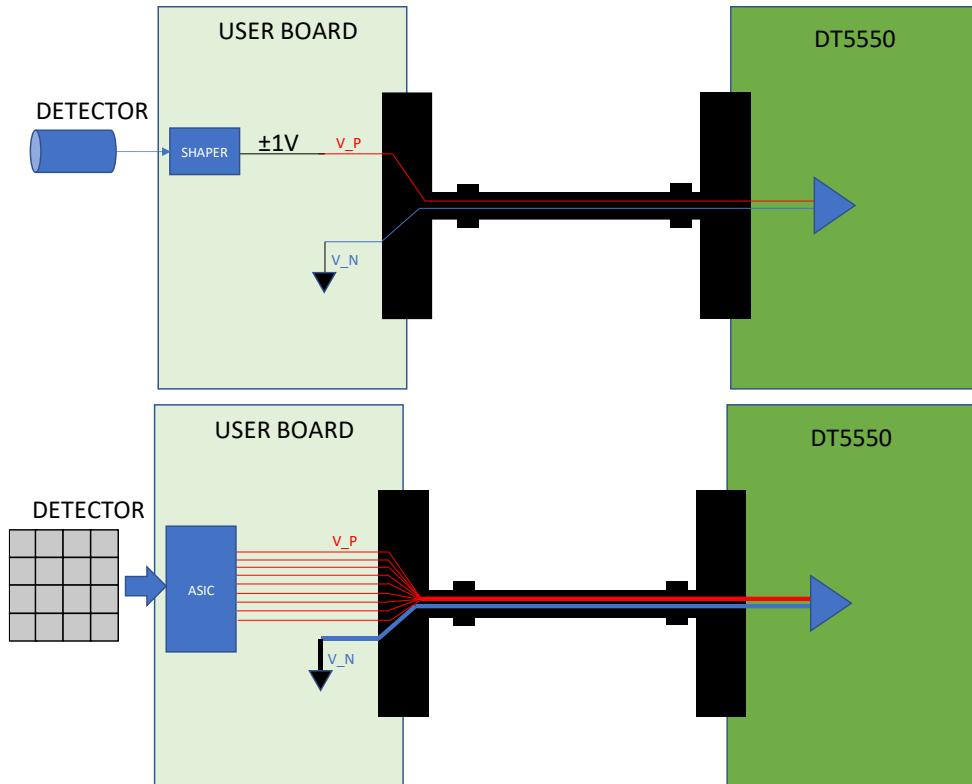

The user should ground (or connect to a fixed power supply) all the negative ( $V_N$ ) terminal of all channels used in single-ended mode. Please take note that with this solution all benefit of differential signal will be lost.

We suggest (if possible) to ground the  $V_N$  terminals as close as possible to the DT5550. It is possible to design a small PCB with a VHDCI male connector on one side and a STRIP ribbon cable connector on the other side. On that PCB all  $V_N$  must be connected to GND or 1V. We also suggest to use a shielded ribbon cable when single ended signal are carried on the cable. We suggest to alternate one signal and one ground on the ribbon cable in order to reduce the cross talk

**Figure 9.8:** connection of single-ended signals using a passive single-ended to differential conversion and grounding optimization.

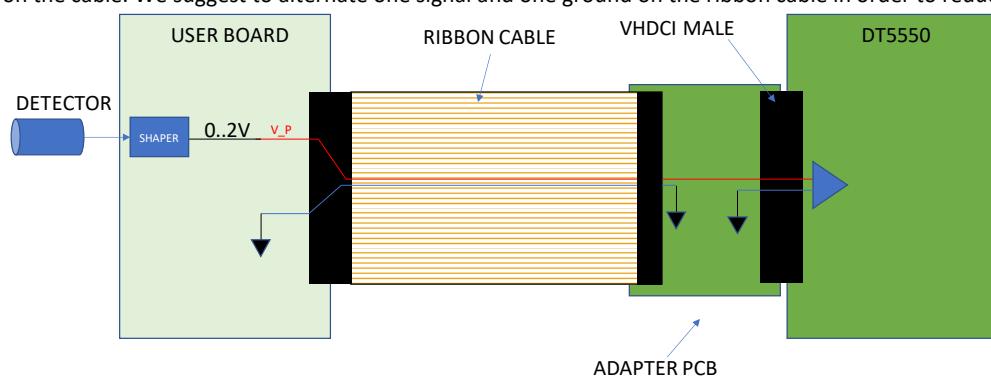

## Digital Input Stage

The DT5550 hosts two VHDCI connectors for digital inputs/outputs on the front panel. Each connector carries:

- 24 differential lines supporting the standards CMOS 3.3V, LVCMOS 1.8V, LVDS, BLVDS (or PSEUDO LVDS)

- one low jitter clock

- one I2C for low speed device configuration

- one 2 A programmable voltage power supply

The pinout of the digital VHDCI connector is shown below.

Figure 9.9: pinout of the digital connectors of the DT5550.

Digital I/O can be used for several applications, for example:

- Input for triggers/veto

- Input from photon counting detector / ASIC

- Readout of digital ASIC both with serialized output or parallel output

- Control of the readout process of analog ASIC

- Direct interconnection between multiple DT5550 to extend processing algorithm

Using SCI-Compiler, is possible to select the I/O standard and the pin direction (IN/OUT). Pin direction and signal standard must be selected at configuration time and can not be changed in real-time.

A switch on the back side of the DT5550 allows to select the operational voltage for all digital I/Os. The switch can be moved only when the instruments is off.

Figure 9.10: DT5550 voltage selector switch for digital I/Os.

**⚠️ WARNING:** Do not change the bank voltage of the I/O connector while the instruments is powered. It could damage the board and the connected detector system. In order to minimize the risk of unwanted voltage changes a security switch is used.

LVDS signals can be used both with 3.3V and 1.8V bank power supply. The LVDS common mode is 1.65V when 3.3 V is selected while when is 0.9V if 1.8 V is selected. Both common modes are within the LVDS specifications.

The clock signal is driven directly by the clock generator, indeed is not possible to select the voltage. The clock signal is always an LVDS with 1.25V common mode.

When CMOS signal is used we recommend connecting together all ground pin at board level.

## Clock Distribution

The DT5550 has a versatile clock distribution net. A Texas Instruments CDCE62005 clock generator is used in order to generate the clock for all devices on the board. Two clocks (fixed at 80 MHz) are provided to the ADCs. The others three clocks are connected to the front panel digital connectors and to the FPGA. By default, the chip is configured to generate the ADC clock at 80 MHz and at 320 MHz LVDS to the FPGA, while the clock on front panel connectors is disabled.

**⚠️ WARNING:** The user is not allowed to reprogram the clock generator, since the FPGA has no other clock source except one. If the FPGA clock is disabled, there will be no way to restore a clock to the FPGA. User can change on-fly the configuration of the clock generator without writing it in the EEPROM.

SCI-Compiler clock manager allows the user to configure the Clock Generator frontal connector frequency. This setting will be not stored in the clock generator EEPROM but in the firmware. When the firmware boot-up it will override the default configuration of the EEPROM writing in the volatile memory.

An eventual external clock input signal must be a 25MHz, low jitter, 3.3V CMOS input. The external clock output is a CMOS 3.3v 25 MHz square wave. The clock output is able to drive a 50Ω terminated cable.

**Figure 9.11:** scheme of the clock distribution on the DT5550.

# 10 Drivers & Libraries

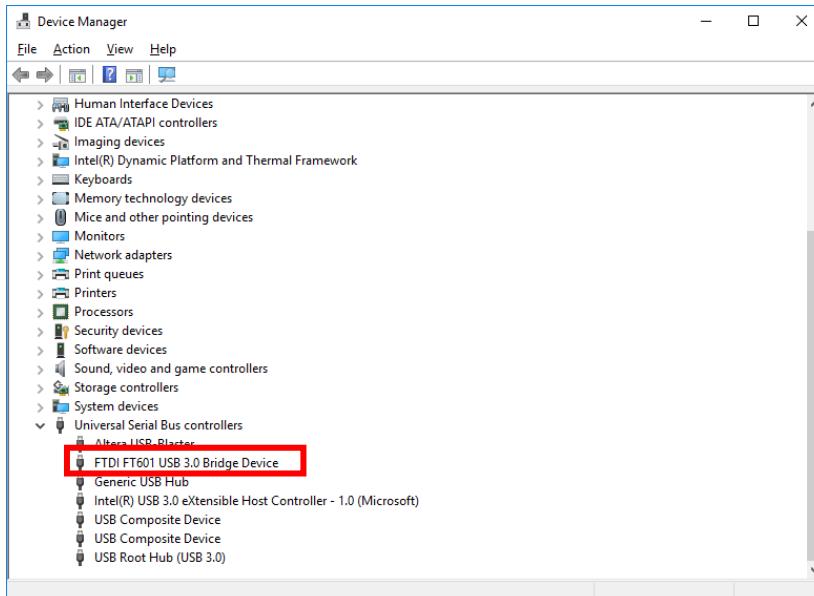

The DT5550 uses the standard FTDI FT60X driver (D3XX Driver) for USB 3.0 connection. We decided not to customize the device driver in order to preserve the portability of the driver on Windows/Linux/MacOS/Android OS. Drivers for these operating systems can be downloaded from FTDI web page:

<http://www.ftdichip.com/Drivers/D3XX.htm>

Follow the FTDI driver installation guide to install the device driver.

**Note:** upon installation of SCI-Compiler or SCI-55X0 Readout Software, the drivers for DT5550 will be automatically installed in your Windows OS.

Figure 10.1: the Windows Device Manager showing up the DT5550 as FTDI FT601 USB3.0 Bridge Device

Libraries for C/C++/C#/Python are generated by SCI-Compiler when firmware code is compiled. The libraries can be used for custom software development on Windows/Linux/MacOS/Android. Libraries related to the default firmware are provided within the SCI-55X0 Readout Software open source code.

# 11 Firmware and Upgrade

The DT5550 is a programmable platform and it is designed in order to encourage the user to develop its own custom firmware using **SCI-Compiler** to generate and compile the firmware code.

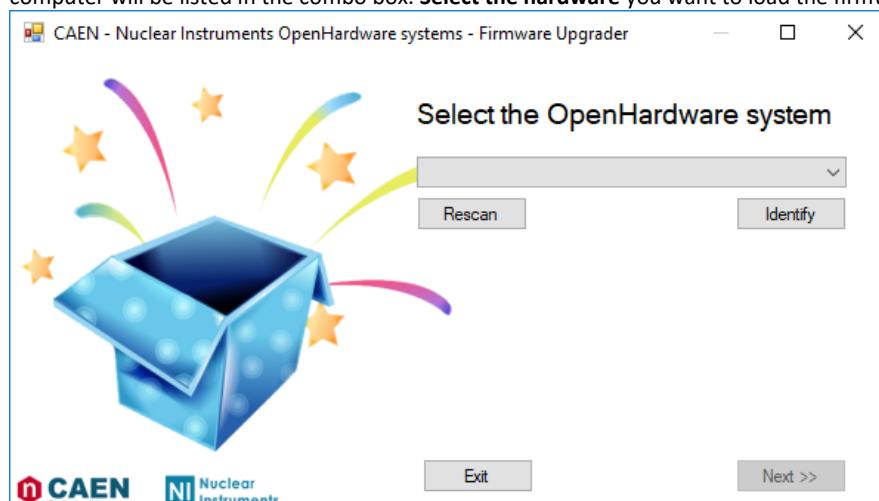

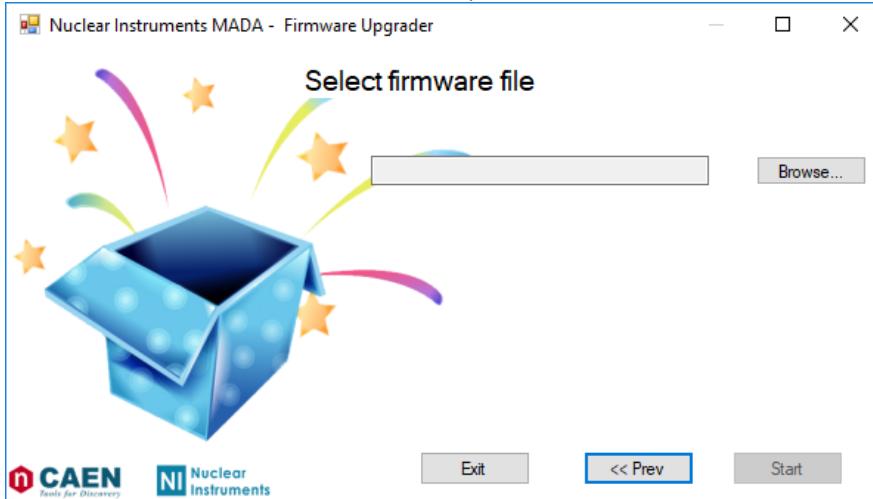

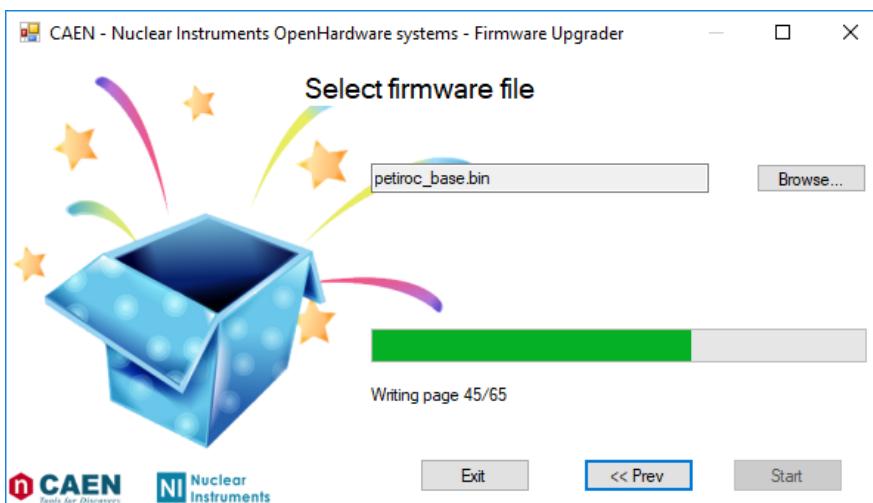

However, a full working default firmware is provided: this is a fully featured solution and it is developed not as a basic example to start developing with SCI-Compiler but as a full DAQ readout system firmware. The DT5550 comes with the default firmware already uploaded. In any case the firmware can be downloaded from CAEN website and easily installed on the board with the OpenHardware – Firmware Upgrader tool (see Sec. **Firmware Upgrade**)

The **default firmware** implements typical features of Waveform Recording Digitizers and QDC algorithms and it is fully managed by the free-downloadable and open-source [SCI-55X0 Readout Software](#). In more details, the default firmware implements the following pulse processing features:

- Waveform digitization of all analog channels

- Leading edge or derivative trigger

- 32 independent channels digital charge integration for energy calculation (QDC)

- Time stamping with 12.5 ns resolution

- Different readout modes: independent channels, frame trigger (OR of all channels trigger), external trigger

- External veto and trigger on programmable LEMO GPIO

- List readout mode

- Interface with DT5550AFE

- Rate meter with dead time calculation on each channel

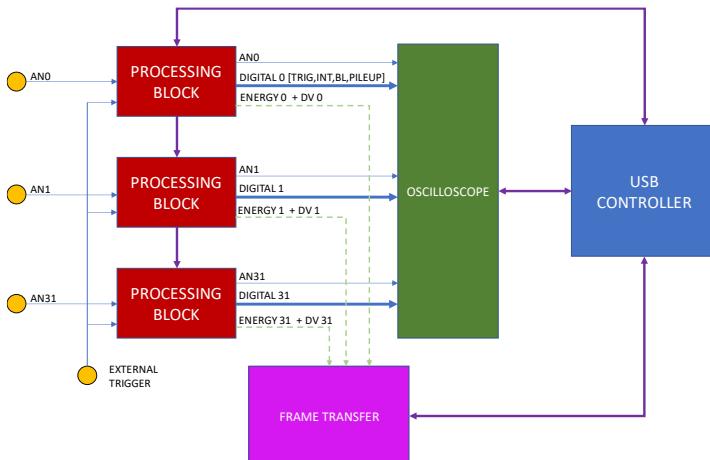

In general, a firmware for the DT5550 is divided in two parts:

- FRAMEWORK: a set of non-configurable blocks (or configurable with some limitations) that implements low level functionalities like ADC management, USB3 communication, I/O buffers, etc.

- PROCESSING CORE: firmware developed by the user (the block diagram in SCI-Compiler tool) with all processing algorithms to analyze and process the acquired data.

## Firmware Framework Structure

All firmware for DT5550 have a common structure called framework. The framework contains the building blocks which are mandatory for the board correct working. The framework should not be edited by the user but can be configured with some limitations using SCI-Compiler tool. The framework is like the kernel of an OS and manage the low-level interfacing with hardware peripherals. The main structures are:

- ADC manager: configures the ADCs, deserialize data and provide them as a data vector synchronous to the acquisition clock.

- Clock configuration: configures the clock generator with user-defined configuration after bootstrap.

- Frontal Connector Power Supply: configures the voltage on the power supply pins of the frontal connector

- I2C Interface: Map on USB or allow direct firmware access to all the physical I2C interfaces

- SPI/UART Interface: Map on USB or allow direct firmware access to the rear SPI/UART interfaces; it allows to select between UART/SPI at designing time

- I/O buffers: allows to select the standard (CMOS/LVDS) and the direction (input/output) of all programmable I/Os.

- USB 3 interface: implements the USB 3 to local bus conversion

SCI-Compiler masks all physical VHDL interconnection automatically placing and configuring the blocks above. The configurable parameters can be set in the project property page. See SCI-Compiler documentation for further details

## Firmware design: the processing core

The DT5550 processing core is a Xilinx Kintex7 FPGA. The FPGA can be programmed in several ways:

- VHDL/Verilog: this is the typical language for developing processing system in FPGAs. It is based on basic operation (logic/arithmetic/conditional processing/sequential element) connected each other to build component. Component are then connected together in order to create more complex designs.

- C: a C/C++ program is automatically converted in a VHDL design by a software tool.

- Design with high level blocks: the user connects together a series of pre-designed building block in order to obtain the desired processing system.

**SCI-Compiler** is a set of very high level blocks which implement the functionalities of the most common instrumentation used in physics experiment: digitizer, MCA, TDC, Time Over Threshold, trigger, scaler, etc.

Sci-Compiler is designed to work at best with DT5550 and CAEN suggests to use this firmware generator and compiler tool since it focuses the attention only on the functional blocks of the application to be implemented and does not require a deep knowledge of the device in use. The user is free to develop a firmware in VHDL without using the SCI-Compiler. We suggest to use the default framework to correctly initialize the board components. Framework source code is partially encrypted in order to protect our IP and avoid unauthorized copy of the board.

The framework code is available inside the installation folder of SCI-Compiler.

SCI-Compiler generates VHDL code and Vivado Project. If the user wants to add custom functionalities that are not implementable with SCI-Compiler, he can use the SCI-COMPILER to develop some parts of the design and then open the project in Vivado to add missing function writing in VHDL and then compile as a standard Vivado Project.

The DT5550 can be used for different application, requiring different firmware (for example multichannel analog digitization, readout of mixed signal ASICs, direct readout of shaped signals).

In the following we describe the default firmware of the DT5550.

## Default firmware for DT5550

The DT5550 has a default firmware pre-programmed from factory. The default firmware implements a 32-channels digitizer with waveform recording and charge integration.

The default firmware is designed to work with SCI-55X0 Readout Software. It is fully developed in SCI-Compiler and can be easily modified by the user. SCI-55X0 Readout Software is distributed open source in VB.NET. The user can start from the firmware and software project to create his own custom application.

The default firmware works with both differential and single-ended signals. SCI-55X0 Readout Software can directly control the DT5550AFE single-ended to differential adapter board to set the offset and the input impedance.

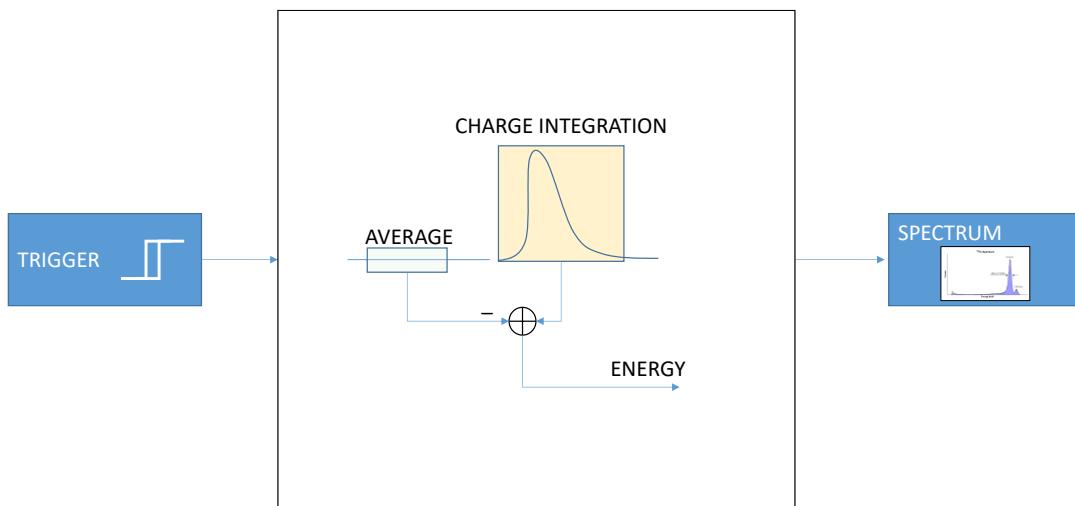

### Charge integration

The basic structure of the firmware is the following: the trigger identifies the signal and calculates the sum of all digitized data. The baseline is calculated as moving average of the input signal. The baseline calculation is suspended during the charge integration. The energy is calculated as the difference between the charge and the baseline. The data are then transmitted to the computer as a list of time and energy. The SCI-55X0 Readout Software receives the list and calculates the energy spectrum for each channel; it also displays data as bidimensional heatmap (image from the detector)

**Figure 11.1:** scheme of the default firmware for the DT5550.

The firmware diagram above is developed in SCI-Compiler and implements the single channel processing logic. The SCI-Compiler project is then designed in a hierachic way. Multiple processing blocks calculate the energy and timestamp of each channel: these processing blocks are connected together at the top of the project.

Figure 11.2: Firmware hierachic structure in SCI-Compiler.

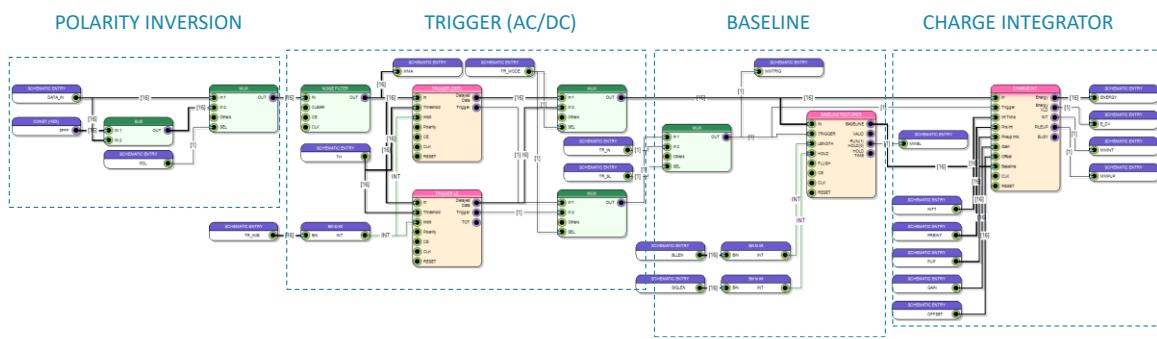

Figure 11.3: SCI-Compiler scheme for single channel data processing in the default firmware.

The SCI-Compiler scheme of the single channel processing block is shown in Figure 11.3. Different main parts can be distinguished in this block diagram:

- **Polarity inversion** chain allows to accept both polarity signal. The signal is inverted calculating (0x3FF – signal). A multiplexer selects between positive (no operation) and negative (inverted) polarity.

- The **trigger** can operate with both leading edge and derivative trigger. The trigger mode to be used can be selected in the SCI-55X0 Readout Software. Two multiplexer are used: the first selects between leading and derivative trigger, while the second selects between internal and external trigger.

- The **baseline** is calculated by averaging the signal values for a certain amount of time. The baseline calculation starts when the TRIGGER is high and the time interval indicated at the HOLD input has been passed. The output of the “Baseline Restorer” SCI-Compiler block contains the baseline value.

- The **charge integration** is managed in SCI-Compiler by the “Charge Int” block and it is performed on the input signal delayed by the trigger. It is possible to specify in input the integration gate, the pre-gate, the pile-up rejection time and the baseline value. The result of the integration process, i.e. the area of the input signal, is provided at the ENERGY output pin of the “Charge Int” block. The PILEUP output signal indicates if the considered input signal has been characterized by a pileup event. The BUSY output is high if the integration calculation is occurring.

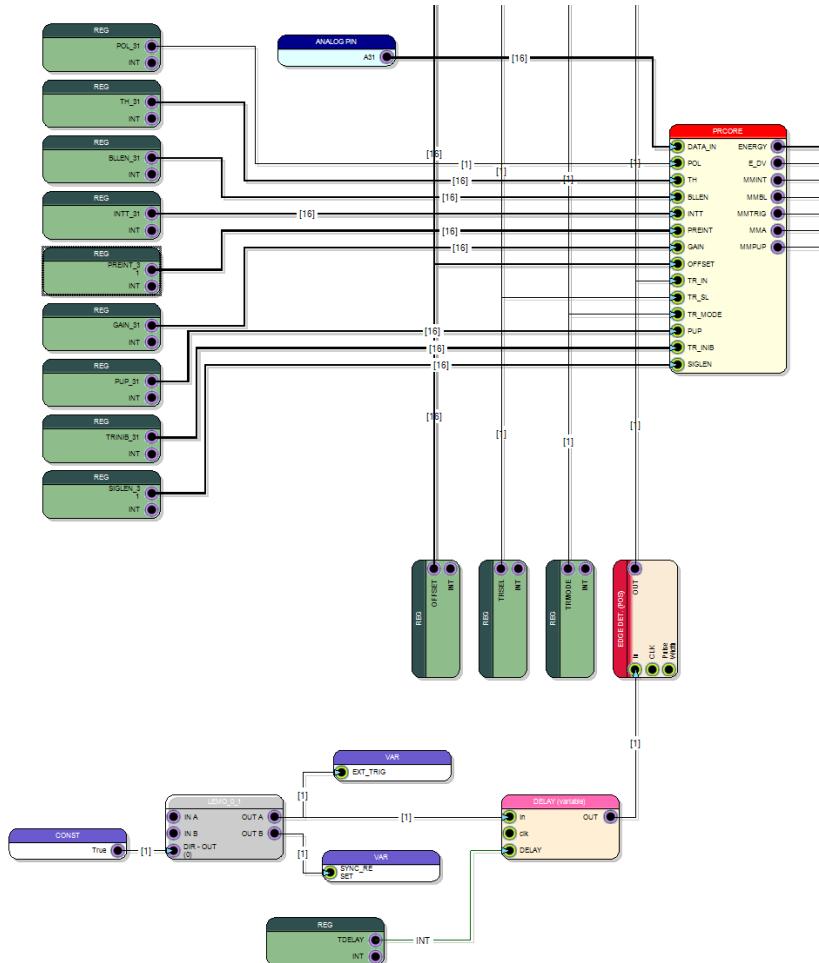

The single channel processing block shown in Figure 11.3 can be represented by a unique block, the PRCORE block shown in Figure 11.4. Inside this block there are all sub-blocks illustrated before. The PRCORE is connected to the Analog Input and to the registers for the configuration. Moreover, the PRCORE can accept an external trigger signal coming from LEMO 0 (see again Figure 11.4, bottom part).

**Figure 11.4:** SCI-Compiler scheme of the whole charge integration process for a channel of the DT5550.

The registers used for charge integration settings are listed below (see also green blocks in **Figure 11.4** for reference). These registers can be used by the user to configure the data acquisition when developing a custom application to control the DT5550

| Register Name<br>(XX= channel number) | Address<br>(HEX)    | Bits | Description                                                                                                                                                                                                                                                                                       |

|---------------------------------------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POL_XX                                | [0x10000 : 0x1001F] | 32   | Polarity of the input signal.<br>0: input signal is positive<br>1: input signal is negative                                                                                                                                                                                                       |

| TH_XX                                 | [0x10020 : 0x1003F] | 32   | Trigger threshold. If derivative trigger is selected this is the slope of the signal, if leading edge trigger is selected this is the value of the input signal height that fires the trigger                                                                                                     |

| INTT_XX                               | [0x10040 : 0x1005F] | 32   | Length in samples of the integration window.                                                                                                                                                                                                                                                      |

| BLLEN_XX                              | [0x10060 : 0x1007F] | 32   | Length in samples of the baseline (1 sample = 12.5ns)                                                                                                                                                                                                                                             |

| SIGLEN_XX                             | [0x10080 : 0x1009F] | 32   | Length of the whole signal used for the baseline calculation hold-off.                                                                                                                                                                                                                            |

| PREINT_XX                             | [0x100A0 : 0x100BF] | 32   | Length in samples of the pre-integration window; the pre-integration window integrates the part of the signal before the trigger                                                                                                                                                                  |

| GAIN_XX                               | [0x100C0 : 0x100DF] | 32   | Gain of the charge integrator. Usually this number should be equal to $1/INTT \times 65535$ . It is possible to increase the gain and the measure resolution multiply by an arbitrary value the previous number                                                                                   |

| TRINIB_XX                             | [0x100E0 : 0x100FF] | 32   | Length of the trigger inhibit. Trigger inhibit avoid to double trigger a signal.                                                                                                                                                                                                                  |

| PUP_XX                                | [0x10100 : 0x1011F] | 32   | Length in samples of the pileup window. The pileup window opens after the end of the integration window. An event occurs in the integration window both events (the integrating event and the piled up one) are discarded. If event occurs in the pileup event only the second event is discarded |

| TRMODE                                | 0x10120             | 1    | Trigger mode<br>0: derivative<br>1: leading edge                                                                                                                                                                                                                                                  |

| TRSEL                                 | 0x10121             | 1    | Trigger select<br>0: internal<br>1: external trigger (LEMO 0)                                                                                                                                                                                                                                     |

| OFFSET                                | 0x10122             | 1    | Digital offset enabled/disabled                                                                                                                                                                                                                                                                   |

| TDELAY                                | 0x10124             | 1    | Delay applied on the external trigger. External trigger usually should be delayed in order to compensate the DT5550 pipeline (about 200ns)                                                                                                                                                        |

**Table 11.1:** registers description of the charge integrator module.

In the full SCI-Compiler project, all channels outputs (energy) are connected to the frame transfer module. The frame transfer module is able to transfer all channels together when one triggers. It is also possible to operate in list mode: energy, time, channel information is transferred as soon as a specific channel trigger.

## Waveform recording

An oscilloscope module is also available in SCI-Compiler and it allows to inspect the input signal and digitize the waveform. The oscilloscope allows the user to digitize the analog input signal synchronously with four digital tracks:

- Integration probe: the signal is high when integration is in process.

- Trigger

- Baseline: the signal is high when baseline calculation is in progress.

- Pileup: the signal marks events discarded by the pileup rejector

**Figure 11.5:** scheme of the oscilloscope module available in the default firmware for the DT5550.

In the graphical interface of the Oscilloscope tool (available directly in SCI-Compiler) the user can set the following parameters: the trigger source (external, internal or the specific channel), the trigger mode (automatic, single shot), the trigger level, the acquisition window and the position of the triggered signal in the acquisition window. These parameters, together with the oscilloscope status and the waveform data can be controlled through some registers automatically generated during the block creation. The register addresses are available in the .json file generated during the firmware compilation. These registers can be used by the user to configure the data acquisition when developing a custom application to control the DT5550. Below the registers for the oscilloscope module are listed:

### CONFIG\_ARM

A transition from 0 to 1 of the value of this register enables the oscilloscope measurement.

### CONFIG\_DECIMATOR

The value set with this register represents the decimation factor for the output data.

### CONFIG\_TRIGGER\_MODE

This register sets all the information of the data acquisition trigger. The first three bits of the value written in the register specify the trigger acquisition mode:

000 -> external trigger

010 -> software trigger

001 -> analog signal trigger

100 -> digital 0 signal trigger

101 -> digital 1 signal trigger

110 -> digital 2 signal trigger

111 -> digital 3 signal trigger

The fourth bit, that has to be specified for the analog channel trigger mode, represents the trigger edge: 0 is a rising edge (to be set for positive signals) and 1 is a falling edge (in case of negative signals). For the software trigger mode the seventh bit has to be set to 1 to trigger the data acquisition. In all the cases of the analog and digital trigger modes the channel can be specified from the eighth to the fifteenth bit.

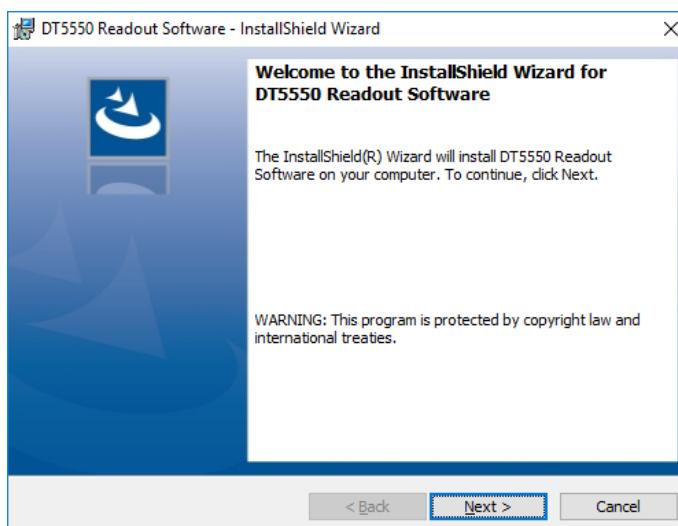

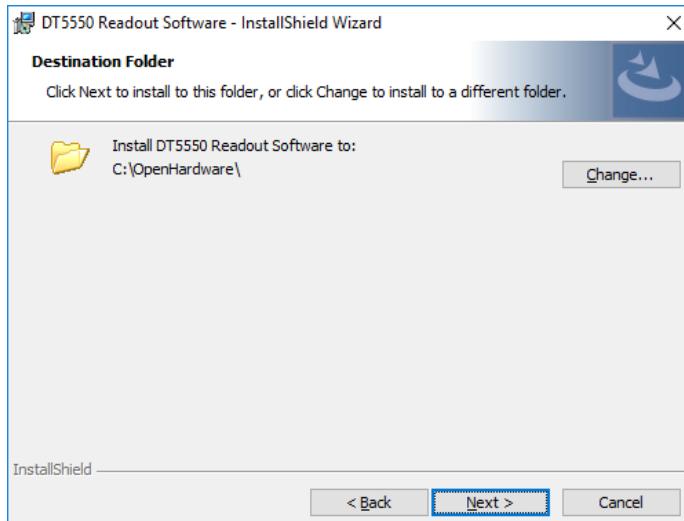

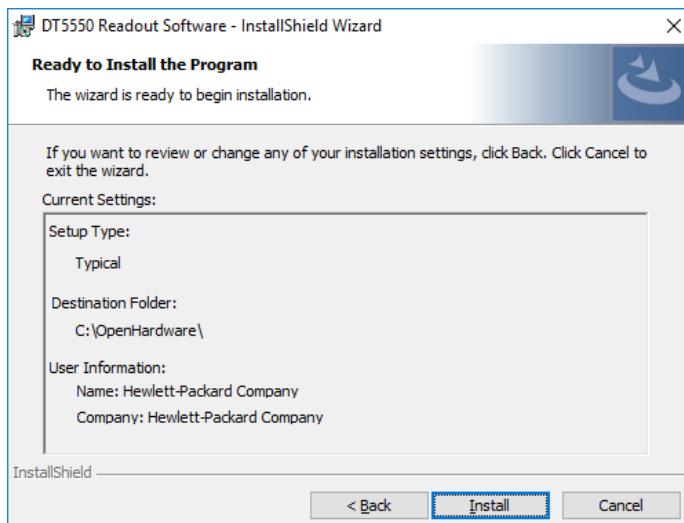

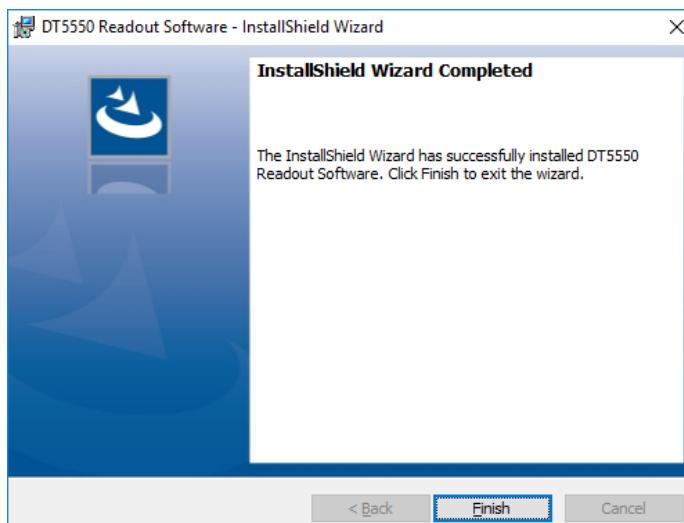

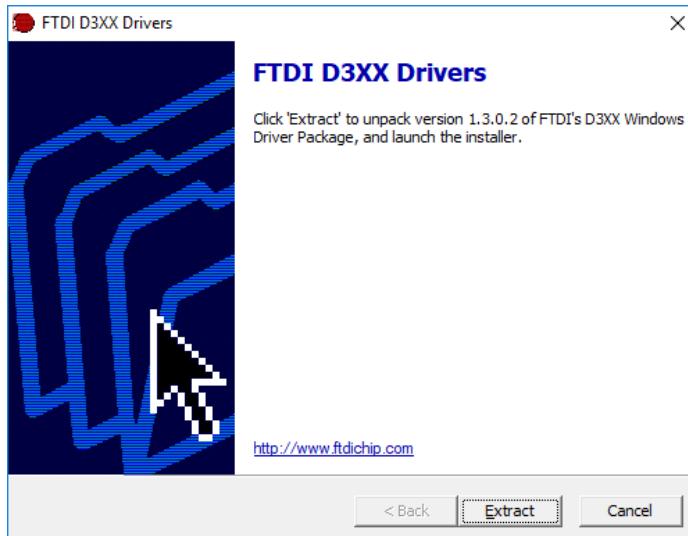

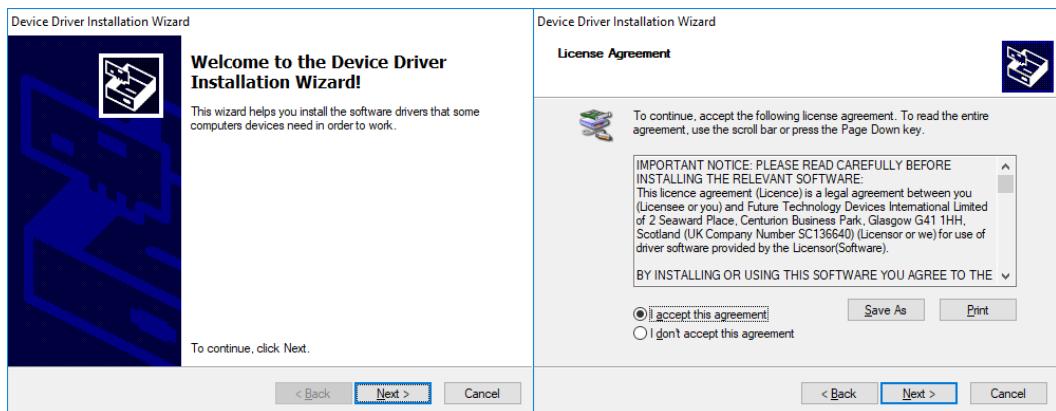

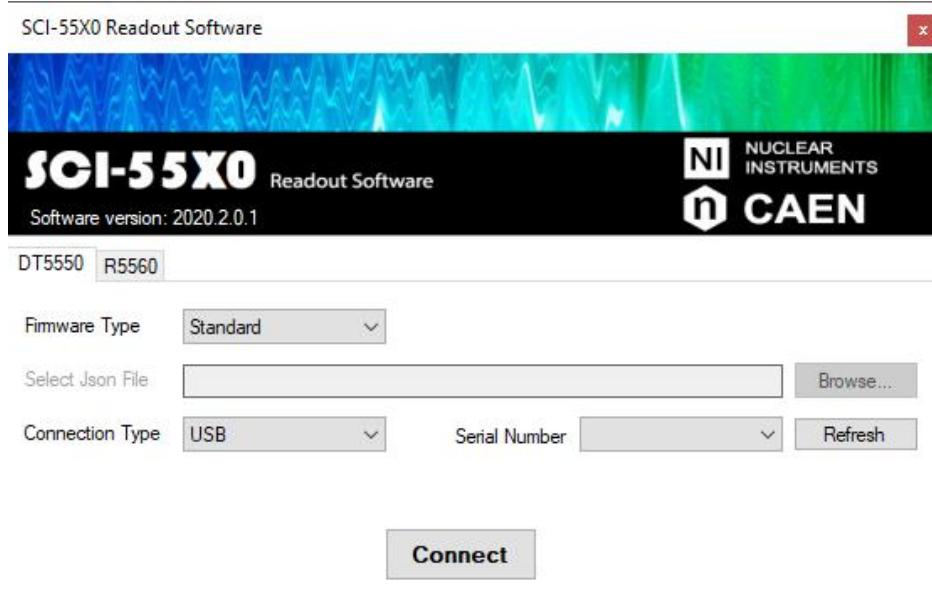

### CONFIG\_PRETRIGGER