# Register your device

Register your device to your **MyCAEN+** account and get access to our customer services, such as notification for new firmware or software upgrade, tracking service procedures or open a ticket for assistance. **MyCAEN+** accounts have a dedicated support service for their registered products. A set of basic information can be shared with the operator, speeding up the troubleshooting process and improving the efficiency of the support interactions.

**MyCAEN+** dashboard is designed to offer you a direct access to all our after sales services. Registration is totally free, to create an account go to <https://www.caen.it/become-mycaenplus-user> and fill the registration form with your data.

1

create a MyCAEN+ account

2

register your devices

3

get support and more!

<https://www.caen.it/become-mycaenplus-user/>

# Purpose of this User Manual

This User Manual contains the technical description of the front-end electronic board (FEB) A1702/DT5702 for the readout of an array of 32 Silicon Photomultipliers (SiPM) and the hardware/software operation.

## Change Document Record

| Date                             | Revision | Changes                                                                                                                                                           |

|----------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 10 <sup>th</sup> , 2017  | 00       | Initial release                                                                                                                                                   |

| May 10 <sup>th</sup> , 2018      | 01       | Added firmware description and ordering option.<br>Revised chapter Errore. L'origine riferimento non è stata trovata..<br>Extended chapter <b>Test Software</b> . |

| July 20 <sup>th</sup> , 2018     | 02       | Revised Chap. <b>Packaging and compliance</b>                                                                                                                     |

| June 4 <sup>th</sup> , 2019      | 03       | Warning added in <b>Jumpers</b> .                                                                                                                                 |

| November 3 <sup>rd</sup> , 2021  | 04       | General revision of Safety Notices and Installation Instructions.                                                                                                 |

| February 24 <sup>th</sup> , 2023 | 05       | Added Additional instruction for a safe use.                                                                                                                      |

## Symbols, abbreviated terms and notation

|              |                                         |

|--------------|-----------------------------------------|

| ADC          | Analog-to-digital converter             |

| ASIC         | Application Specific Integrated Circuit |

| GUI          | Graphical User Interface                |

| SiPM or MPPC | Silicon Photo-Multiplier                |

| FEB          | Front End Boards                        |

| PPS          | Pulse Per Second                        |

| SPI          | Serial Peripheral Interface             |

| TDC          | Time-to-digital converted               |

## Reference Documents

- [RD1] A.Aloisio, et al., *FPGA Implementation of a High-resolution Time-to-Digital Converter*, 2007 IEEE Nuclear Science Symposium Conference Record, N15-137.

- [RD2] M.Auger et al., *Multi-channel front-end board for SiPM readout*, Journal of Instrumentation, Volume 11, 2016

- [RD3] WeeROC Citiroc1A datasheet (<https://www.weeroc.com/en/products/citiroc-1a>)

## Manufacturer contact

**CAEN S.p.A.**

Via Vetraia, 11 55049 Viareggio (LU) - ITALY

Tel. +39.0584.388.398 Fax +39.0584.388.959

[www.caen.it](http://www.caen.it) | [info@caen.it](mailto:info@caen.it)

© CAEN SpA – 2023

## Limitation of Responsibility

If the warnings contained in this manual are not followed, CAEN will not be responsible for damage caused by improper use of the device. The manufacturer declines all responsibility for damage resulting from failure to comply with the instructions for use of the product. The equipment must be used as described in the user manual, with particular regard to the intended use, using only accessories as specified by the manufacturer. No modification or repair can be performed.

## Disclaimer

No part of this manual may be reproduced in any form or by any means, electronic, mechanical, recording, or otherwise, without the prior written permission of CAEN spa.

The information contained herein has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. CAEN spa reserves the right to modify its products specifications without giving any notice; for up to date information please visit [www.caen.it](http://www.caen.it).

## Made in Italy

We remark that all our boards have been designed and assembled in Italy. In a challenging environment where a competitive edge is often obtained at the cost of lower wages and declining working conditions, we proudly acknowledge that all those who participated in the production and distribution process of our devices were reasonably paid and worked in a safe environment (this is true for the boards marked "MADE IN ITALY", while we cannot guarantee for third-party manufactures).

## Table of contents

|                                                                        |           |

|------------------------------------------------------------------------|-----------|

| .....                                                                  | 1         |

| Purpose of this User Manual .....                                      | 3         |

| Change Document Record .....                                           | 3         |

| Symbols, abbreviated terms and notation .....                          | 3         |

| Reference Documents .....                                              | 3         |

| Manufacturer contact.....                                              | 3         |

| Limitation of Responsibility .....                                     | 3         |

| Disclaimer.....                                                        | 3         |

| Made in Italy.....                                                     | 4         |

| <b>Table of contents.....</b>                                          | <b>5</b>  |

| <b>List of Figures.....</b>                                            | <b>6</b>  |

| <b>List of Tables .....</b>                                            | <b>7</b>  |

| <b>1 Introduction .....</b>                                            | <b>8</b>  |

| <b>2 Safety Notices .....</b>                                          | <b>9</b>  |

| Important notice .....                                                 | 10        |

| <b>3 Technical Specifications.....</b>                                 | <b>11</b> |

| <b>4 Packaging and compliancy .....</b>                                | <b>12</b> |

| <b>5 PID (Product Identifier) .....</b>                                | <b>14</b> |

| <b>6 Power Requirements .....</b>                                      | <b>15</b> |

| <b>7 Installing the device .....</b>                                   | <b>16</b> |

| <b>8 Hardware Description .....</b>                                    | <b>17</b> |

| Jumpers and auxiliaries.....                                           | 18        |

| <b>9 Functional Description.....</b>                                   | <b>20</b> |

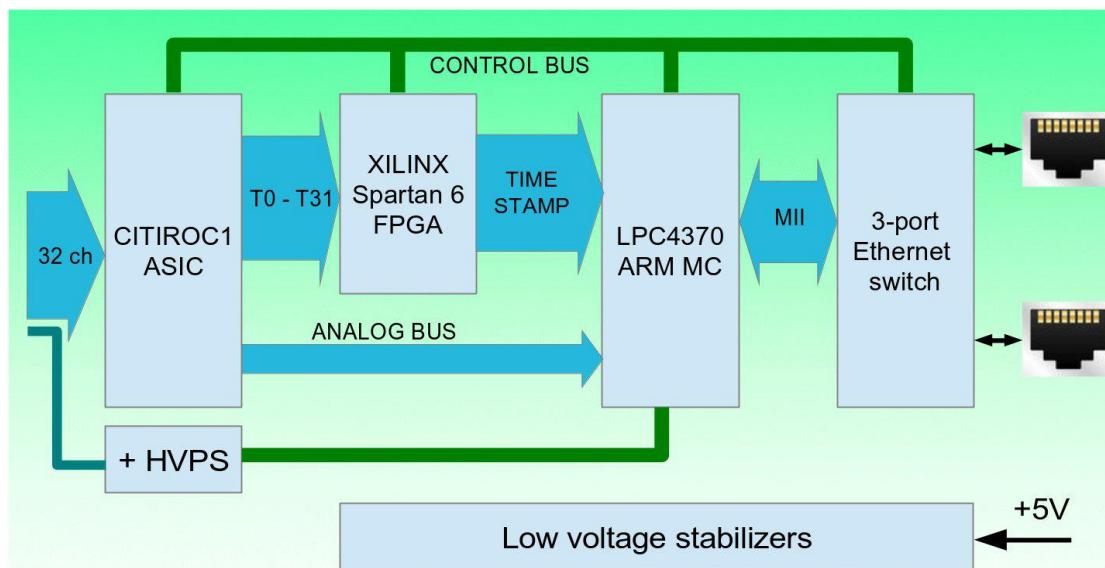

| General structure and main components.....                             | 20        |

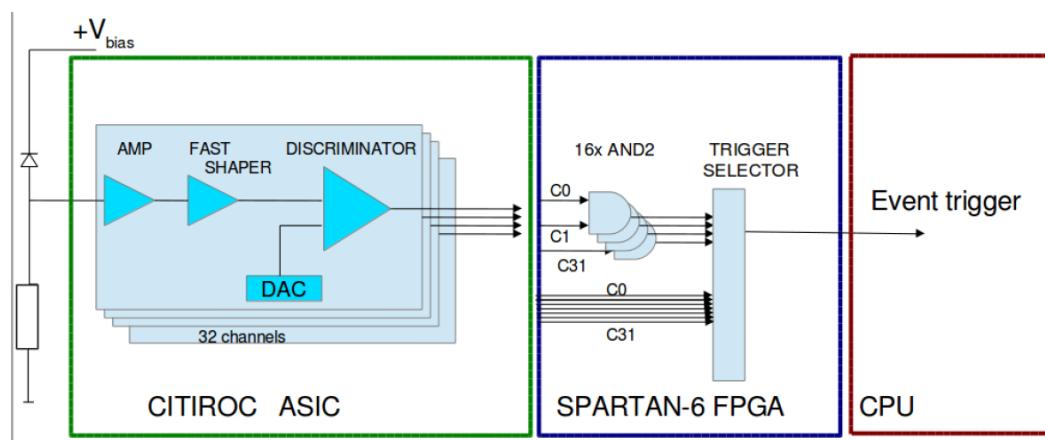

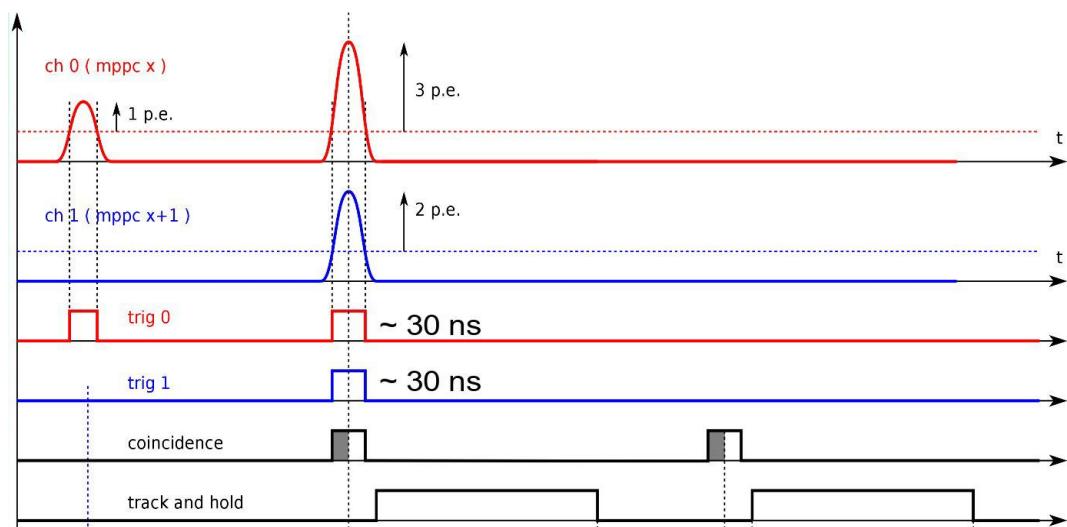

| Triggering logic.....                                                  | 21        |

| Board firmware.....                                                    | 22        |

| Bias generator and analog signal readout .....                         | 22        |

| Time stamp generator.....                                              | 23        |

| Event buffer and back-end Ethernet interface.....                      | 24        |

| Back-end communication and FEBDTP v3.0 data transmission protocol..... | 26        |

| <b>10 Test Software .....</b>                                          | <b>32</b> |

| Prerequisites.....                                                     | 32        |

| Compiling and installation .....                                       | 32        |

| Usage .....                                                            | 32        |

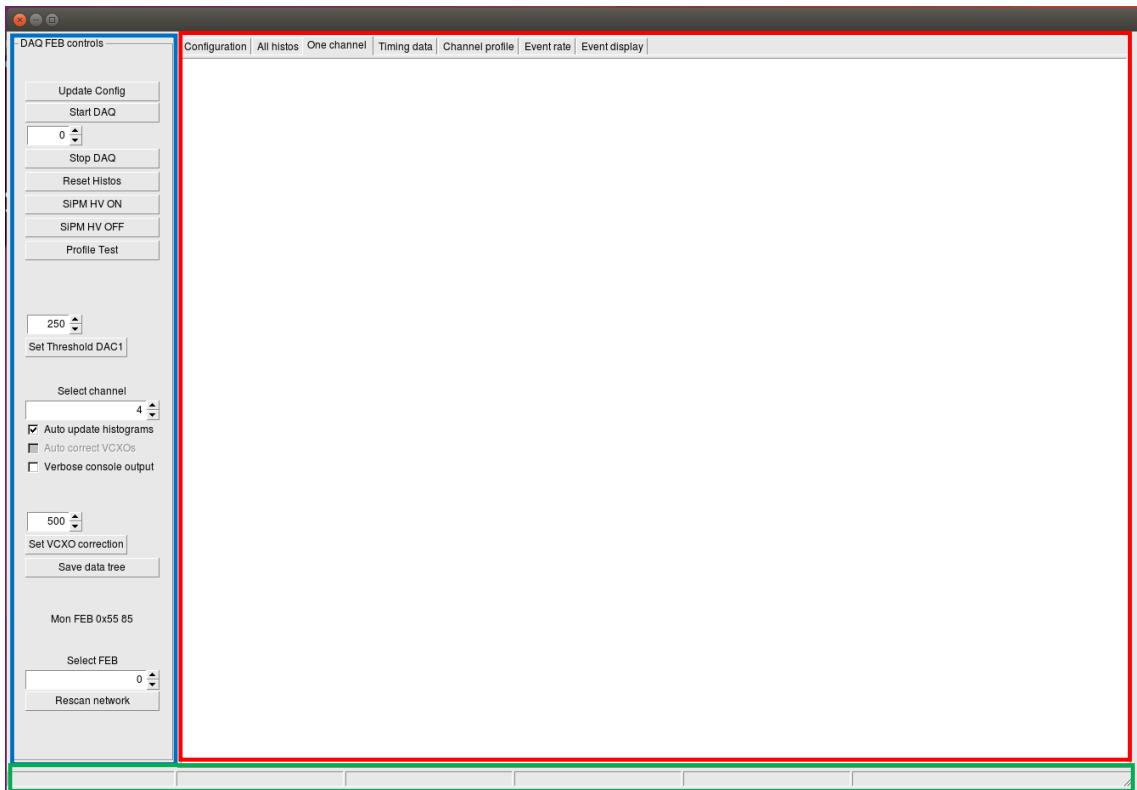

| Software interface.....                                                | 33        |

| DAQ FEB controls .....                                                 | 34        |

| Display Area .....                                                     | 35        |

| Statistics bar.....                                                    | 39        |

| DAQ using DT5702 .....                                                 | 40        |

| <b>11 Annexes .....</b>                                                | <b>43</b> |

| CITIROC Configuration files.....                                       | 43        |

| <b>12 Additional instruction for a safe use.....</b>                   | <b>47</b> |

| Electrical safety instructions .....                                   | 47        |

| EMC considerations.....                                                | 47        |

| <b>13 Instructions for Cleaning .....</b>                              | <b>49</b> |

| Cleaning the Touchscreen .....                                         | 49        |

|                                           |           |

|-------------------------------------------|-----------|

| Cleaning the air vents.....               | 49        |

| General cleaning safety precautions ..... | 49        |

| <b>14 Device decommissioning .....</b>    | <b>50</b> |

| <b>15 Disposal.....</b>                   | <b>51</b> |

| <b>16 Technical Support.....</b>          | <b>52</b> |

## List of Figures

|                                                                                                                                                                                                                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.1:PID location.....                                                                                                                                                                                                                                                                                                          | 14 |

| Figure 6.1: AC/DC power supply provided with the DT5702 module. Only the power supply adapter connector for DC input is provided with A1702.....                                                                                                                                                                                      | 15 |

| Figure 7.1: installing the A1702/DT5702.....                                                                                                                                                                                                                                                                                          | 16 |

| Figure 8.1: A1702/DT5702 general view. Main connectors and components are highlighted.....                                                                                                                                                                                                                                            | 17 |

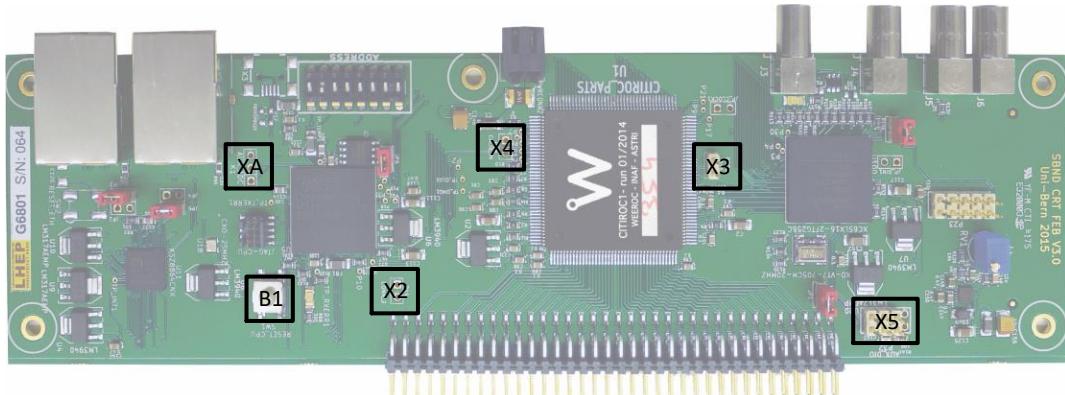

| Figure 8.2: Jumpers and bias regulator .....                                                                                                                                                                                                                                                                                          | 18 |

| Figure 8.3: Auxiliary connections and CPU reset button .....                                                                                                                                                                                                                                                                          | 19 |

| Figure 8.4: Pinout of the auxiliary connector X5.....                                                                                                                                                                                                                                                                                 | 19 |

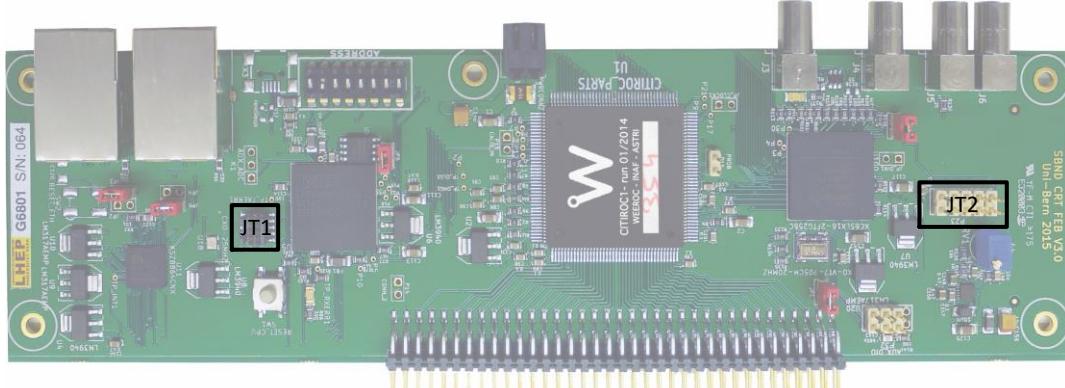

| Figure 8.5: JTAG pin headers for firmware programming .....                                                                                                                                                                                                                                                                           | 19 |

| Figure 8.6: Pinout of JTAG pin headers JT1 (on the left) and JT2 (on the right) .....                                                                                                                                                                                                                                                 | 19 |

| Figure 9.1: General block-scheme of the FEB .....                                                                                                                                                                                                                                                                                     | 20 |

| Figure 9.2: Block-scheme of the triggering circuit for even-odd adjacent channels coincidence.....                                                                                                                                                                                                                                    | 21 |

| Figure 9.3: Timing diagram of the triggering circuit. Ch0 & Ch1 coincidence logic is shown. The second event on Ch0 (red) is in coincidence with the event on Ch1 (blue) and triggers a readout cycle. .....                                                                                                                          | 21 |

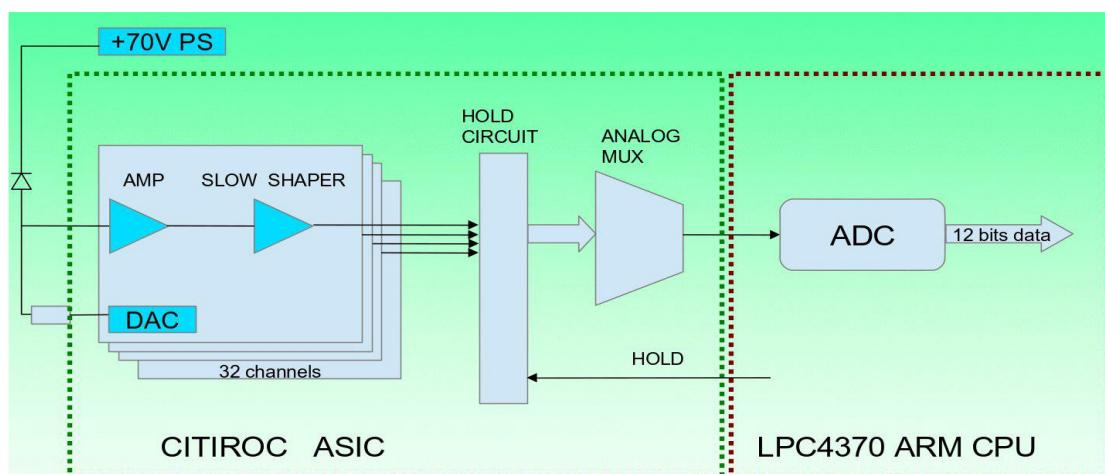

| Figure 9.4: Block-scheme of the analog signal processing circuit.....                                                                                                                                                                                                                                                                 | 22 |

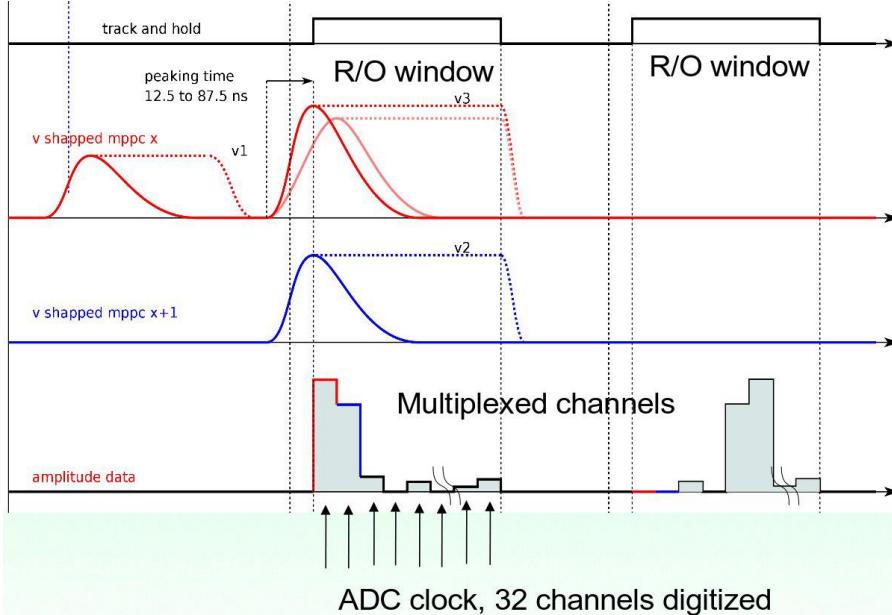

| Figure 9.5: Timing diagram of the analog signal processing circuit .....                                                                                                                                                                                                                                                              | 23 |

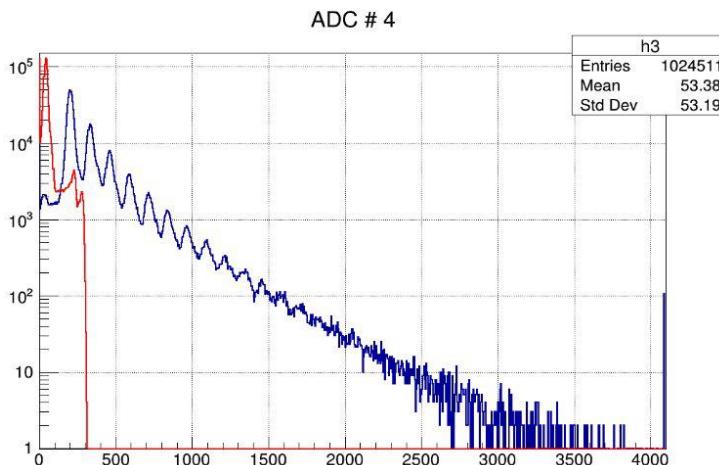

| Figure 9.6: Typical performance of analog signal processing circuit (with Hamamatsu S12825-050P-MPPC). The blue spectrum is a dark count measurement with a threshold of 0.5 p.e., while the red spectrum is obtained triggering on some other channel. .....                                                                         | 23 |

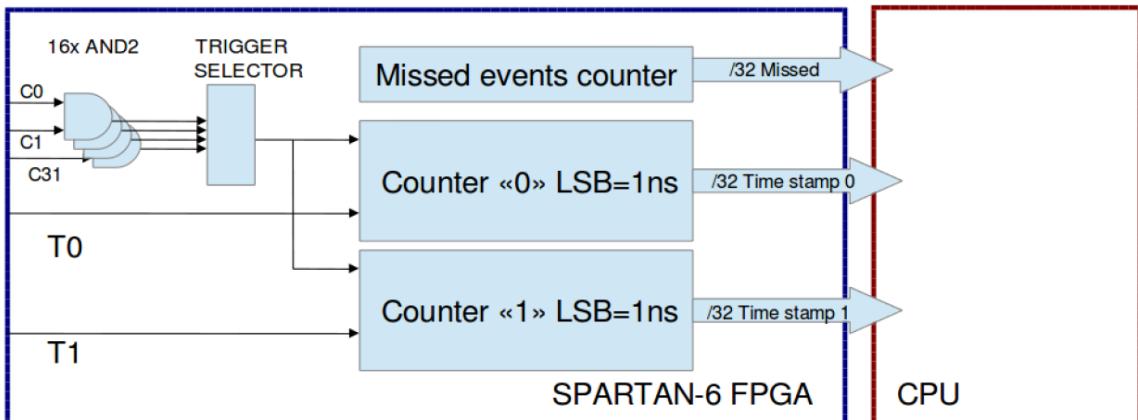

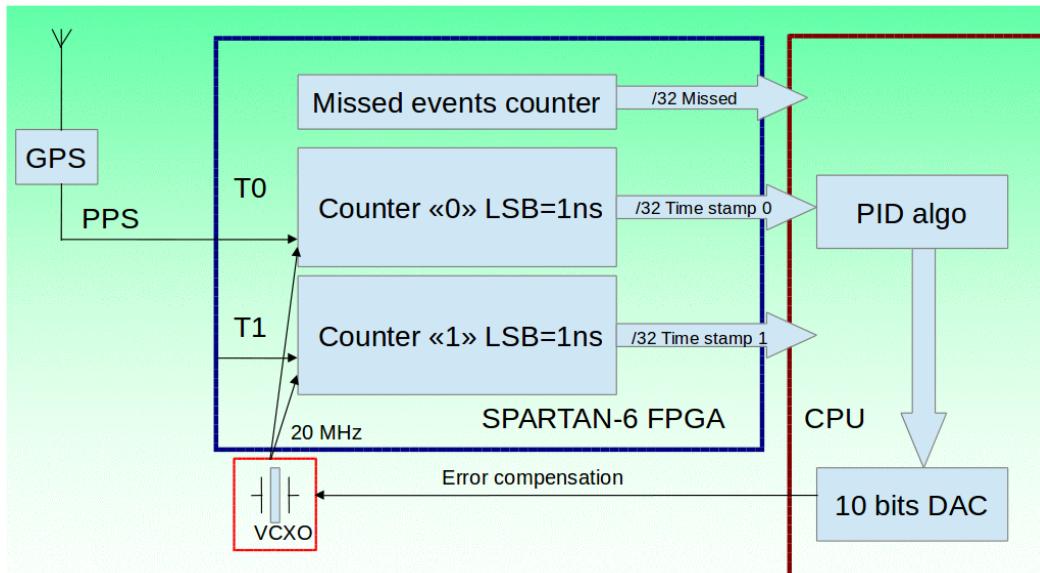

| Figure 9.7: Block-scheme of time stamp generation circuit.....                                                                                                                                                                                                                                                                        | 24 |

| Figure 9.8: Block-scheme of the oscillator control loop for the time stamp generation circuit .....                                                                                                                                                                                                                                   | 24 |

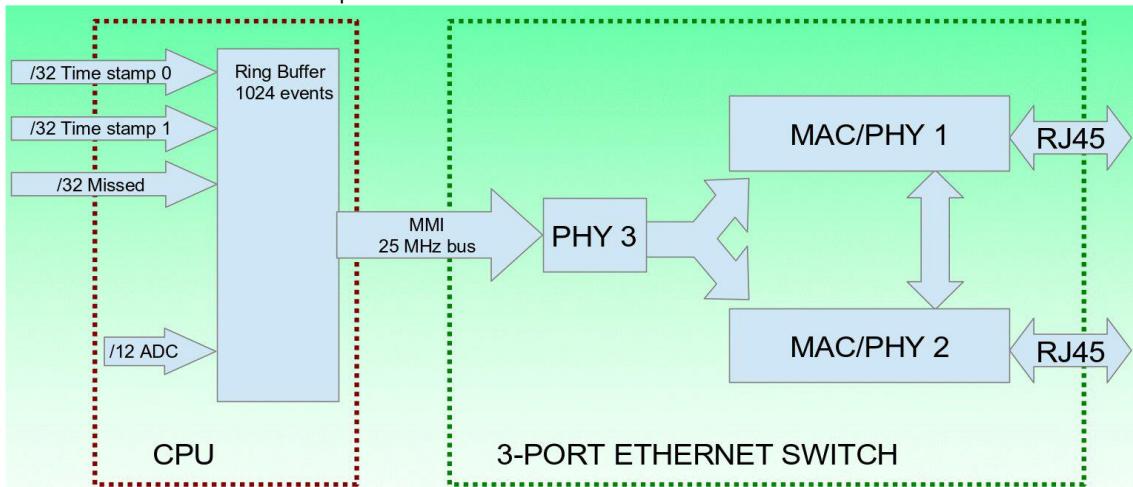

| Figure 9.9: Block-scheme of the back-end data transmission and control interface .....                                                                                                                                                                                                                                                | 25 |

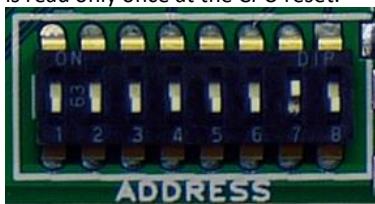

| Figure 9.10: the 8-bits MAC address switch array. The configuration shown in the picture [01000000] corresponds to MAC[5] = 0X40 .....                                                                                                                                                                                                | 25 |

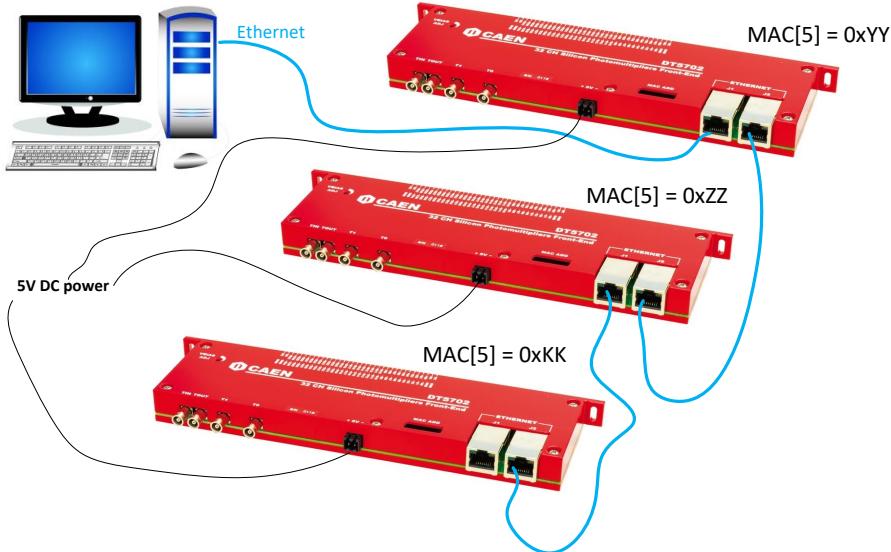

| Figure 9.11: Scheme of the FEBs daisy chain and connection to the host computer. Note that the MAC[5] byte is set differently for each board.....                                                                                                                                                                                     | 26 |

| Figure 10.1: screenshot of the Ubuntu terminal at the DAQ software startup. The MAC address and the firmware release are highlighted in red and yellow respectively.....                                                                                                                                                              | 33 |

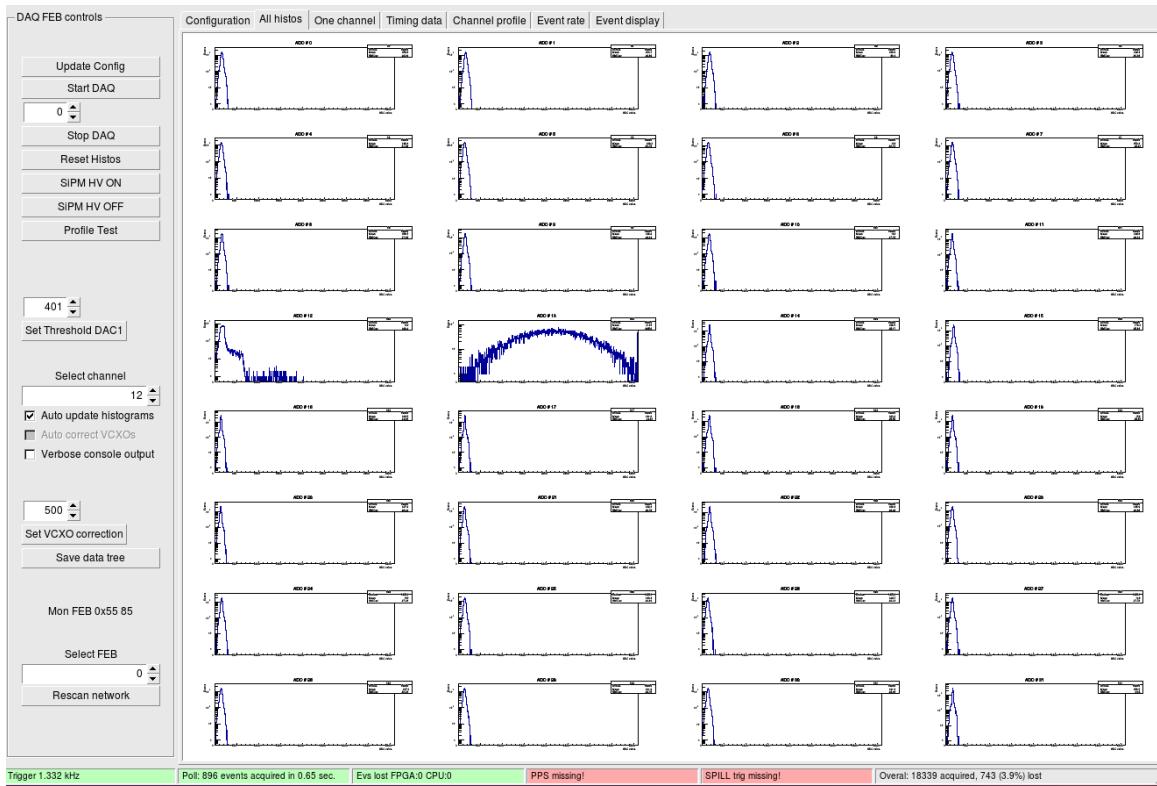

| Figure 10.2: main page of the DAQ software GUI. Its main parts are highlighted: the DAQ controls menu in blue, the display area in red and the statistics bar in green.....                                                                                                                                                           | 34 |

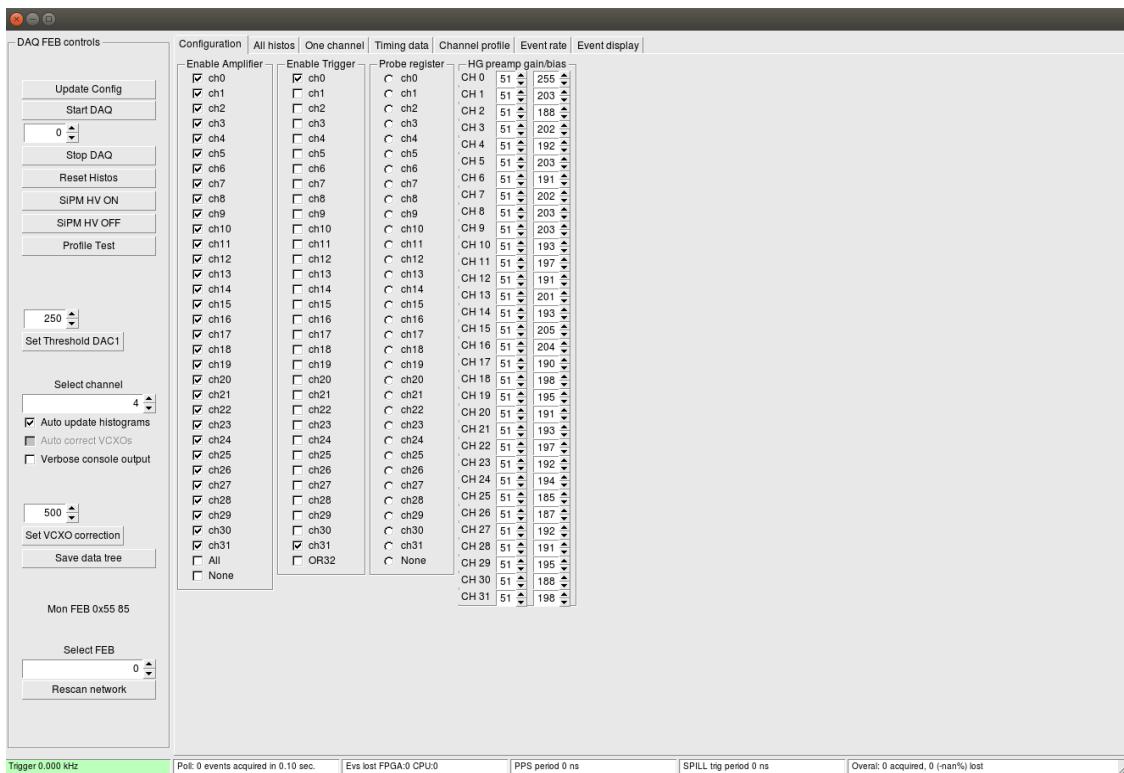

| Figure 10.3: "Configuration" tab in the GUI to control several bits of the CITIROC Slow Control register .....                                                                                                                                                                                                                        | 36 |

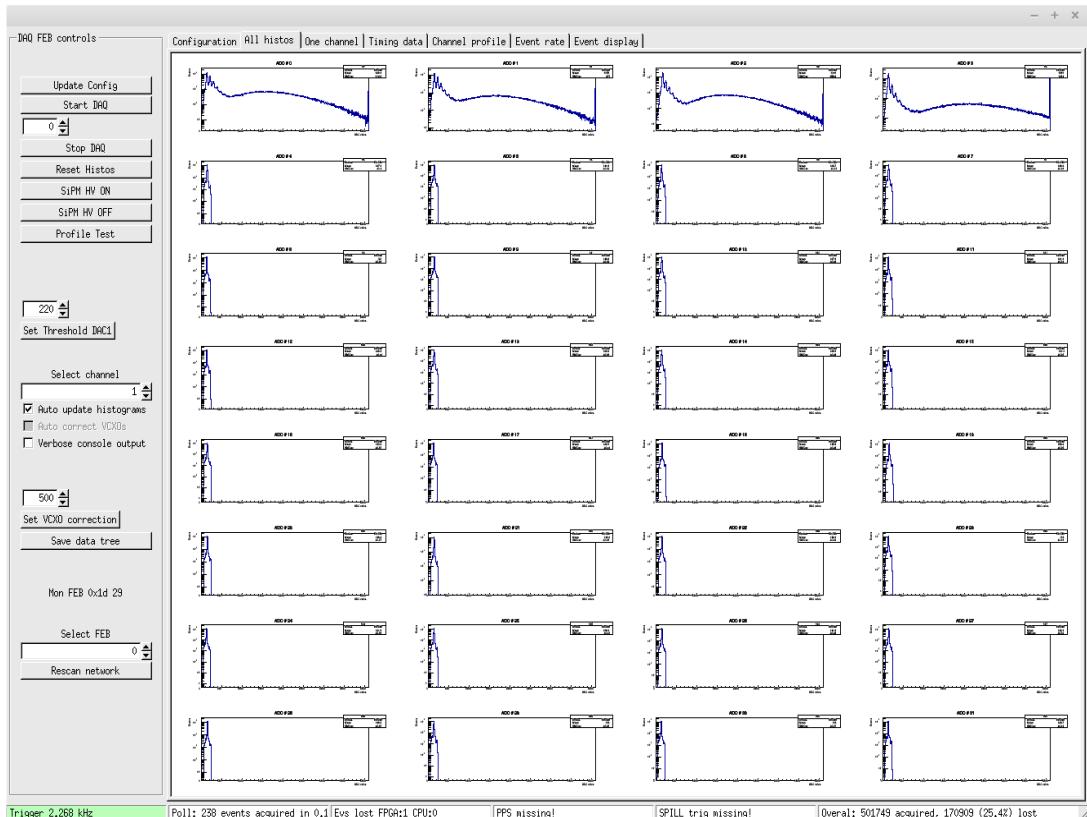

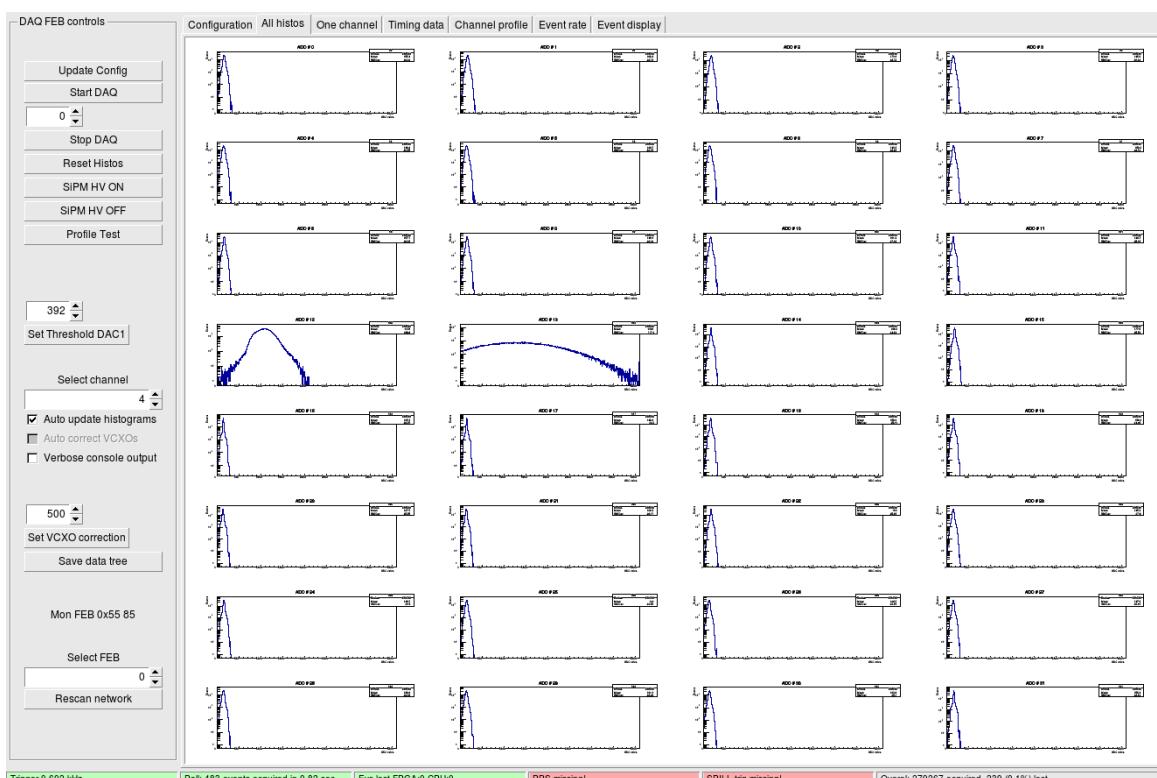

| Figure 10.4: the "All histos" tab during acquisition. Here the FPGA firmware rel FLX7.003 was used and only channels 0,1,2,3 where enabled to trigger in coincidence. Non-triggering channels are displaying their characteristic noise peak. See DAQ using DT5702 for more details.....                                              | 37 |

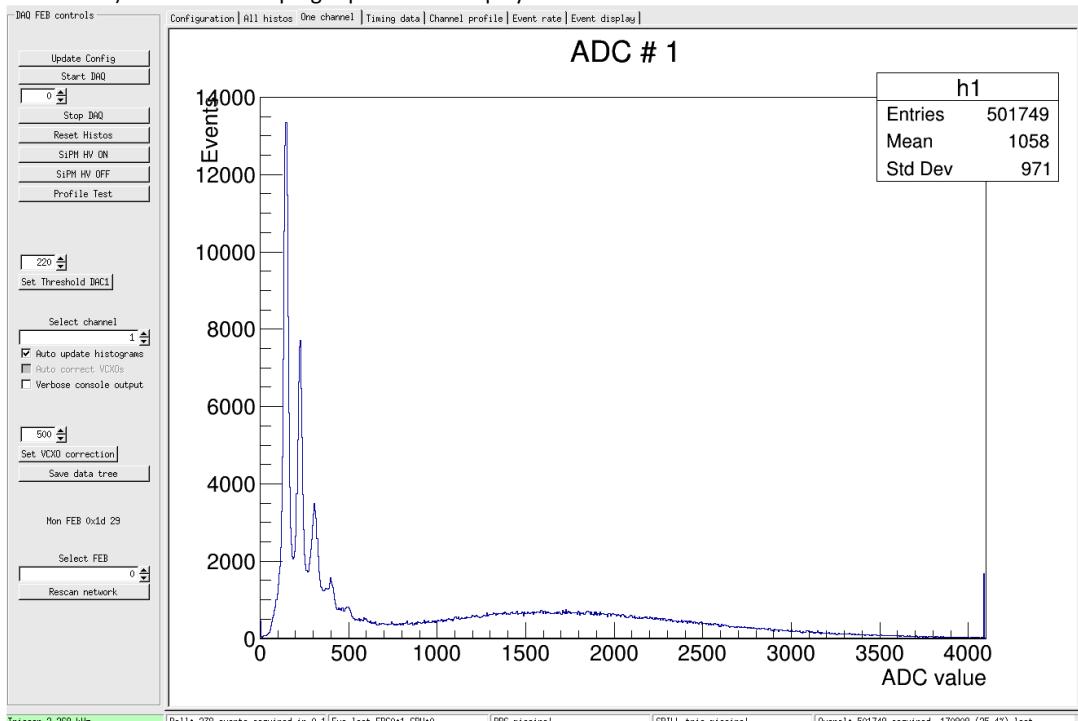

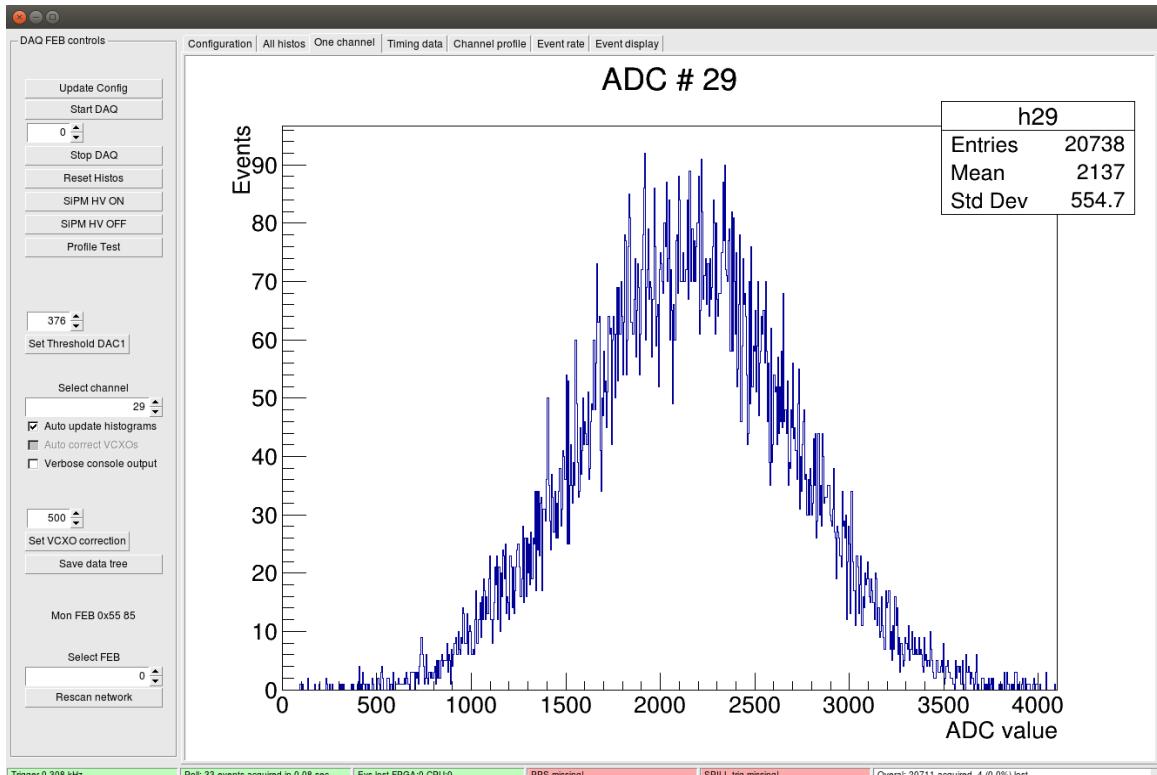

| Figure 10.5: the "One channel" tab showing the histogram of channel 1 during a DAQ. Here typical peaks generated by a SiPM are shown. ....                                                                                                                                                                                            | 37 |

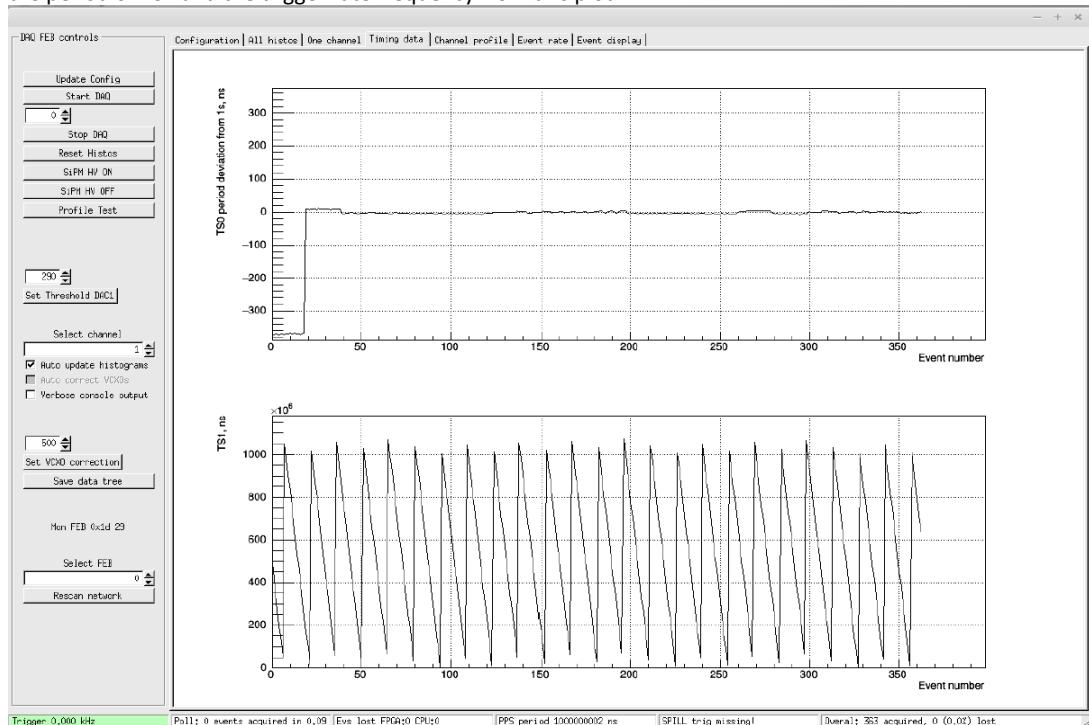

| Figure 10.6: the "Timing data" tab when a PPS timer is connected to T0 LEMO input. ....                                                                                                                                                                                                                                               | 38 |

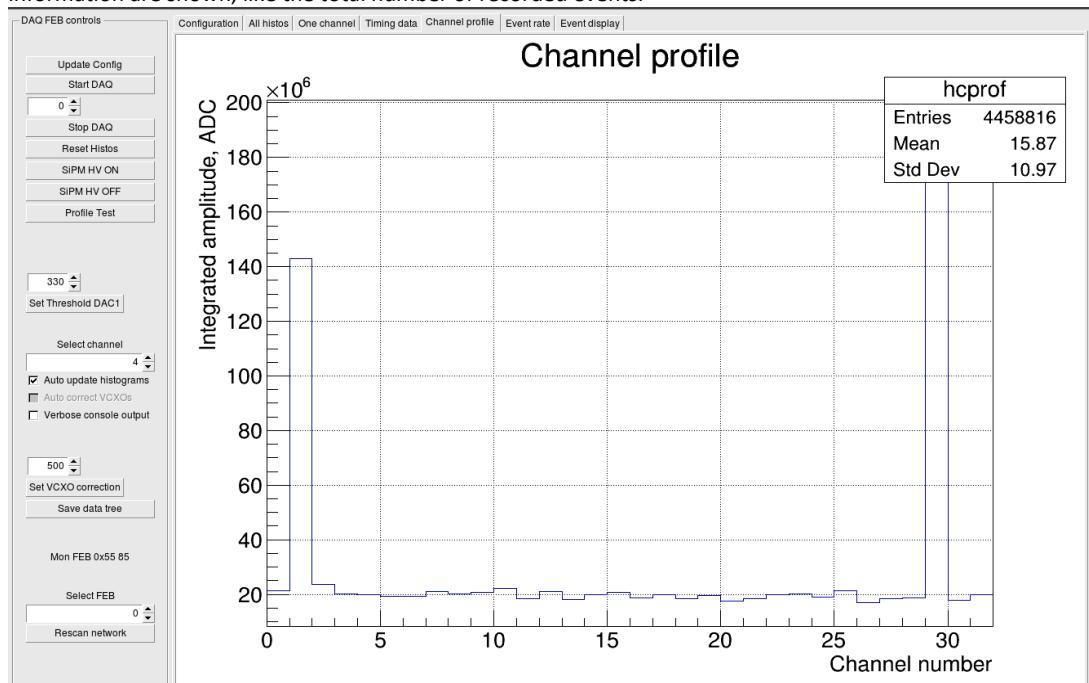

| Figure 10.7: the "Channel profile" tab when channels 1 and 29 are acquiring events in coincidence using "nfoldcoinc" FPGA software. ....                                                                                                                                                                                              | 38 |

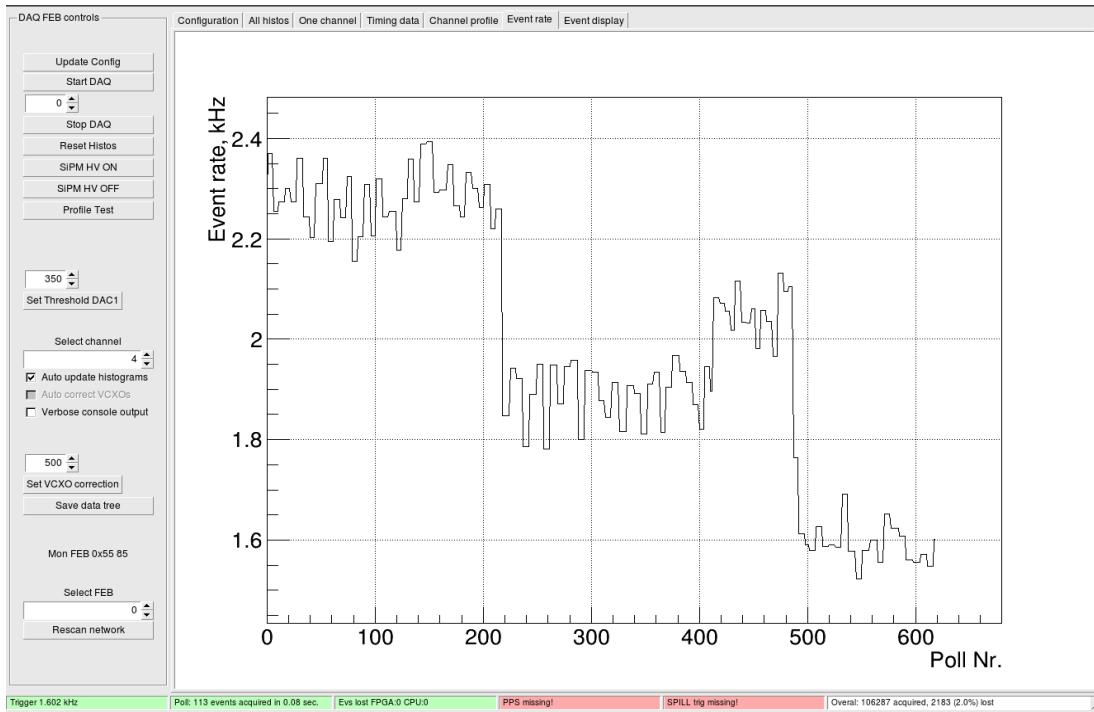

| Figure 10.8: the "Event rate" tab during DAQ, while changing the DAC1 threshold. The event rate is plotted as a function of the Poll Nr. In the bottom statistics bar it is possible to read the composition of the last transmitted poll (113 events acquired in 0.08 s). ....                                                       | 39 |

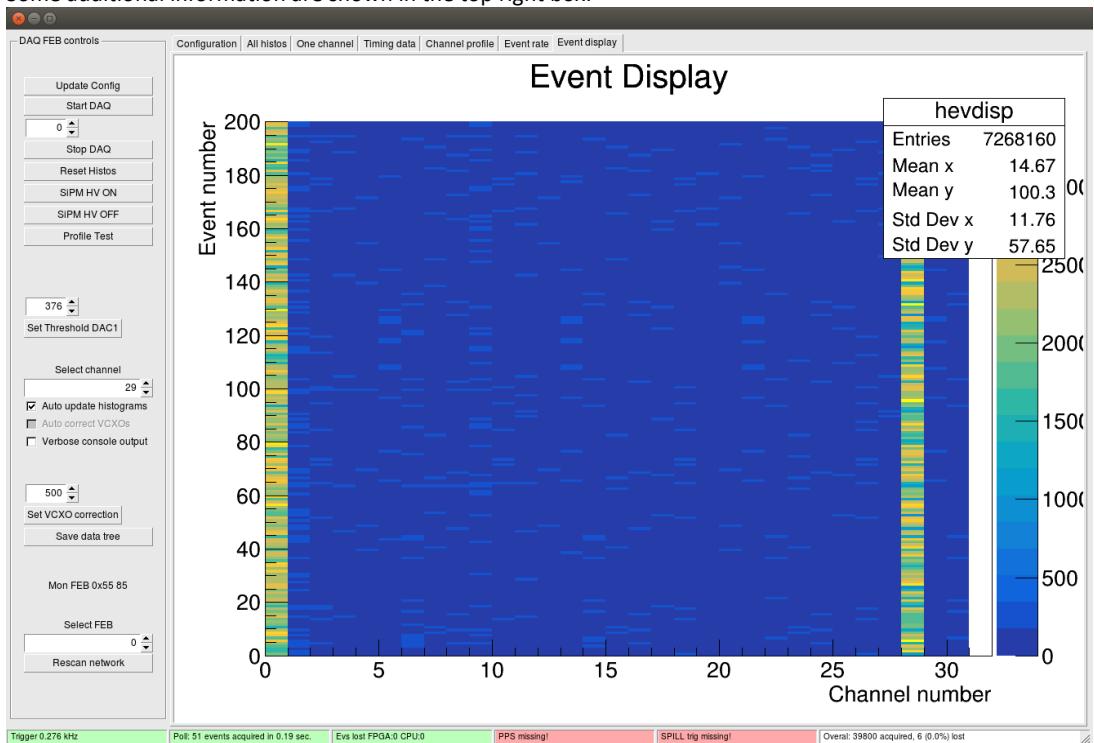

| Figure 10.9: the "Event display" tab showing the rainfall-style plot of the event number recorded by each channel. ....                                                                                                                                                                                                               | 39 |

| Figure 10.10: the statistics bar at the bottom of the GUI .....                                                                                                                                                                                                                                                                       | 40 |

| Figure 10.11: the statistics bar during different DAQs. The top bar is a DAQ performed with optimal parameters: the trigger rate is sufficiently low and a small amount of events is lost (only 2%). The bottom bar is the result of a bad set of DAQ parameters: the trigger rate is too high and many events are lost (41.9%). .... | 40 |

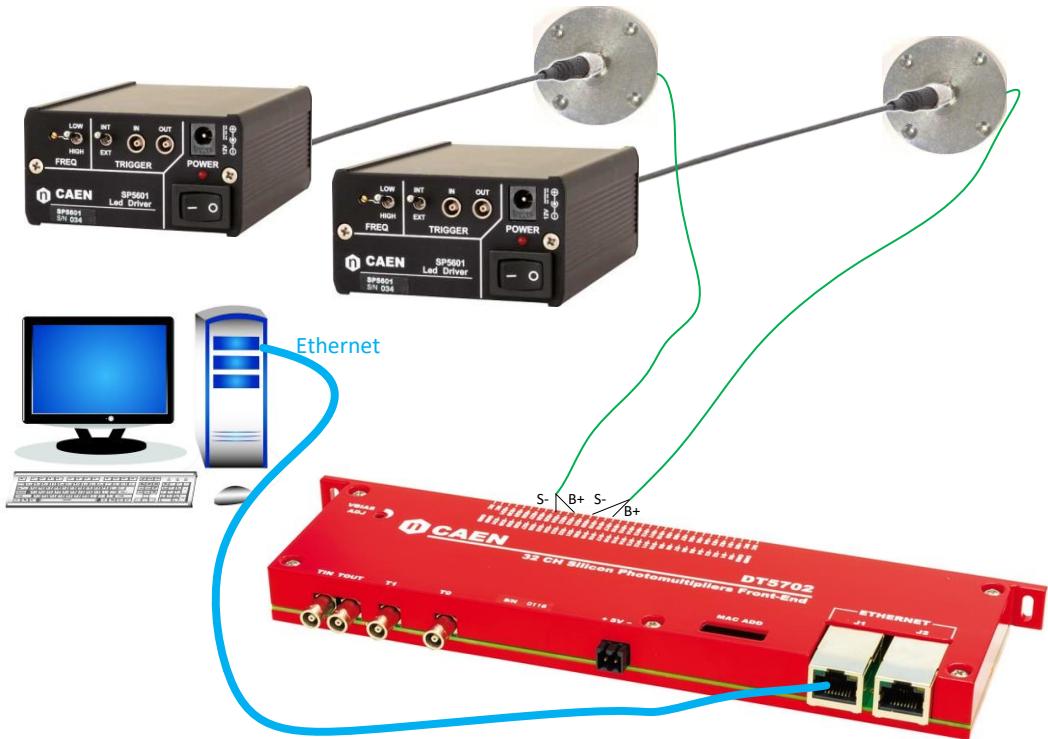

| Figure 10.12: a possible setup to perform DAQ using a CAEN DT5702 .....                                                                                                                                                                                                                                                               | 41 |

|                                                                                                                                                                                                                                                                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 10.13: DAQ of two SiPMs signals in coincidence. Triggering channels 12 and 13 are not showing any noise peak, while the other channels are clearly showing their pedestals.....                                                                                                                                                                                | 41 |

| Figure 10.14: DAQ of two SiPMs signals in "OR32" mode, using the FPGA firmware rel FLX7.003. With respect to Figure 10.13, channel 12 is showing its intrinsic low energy noise peaks. Non-triggering channels are also showing their noise peak. Note also that, w.r.t. Figure 10.13, the DAC1 threshold has been increased to avoid trigger rate massive increase.. | 42 |

| Figure 10.15: signal from a SiPM illuminated by a CAEN SP5601 LED driver. A typical SiPM peak is visible.....                                                                                                                                                                                                                                                         | 42 |

## List of Tables

|                                                                                                                                                                                                                                                    |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1.1: Available ordering options .....                                                                                                                                                                                                        | 8  |

| Table 3.1: Technical specifications of CAEN A1702/DT5702.....                                                                                                                                                                                      | 11 |

| Table 4.1: delivered kit for A1702.....                                                                                                                                                                                                            | 12 |

| Table 4.2: delivered kit for DT5702. ....                                                                                                                                                                                                          | 13 |

| Table 8.1: A1702/DT5702 main connectors and components description .....                                                                                                                                                                           | 18 |

| Table 9.1: FEBDTP V3.0 datagram structure and example. The total length of the datagram is in the range 64 to 1500 bytes.....                                                                                                                      | 26 |

| Table 9.2: Command to read ETHERNET switch control/status register. REG is the register address to read. The answer of the FEB is contained in the FEB-OK-SR command payload.....                                                                  | 27 |

| Table 9.3: Command to write ETHERNET switch control/status register. REG is the register address to be written. The content to be written is contained in the FEB-WR-SR command payload.....                                                       | 27 |

| Table 9.4: Command to read ETHERNET switch control/status, 256 registers at once. The answer of the FEB is contained in the FEB-OK-SR command payload.....                                                                                         | 27 |

| Table 9.5: Command to write ETHERNET switch control/status, 256 registers at once. The content to be written is contained in the FEB-WR-SRFF command payload. ....                                                                                 | 27 |

| Table 9.6: Command to broadcast the MAC of the host to all FEBs and to collect MACs of all FEBs into the host's client DB. It returns the firmware version string in FEB_OK data field. If RR RR >0, it sets the VCXO correction value to RR RR .. | 28 |

| Table 9.7: Acquisition control command.....                                                                                                                                                                                                        | 28 |

| Table 9.8: Command to turn SiPMs HV bias ON .....                                                                                                                                                                                                  | 28 |

| Table 9.9: Command to turn SiPMs HV bias OFF .....                                                                                                                                                                                                 | 28 |

| Table 9.10: This command requests current trigger rate from the FEB, returned as float in the first 4 bytes of Data field of FEB_OK reply.....                                                                                                     | 29 |

| Table 9.11: Command to read CITIROC Slow Control register (SR) .....                                                                                                                                                                               | 29 |

| Table 9.12: Command to write and latch CITIROC Slow Control register (SR) .....                                                                                                                                                                    | 29 |

| Table 9.13: Command to read the event buffer. The FEB_DATA_CDR message is repeated till the FEB buffer is empty. The FEB_EOF_CDR command terminates the data buffer transmission.....                                                              | 29 |

| Table 9.14: Command to read the CITIROC Probe register (PMR) .....                                                                                                                                                                                 | 29 |

| Table 9.15: Command to write and latch in the CITIROC Probe register (PMR) .....                                                                                                                                                                   | 29 |

| Table 9.16: Command to read the FPGA input flexible logic register (FIL). The 9 bytes control string is formed by 4-bytes mask1, 4-bytes mask2 and a majority byte.....                                                                            | 30 |

| Table 9.17: Command to write and latch in the FPGA input logic register (FIL) .....                                                                                                                                                                | 30 |

| Table 9.18: Command to read SPI Flash Interface content. Bytes A0-A2 define the starting address in PROM address space. Bytes N0-N1 define the number of requested blocks. The CC CC field contains the CRC code of the block. ....                | 30 |

| Table 9.19: Command to write SPI Flash Interface content. Options are specified in RR RR field. .....                                                                                                                                              | 31 |

| Table 10.1: latest firmware revision name .....                                                                                                                                                                                                    | 33 |

| Table 11.1: description of CITIROC probe register bit stream as reported in "CITIROC_PROBEbitstream.txt" .....                                                                                                                                     | 43 |

# 1 Introduction

The A1702/DT5702 Front-End Board is a custom design developed by the Albert Einstein Center for Fundamental Physics of the University of Bern for the readout of **SiPM** arrays used in the **Cosmic Rays veto** of Liquid Argon Neutrino Experiments. The board is designed for the exact purpose of detecting **coincidences at the far ends of scintillating fibers coupled with SiPMs** and measure the signal energy as well as the time of arrival for track reconstruction.

The device is designed to operate in laboratory environment under the supervision of skilled technicians.

The analog input signal is processed by CITIROC, a 32-channel ASIC from WeeROC. Each channel is made of a high-gain charge preamplifier (x 10 – x 600 gain range), fast shaping with the shaping time of 15 ns and slow shaping with configurable shaping time in the range of 12.5 ns to 87.5 ns. Signals from the fast shapers are discriminated (programmable threshold) and produce digital signals (T0-T31) for event triggering. These signals are then combined in the FPGA to give coincidence triggers. The input signals height can be stored in the ASIC Sample-and-Hold (S/H) circuit and multiplexed to a single analog output. This output is routed to an external ADC for sampling and energy list decoding.

The board allows to perform timing measurements, thanks to external reference signals to be fed at the dedicated LEMO inputs. Using very stable signals, like PPS pulses, it is possible to reach timing resolution down to 1 ns. Additional T-IN/T-OUT connectors for board-to-board trigger validation are also available.

The board communicates with the host computer through Ethernet protocol, relying on a ROOT-based demo software running on Linux.

Available board models are listed below.

| Ordering options |                                               |  |              |

|------------------|-----------------------------------------------|--|--------------|

| A1702            | 32-channel SiPM readout Front-End Board       |  | WA1702XAAAAA |

| DT5702           | 32-channel SiPM readout Front-End Board BOXED |  | WDT5702XAAAA |

**Table 1.1:** Available ordering options

(\*) <https://www.weeroc.com>

## 2 Safety Notices

**N.B. Read carefully the “Precautions for Handling, Storage and Installation” document provided with the product before starting any operation.**

The following HAZARD SYMBOLS may be reported on the unit:

|                                                                                     |                                   |

|-------------------------------------------------------------------------------------|-----------------------------------|

|    | Caution, refer to product manual  |

|    | Caution, risk of electrical shock |

|    | Protective conductor terminal     |

|   | Earth (Ground) Terminal           |

|  | Alternating Current               |

|  | Three-Phase Alternating Current   |

The following symbol may be reported in the present manual:

|                                                                                     |                           |

|-------------------------------------------------------------------------------------|---------------------------|

|  | General warning statement |

|-------------------------------------------------------------------------------------|---------------------------|

The symbol could be followed by the following terms:

- **DANGER:** indicates a hazardous situation which, if not avoided, will result in serious injury or death.

- **WARNING:** indicates a hazardous situation which, if not avoided, could result in death or serious injury.

- **CAUTION:** indicates a situation or condition that, if not avoided, could cause physical injury or damage the product and / or its environment.

To avoid potential hazards, use the product only as specified. Only qualified personnel should perform service procedures.

**Avoid Electric Overload.** To avoid electric shock or fire hazard, do not power a load outside of its specified range.

**Avoid Electric Shock.** To avoid injury or loss of life, do not connect or disconnect cables while they are connected to a voltage source.

**Do Not Operate without Covers.** To avoid electric shock or fire hazard, do not operate this product with covers or panels removed.

**Do Not Operate in Wet/Damp Conditions.** To avoid electric shock, do not operate this product in wet or damp conditions.

**Do Not Operate in an Explosive Atmosphere.** To avoid injury or fire hazard, do not operate this product in an explosive atmosphere.

**Do Not Operate with Suspected Failures.** If you suspect this product to be damaged, please contact Technical Support.

## Important notice

**CAUTION:** do not perform tests measuring the effective bias voltage on the strip connector with a voltmeter.

**THE POTENTIAL RISK OF DAMAGING THE INTERNAL INPUT LINES EXISTS

IF THE OPERATING INSTRUCTIONS ARE NOT FOLLOWED!**

### 3 Technical Specifications

|                                |                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                              |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>ANALOG INPUTS</b>           | <b>Number of Channels</b><br>32 channels<br>Based on Weeroc CITIROC1A                                                                                                                                                                                                         | <b>Connector</b><br>72-pin, 2-row, 2.54 mm header strip                                                                                                                                                      |

| <b>TEST FUNCTION</b>           | One pulser per channel with programmable 16-bit pattern (fixed amplitude)                                                                                                                                                                                                     |                                                                                                                                                                                                              |

| <b>BIAS VOLTAGE</b>            | <b>Common bias</b><br>20 V to 90 V                                                                                                                                                                                                                                            | <b>Single-channel fine adjustment</b><br>+0.5 V to 4.5 V                                                                                                                                                     |

| <b>PREAMPLIFIER</b>            | <b>Configurable gain</b><br>x10 – x600 range                                                                                                                                                                                                                                  |                                                                                                                                                                                                              |

| <b>SHAPER</b>                  | <b>Fast shaping time</b><br>15 ns                                                                                                                                                                                                                                             |                                                                                                                                                                                                              |

|                                | <b>Slow shaping time</b><br>12.5 ns to 87.5 ns                                                                                                                                                                                                                                |                                                                                                                                                                                                              |

| <b>DISCRIMINATOR</b>           | From 0 to 50 SiPM photoelectrons<br>- 10-bit DAC common threshold<br>- 4-bits DAC for single-channel fine adjustment                                                                                                                                                          |                                                                                                                                                                                                              |

| <b>TIMING RESOLUTION</b>       | Up to 1 ns<br><b>Test conditions:</b> PPS external reference signal with at least 1 ns precision<br><b>Note:</b> if not using external timing reference, the internal TDC is running at 250 MHz clock frequency, thus giving 4ns resolution on the trigger timestamp          |                                                                                                                                                                                                              |

| <b>DIGITAL CONVERSION</b>      | 80 Ms/s , 12 bits ADC                                                                                                                                                                                                                                                         |                                                                                                                                                                                                              |

| <b>DIGITAL I/O</b>             | <b>TIN</b> (LEMO)<br>Validation input                                                                                                                                                                                                                                         | <b>TOUT</b> (LEMO)<br>Output pulse<br>3.3 LVCMOS                                                                                                                                                             |

| <b>TRIGGER</b>                 | <b>Internal Trigger</b><br>OR32 mode or channel pairs coincidences                                                                                                                                                                                                            | <b>Validation trigger</b><br>Only the events that falls inside the validation windows given at TIN are considered valid.                                                                                     |

| <b>MEMORY BUFFER</b>           | up to 1024 events                                                                                                                                                                                                                                                             |                                                                                                                                                                                                              |

| <b>COMMUNICATION INTERFACE</b> | 100 Mbps Ethernet links                                                                                                                                                                                                                                                       |                                                                                                                                                                                                              |

| <b>MULTI BOARDS CONNECTION</b> | Daisy-chain of up to 256 units into one network interface                                                                                                                                                                                                                     |                                                                                                                                                                                                              |

| <b>SOFTWARE</b>                | User interface is a demo CERN ROOT script running on Linux<br><br>*tested with ROOT 6.10/02 on Ubuntu 16.04 OS – 64 bit                                                                                                                                                       |                                                                                                                                                                                                              |

| <b>MECHANICAL</b>              | <b>Form Factor</b><br>A1702<br>DT5702 – Desktop                                                                                                                                                                                                                               | <b>Dimension</b><br>218x16x62.5 mm <sup>3</sup> (WxHxL) - including connectors<br>230x20x80 mm <sup>3</sup> (WxHxL) - including connectors                                                                   |

| <b>ENVIRONMENTAL</b>           | <b>Environment:</b><br><b>Operating Temperature:</b><br><b>Storage Temperature:</b><br><b>Operating Humidity:</b><br><b>Storage Humidity:</b><br><b>Altitude:</b><br><b>Pollution Degree:</b><br><b>Overtoltage Category:</b><br><b>EMC Environment:</b><br><b>IP Degree:</b> | Indoor use<br>0°C to +40°C<br>-10°C to +60°C<br>10% to 90% RH non condensing<br>5% to 90% RH non condensing<br>< 2000m<br>2<br>II<br>Commercial and light industrial<br>IPX0 Enclosure, not for wet location |

| <b>REGULATORY COMPLIANCE</b>   | <b>EMC</b><br>CE 2014/30/EU Electromagnetic Compatibility Directive                                                                                                                                                                                                           | <b>Safety</b><br>CE 2014/35/EU Low Voltage Directive                                                                                                                                                         |

| <b>POWER REQUIREMENTS</b>      | @ +5V<br>0.550 A (max.)                                                                                                                                                                                                                                                       |                                                                                                                                                                                                              |

Table 3.1: Technical specifications of CAEN A1702/DT5702.

## 4 Packaging and compliancy

The A1702 is a bare PCB board - 218/16/62.5 mm<sup>3</sup> (including connectors) W/H/L - The system is provided as OEM device without any enclosure in order to be easily integrated in the final experimental setup.

**A1702 is an ESD sensitive item. Handling without ESD protective covering shall be performed only into approved ESD Protected Area (EPAs)**

**A1702 complies with the EMC directive only if installed in a CE marked system**

The DT5702 is a Desktop module housed in an aluminium case – 230/20/80 mm<sup>3</sup> (W/H/L).

The unit is inspected by CAEN before the shipment, and it is guaranteed to leave the factory free of mechanical or electrical defects.

When receiving the unit, the user is strictly recommended to inspect for any damage which may have occurred during transportation. Particularly, inspect for exterior damages like broken connectors and check that the panel is not scratched or cracked.

All packing material should be held on until the inspection has been completed. If damage is detected, the user must file a claim with the carrier immediately and notify CAEN.

Before installing the unit, make sure to read thoroughly the safety rules and installation requirements (Sec. **Safety Notices**), then place the package content onto your bench.

The content of the delivered package standardly consists of the part list shown in the table below ( **Table 4.1 and Table 4.2** ). All the official documentation, firmware updates, software tools, and accessories are available on [www.caen.it](http://www.caen.it) at the product web page.

|  | Part                                            | Description                                                | Qty |

|--|-------------------------------------------------|------------------------------------------------------------|-----|

|  | A1702                                           | 32 Channel SiPM Readout Board for Cosmic Rays Veto         | x1  |

|  | WEIDMULLER Omnimate series BL 3.50/02/180 SN BX | Connector for DC input. Female plug 3.50 mm, 2 poles, 180° | x1  |

|  | User guide                                      | UM5833 – A1702/DT5702 User Manual                          | x1  |

**Table 4.1:** delivered kit for A1702.

|  | Part               | Description                                              | Qty |

|--|--------------------|----------------------------------------------------------|-----|

|  | DT5702             | 32 Channel SiPM Readout Board for Cosmic Rays Veto BOXED | x1  |

|  | Power supply cable | Standard C13 power supply chord                          | x1  |

|                                                                                   |                 |                                                                                                 |    |

|-----------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------|----|

|  | AC/DC converter | 220-110 V to 5V,3A AC/DC stabilized power supply with WEIDMULLER female connector 2P 1615670000 | x1 |

|  | User guide      | UM5833 – A1702/DT5702 User Manual                                                               | x1 |

Table 4.2: delivered kit for DT5702.

**CAUTION:** to manage the product, consult the operating instructions provided.

It is recommended to:

- Inspect containers for damage during shipment. Report any damage to the freight carrier for possible insurance claims.

- Check that all the components received match those listed on the enclosed packing list. (CAEN cannot accept responsibility for missing items unless we are notified promptly of any discrepancies.)

- Open shipping containers; be careful not to damage contents.

- Inspect contents and report any damage. The inspection should confirm that there is no exterior damage to the unit such as broken knobs or connectors and that the front panel and display face are not scratched or cracked. Keep all packing material until the inspection has been completed.

- If damage is detected, file a claim with carrier immediately and notify CAEN service.

- If equipment must be returned for any reason, carefully repack equipment in the original shipping container with original packing materials if possible. Please contact CAEN service.

- If equipment is to be installed later, place equipment in original shipping container and store in a safe place until ready to install

**DO NOT SUBJECT THE ITEM TO UNDUE SHOCK OR VIBRATIONS**

**DO NOT BUMP, DROP OR SLIDE SHIPPING CONTAINERS**

**DO NOT LEAVE ITEMS OR SHIPPING CONTAINERS UNSUPERVISED IN AREAS WHERE UNTRAINED PERSONNEL MAY MISHANDLE THE ITEMS**

**USE ONLY ACCESSORIES WHICH MEET THE MANUFACTURER SPECIFICATIONS**

## 5 PID (Product Identifier)

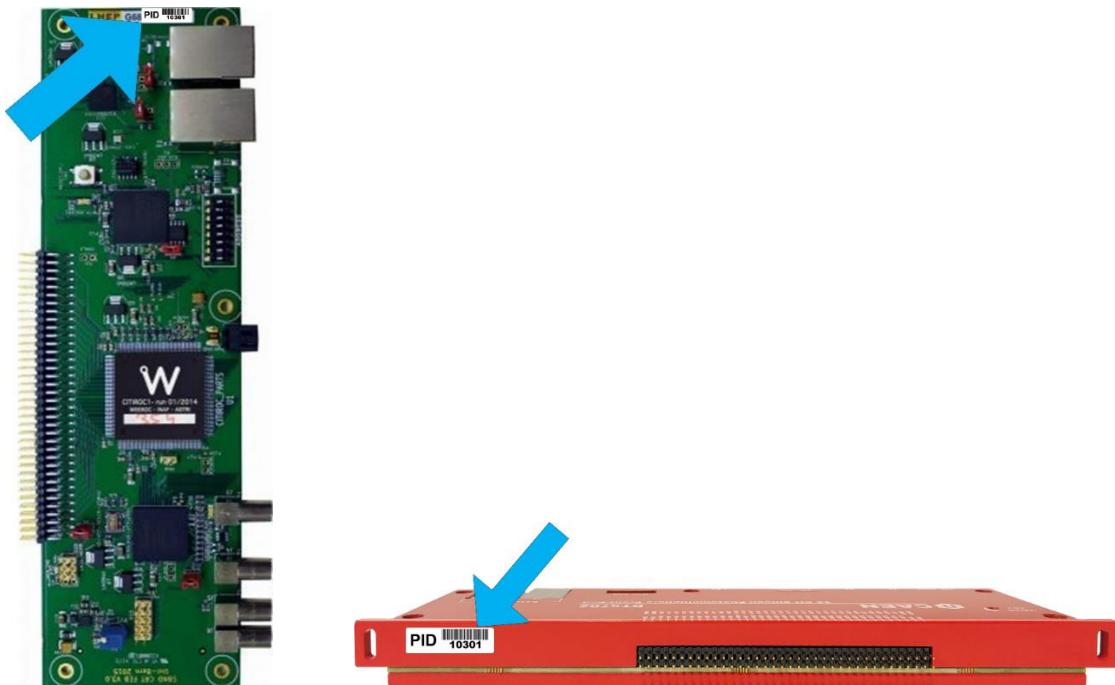

PID is the CAEN product identifier, an incremental number greater than 10000 that is unique for each product. The PID is on a label affixed to the product (Errore. L'origine riferimento non è stata trovata.).

**Figure 5.1:**PID location.

## 6 Power Requirements

The CAEN A1702/DT5702 standalone module is powered by an external AC/DC stabilized power supply. The AC/DC power supply is provided with the DT5702 board and included in the delivered kit. Only the power supply adapter connector WEIDMULLER 2P 1615670000 is provided with the A1702.

Input: 100-240 V AC, 47-63 Hz; Output: 5.0 V, 3.3 A. The typical power consumption is 0.8 A (@ +5 V).

**Note.:** Using a different power supply source, like battery or linear type, it is recommended the source to provide +5 V and, at least, 1.5 A.

**Figure 6.1:** AC/DC power supply provided with the DT5702 module. Only the power supply adapter connector for DC input is provided with A1702.

## 7 Installing the device

- Connect a compatible power supply to the DC input.

A suitable AC/DC converter is delivered together with the DT5702 board, while an external one should be used for A1702. Please check Chap. **Power Requirements** before powering on the A1702.

Figure 7.1: installing the A1702/DT5702.

**ONLY QUALIFIED PERSONNEL SHOULD PERFORM INSTALLATION, OPERATIONS**

**DO NOT INSTALL THE EQUIPMENT SO THAT IT IS DIFFICULT TO OPERATE THE ON/OFF SWITCH ONBOARD**

**IT IS RECOMMENDED THAT THE SWITCH OR CIRCUIT-BREAKER IS NEAR THE EQUIPMENT**

**THE SAFETY OF ANY SYSTEM THAT INCORPORATES THE DEVICE IS UNDER THE RESPONSIBILITY OF THE ASSEMBLER OF THE SYSTEM**

Do not use the device and contact technical support if one of these situations is verified:

- Enclosure integrity is compromised

- Insulation of HV chord is damaged (if present)

- The indication led or display is not performing as required (e.g. led not working, display with incorrect graphic)

- Fans are not working (if present)

## 8 Hardware Description

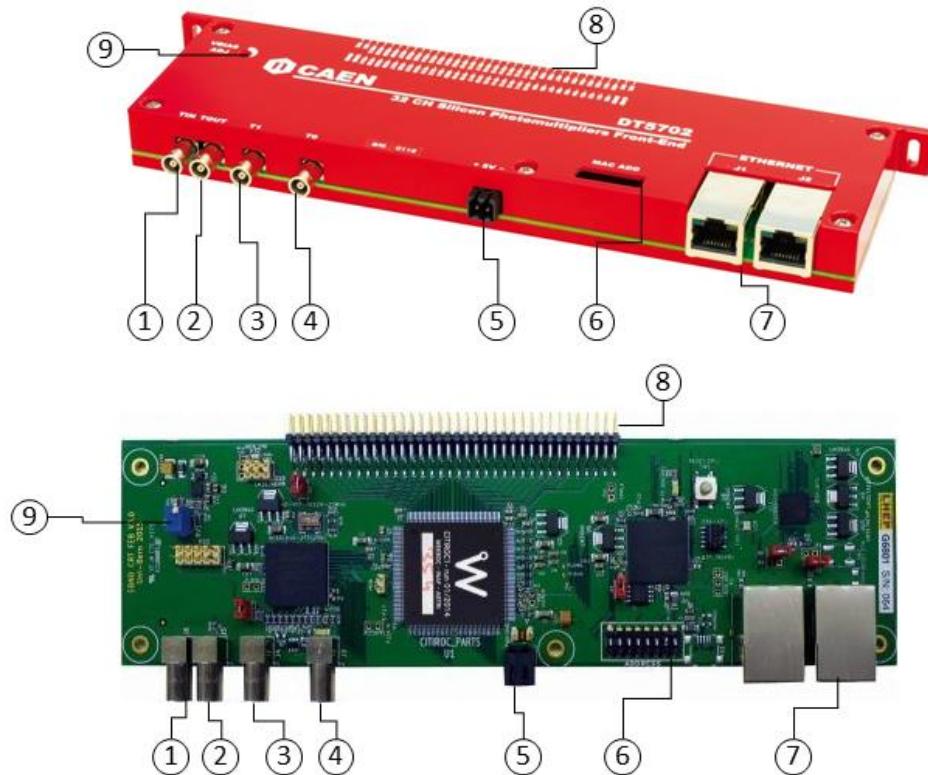

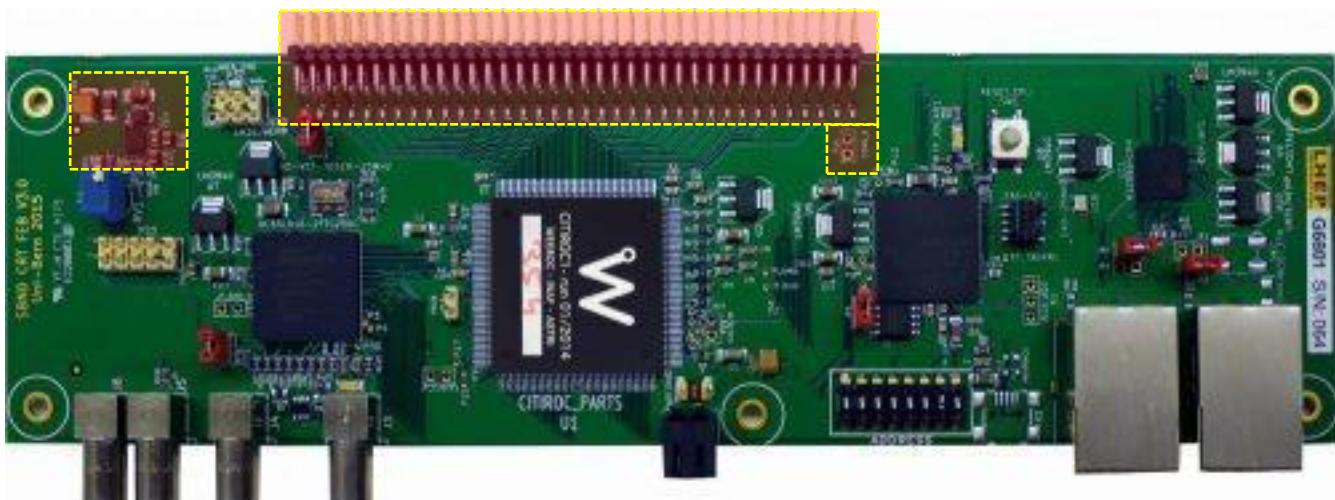

Figure 8.1: A1702/DT5702 general view. Main connectors and components are highlighted

| Number | Connector                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | LEMO                                                 | <b>TIN.</b> Trigger validation input, LVCMOS 3.3V. TIN can be configured to 3.3V or 1.2V LVCMOS logic by mounting one of the shortcut resistors at the backside of the board (R131 and R132). As default, R131 is mounted for 1.2V LVCMOS.<br><br>This input has a pull-up resistor on-board to allow operation without external signal supplied. If using an external signal on TIN, it is recommended to use a 50 Ω termination for correct board operation. |

| 2      | LEMO                                                 | <b>TOUT.</b> Trigger validation output, LVCMOS 3.3V, 25 Ω                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3      | LEMO                                                 | <b>T1.</b> Timing reference input signal, LVCMOS 3.3V high-impedance. By default, not terminated; the termination resistor (R138) can be mounted to its corresponding footprints at the top side of the board.                                                                                                                                                                                                                                                 |

| 4      | LEMO                                                 | <b>T0.</b> Timing reference input signal, LVCMOS 3.3V high-impedance. By default, not terminated; the termination resistor (R137) can be mounted to its corresponding footprints at the top side of the board.                                                                                                                                                                                                                                                 |

| 5      | WEIDMULLER Omnimate series BL 3.50/02/90             | <b>+5V DC input.</b> Male plug 3.50 mm, 2 poles, 90°. The range of the supply is from 4.5V to 5.5V. The current consumption varies depending on the event rate up to a maximum of 510 mA.                                                                                                                                                                                                                                                                      |

| 6      | n/a                                                  | <b>MAC Address switch.</b> It is used to set the last XX byte of the board MAC address: 00:60:37:12:34:XX.                                                                                                                                                                                                                                                                                                                                                     |

| 7      | Dual RJ45                                            | <b>Communication port</b> – 100 Mbps Ethernet sockets for connection to CAT5 twisted pair copper cable. Both ports are identical in terms of functionality. The dual socket can be used for daisy-chaining multiple board into a unique network                                                                                                                                                                                                                |

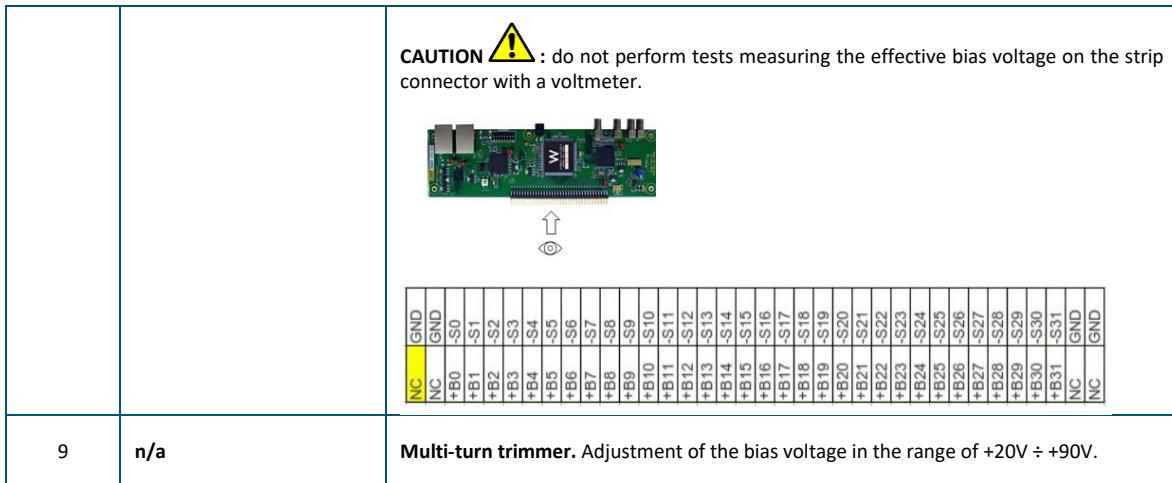

| 8      | STRIP M.D.D.SMD P2.54 36X2 TSM-136-01-L-DH-LC SAMTEC | <b>Input connector.</b> Pinout given below refers to the front view of the input connector. "NC" stands for Not Connected, "GND" pins are connected to common GND plane of the board, 32 "+B" and "-S" signals are positive bias and signal lines respectively. "+B" lines must be connected to cathodes of the SiPMs and "-S" line to the anodes.                                                                                                             |

|           |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |     |    |     |     |     |     |    |     |    |     |     |     |     |     |    |     |     |     |    |     |     |     |     |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |    |     |

|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|----|-----|-----|-----|-----|----|-----|----|-----|-----|-----|-----|-----|----|-----|-----|-----|----|-----|-----|-----|-----|------|-----|------|------|------|------|------|------|------|------|------|-----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|------|------|------|------|------|------|------|------|------|-----|------|------|------|------|------|------|----|-----|

|           |      | <p><b>CAUTION</b>  : do not perform tests measuring the effective bias voltage on the strip connector with a voltmeter.</p>  <table border="1"> <tr> <td><b>NC</b></td><td>GND</td></tr> <tr> <td>NC</td><td>GND</td></tr> <tr> <td>+B0</td><td>-S0</td></tr> <tr> <td>+B1</td><td>S1</td></tr> <tr> <td>+B2</td><td>S2</td></tr> <tr> <td>+B3</td><td>-S3</td></tr> <tr> <td>+B4</td><td>-S4</td></tr> <tr> <td>+B5</td><td>S5</td></tr> <tr> <td>+B6</td><td>-S6</td></tr> <tr> <td>+B7</td><td>S7</td></tr> <tr> <td>+B8</td><td>-S8</td></tr> <tr> <td>+B9</td><td>-S9</td></tr> <tr> <td>+B10</td><td>S10</td></tr> <tr> <td>+B11</td><td>-S11</td></tr> <tr> <td>+B12</td><td>-S12</td></tr> <tr> <td>+B13</td><td>-S13</td></tr> <tr> <td>+B14</td><td>-S14</td></tr> <tr> <td>+B15</td><td>S15</td></tr> <tr> <td>+B16</td><td>-S16</td></tr> <tr> <td>+B17</td><td>-S17</td></tr> <tr> <td>+B18</td><td>-S18</td></tr> <tr> <td>+B19</td><td>-S19</td></tr> <tr> <td>+B20</td><td>-S20</td></tr> <tr> <td>+B21</td><td>-S21</td></tr> <tr> <td>+B22</td><td>-S22</td></tr> <tr> <td>+B23</td><td>S23</td></tr> <tr> <td>+B24</td><td>-S24</td></tr> <tr> <td>+B25</td><td>-S25</td></tr> <tr> <td>+B26</td><td>-S26</td></tr> <tr> <td>+B27</td><td>-S27</td></tr> <tr> <td>+B28</td><td>S28</td></tr> <tr> <td>+B29</td><td>-S29</td></tr> <tr> <td>+B30</td><td>-S30</td></tr> <tr> <td>+B31</td><td>-S31</td></tr> <tr> <td>NC</td><td>GND</td></tr> </table> | <b>NC</b> | GND | NC | GND | +B0 | -S0 | +B1 | S1 | +B2 | S2 | +B3 | -S3 | +B4 | -S4 | +B5 | S5 | +B6 | -S6 | +B7 | S7 | +B8 | -S8 | +B9 | -S9 | +B10 | S10 | +B11 | -S11 | +B12 | -S12 | +B13 | -S13 | +B14 | -S14 | +B15 | S15 | +B16 | -S16 | +B17 | -S17 | +B18 | -S18 | +B19 | -S19 | +B20 | -S20 | +B21 | -S21 | +B22 | -S22 | +B23 | S23 | +B24 | -S24 | +B25 | -S25 | +B26 | -S26 | +B27 | -S27 | +B28 | S28 | +B29 | -S29 | +B30 | -S30 | +B31 | -S31 | NC | GND |

| <b>NC</b> | GND  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |     |    |     |     |     |     |    |     |    |     |     |     |     |     |    |     |     |     |    |     |     |     |     |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |    |     |

| NC        | GND  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |     |    |     |     |     |     |    |     |    |     |     |     |     |     |    |     |     |     |    |     |     |     |     |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |    |     |

| +B0       | -S0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |     |    |     |     |     |     |    |     |    |     |     |     |     |     |    |     |     |     |    |     |     |     |     |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |    |     |

| +B1       | S1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |     |    |     |     |     |     |    |     |    |     |     |     |     |     |    |     |     |     |    |     |     |     |     |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |    |     |

| +B2       | S2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |     |    |     |     |     |     |    |     |    |     |     |     |     |     |    |     |     |     |    |     |     |     |     |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |    |     |

| +B3       | -S3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |     |    |     |     |     |     |    |     |    |     |     |     |     |     |    |     |     |     |    |     |     |     |     |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |      |      |      |     |      |      |      |      |      |      |    |     |