Rev. 7 - July 16th, 2024

# R5560/R5560SE

128 Channel 14 bit 125 MS/s Open FPGA Digitizer

# Register your device

Register your device to your **MyCAEN+** account and get access to our customer services, such as notification for new firmware or software upgrade, tracking service procedures or open a ticket for assistance. **MyCAEN+** accounts have a dedicated support service for their registered products. A set of basic information can be shared with the operator, speeding up the troubleshooting process and improving the efficiency of the support interactions.

**MyCAEN+** dashboard is designed to offer you a direct access to all our after sales services. Registration is totally free, to create an account go to <https://www.caen.it/become-mycaenplus-user> and fill the registration form with your data.

**1**

create a MyCAEN+ account

**2**

register your devices

**3**

get support and more!

<https://www.caen.it/become-mycaenplus-user/>

# Purpose of this User Manual

This User Manual contains the full description of the R5560SE 128-Channel 14-bit @125 MS/s Open FPGA Digitizer, of its web interface and a brief guide to the Open Hardware Readout Software.

## Change Document Record

| Date                             | Revision | Changes                                                                                         |

|----------------------------------|----------|-------------------------------------------------------------------------------------------------|

| June 5 <sup>th</sup> , 2020      | 00       | Initial release                                                                                 |

| December 17 <sup>th</sup> , 2020 | 01       | Revision of a deleted section                                                                   |

| March 19 <sup>th</sup> , 2021    | 02       | Revised <b>Functional Description</b>                                                           |

| May 27 <sup>th</sup> , 2021      | 03       | Minor revision of Technical Specifications                                                      |

| October 15 <sup>th</sup> , 2021  | 04       | Revised <b>Safety Notices</b><br>Minor revision of Technical Specifications                     |

| February 2 <sup>nd</sup> , 2022  | 05       | General revision.<br>Added new update procedure<br>Added Chap. <b>Touchscreen Display Guide</b> |

| June 20 <sup>th</sup> , 2023     | 06       | Unification of R5560 and R5560SE User Manuals and complete revision of contents                 |

| July 16 <sup>th</sup> , 2024     | 07       | Rectified pinout of R5560 analog input connector                                                |

## Symbols, abbreviated terms and notation

|      |                                         |

|------|-----------------------------------------|

| ADC  | Analog to Digital Converter             |

| ASIC | Application Specific Integrated Circuit |

| DAQ  | Data Acquisition                        |

| FIFO | First In First Out                      |

| FPGA | Field Programmable Gate Array           |

| FTP  | File Transfer Protocol                  |

| OS   | Operating system                        |

| SDK  | Software Development Kit                |

## Reference Document

[RD1] GD6520 - SCI-Compiler Quick Start Guide

[RD2] UM6519 - SCI-Compiler User Manual

## Manufacturer contact

**CAEN S.p.A.**

Via Vетraia, 11 55049 Viareggio (LU) - ITALY

Tel. +39.0584.388.398 Fax +39.0584.388.959

[www.caen.it](http://www.caen.it) | [info@caen.it](mailto:info@caen.it)

© CAEN SpA – 2023

## Limitation of Responsibility

If the warnings contained in this manual are not followed, CAEN will not be responsible for damage caused by improper use of the device. The manufacturer declines all responsibility for damage resulting from failure to comply with the instructions for use of the product. The equipment must be used as described in the user manual, with particular regard to the intended use, using only accessories as specified by the manufacturer. No modification or repair can be performed.

## Disclaimer

No part of this manual may be reproduced in any form or by any means, electronic, mechanical, recording, or otherwise, without the prior written permission of CAEN spa.

The information contained herein has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. CAEN spa reserves the right to modify its products specifications without giving any notice; for up to date information please visit [www.caen.it](http://www.caen.it).

## Made in Italy

We remark that all our boards have been designed and assembled in Italy. In a challenging environment where a competitive edge is often obtained at the cost of lower wages and declining working conditions, we proudly acknowledge that all those who participated in the production and distribution process of our devices were reasonably paid and worked in a safe environment (this is true for the boards marked "MADE IN ITALY", while we cannot guarantee for third-party manufactures).

## Table of contents

|                                                      |           |

|------------------------------------------------------|-----------|

| <b>Purpose of this User Manual .....</b>             | <b>3</b>  |

| <b>Change Document Record .....</b>                  | <b>3</b>  |

| <b>Symbols, abbreviated terms and notation .....</b> | <b>3</b>  |

| <b>Reference Document .....</b>                      | <b>3</b>  |

| <b>Manufacturer contact .....</b>                    | <b>3</b>  |

| <b>Limitation of Responsibility .....</b>            | <b>3</b>  |

| <b>Disclaimer .....</b>                              | <b>3</b>  |

| <b>Made in Italy .....</b>                           | <b>4</b>  |

| <b>Table of contents.....</b>                        | <b>5</b>  |

| <b>List of Figures.....</b>                          | <b>6</b>  |

| <b>List of Tables .....</b>                          | <b>7</b>  |

| <b>1   Introduction .....</b>                        | <b>9</b>  |

| <b>2   Safety Notices .....</b>                      | <b>10</b> |

| <b>3   Block Diagram.....</b>                        | <b>12</b> |

| <b>4   Technical Specifications.....</b>             | <b>13</b> |

| <b>5   Packaging and compliancy.....</b>             | <b>15</b> |

| SCI-Compiler License .....                           | 16        |

| <b>6   PID (Product Identifier) .....</b>            | <b>18</b> |

| <b>7   Power Requirements .....</b>                  | <b>19</b> |

| <b>8   Cooling Management.....</b>                   | <b>20</b> |

| Cleaning the air vents.....                          | 20        |

| <b>9   Installing the device .....</b>               | <b>21</b> |

| <b>10   Panels Description .....</b>                 | <b>22</b> |

| R5560 dimensions .....                               | 22        |

| R5560SE dimensions.....                              | 23        |

| Front Panel .....                                    | 24        |

| Rear Panel.....                                      | 26        |

| <b>11   Functional Description .....</b>             | <b>27</b> |

| System Architecture.....                             | 27        |

| DAQ section .....                                    | 28        |

| R5560 Differential Inputs .....                      | 29        |

| Analog Frontend - R5560SE .....                      | 30        |

| Digital Stage.....                                   | 31        |

| Data readout .....                                   | 32        |

| Clock Distribution .....                             | 34        |

| Synchronization among multiple boards .....          | 35        |

| DAQ Datapath.....                                    | 36        |

| <b>12   Touchscreen Display Guide .....</b>          | <b>38</b> |

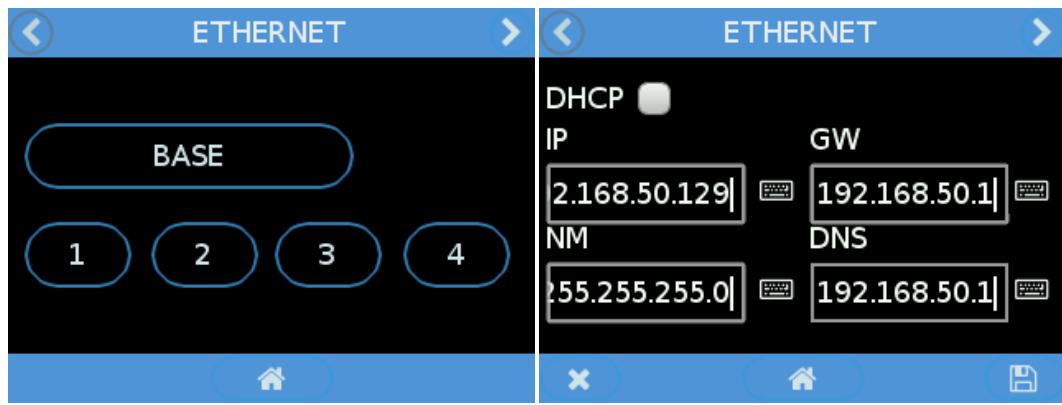

| Ethernet settings .....                              | 38        |

| Signal routing settings .....                        | 39        |

| Info and status .....                                | 41        |

| <b>13   Web Interface.....</b>                       | <b>42</b> |

| Baseboard Web Interface.....                         | 42        |

| Connection .....                                     | 42        |

| Device Status and firmware upgrade .....             | 42        |

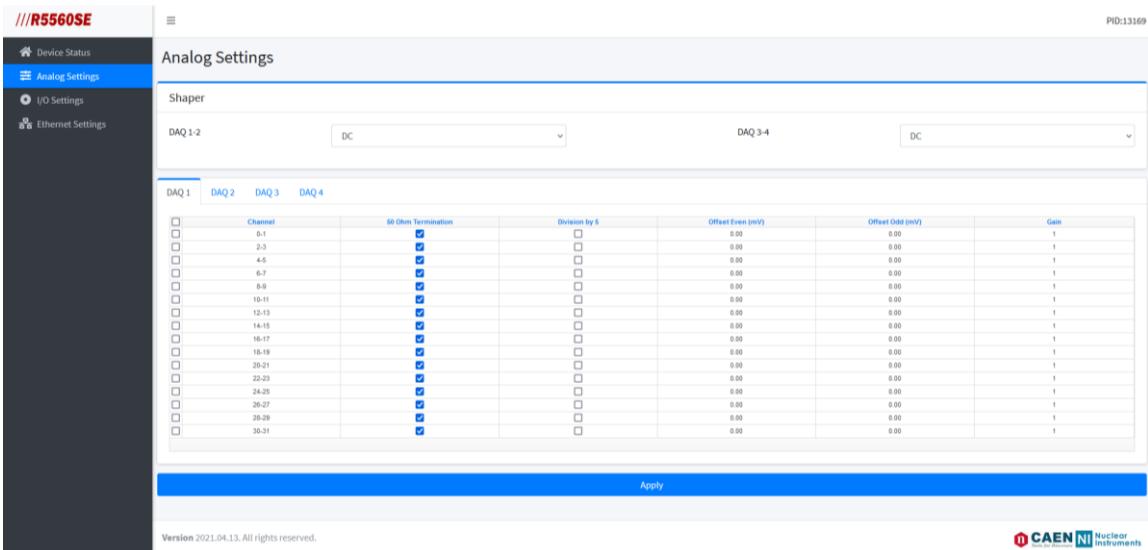

| Analog settings .....                                | 43        |

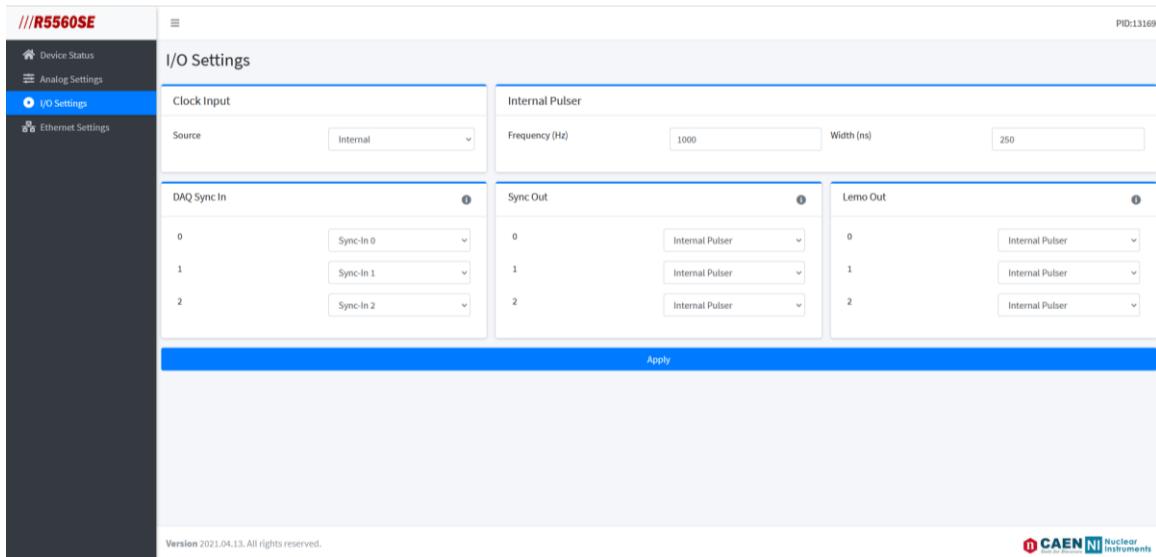

| I/O settings .....                                   | 44        |

|                                               |           |

|-----------------------------------------------|-----------|

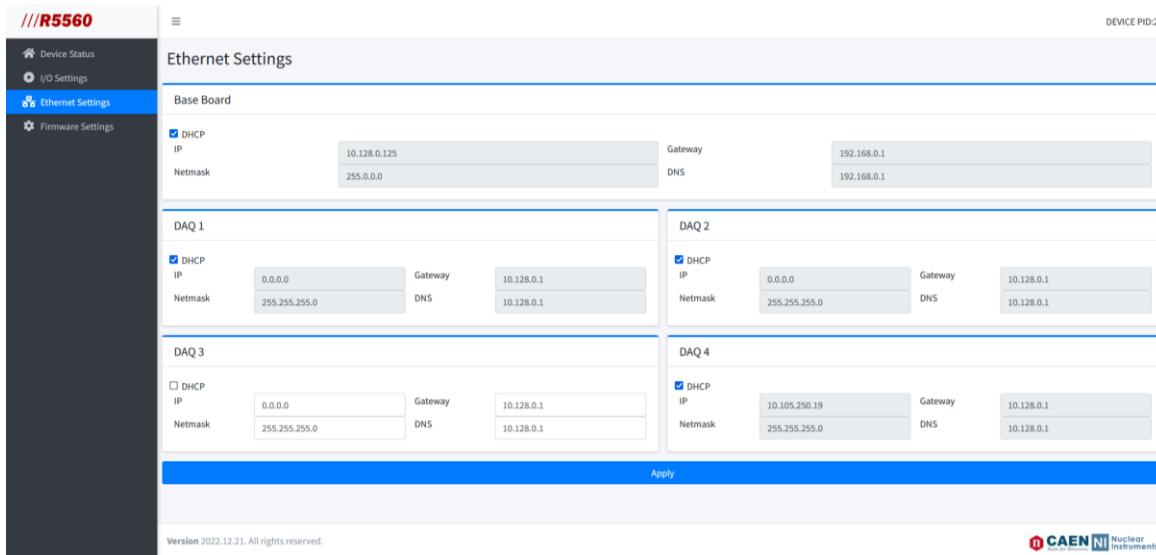

| Ethernet settings.....                        | 45        |

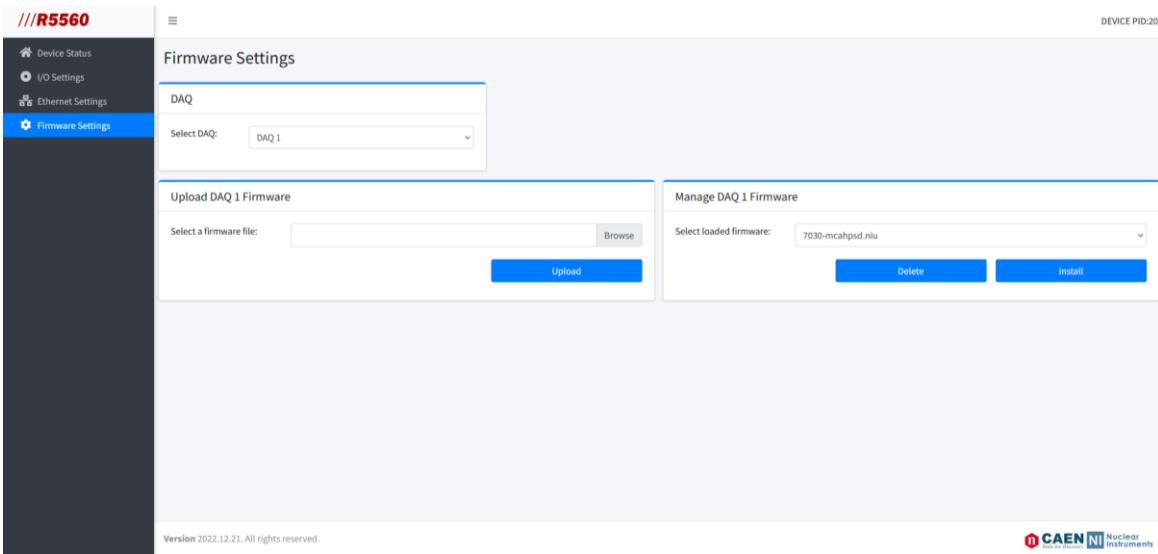

| Firmware Settings .....                       | 45        |

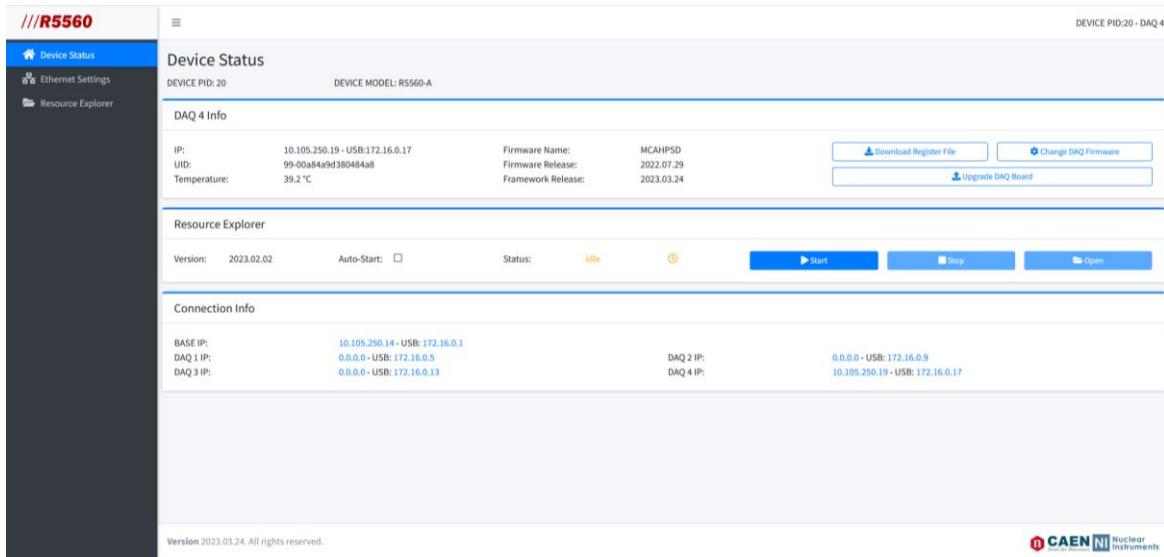

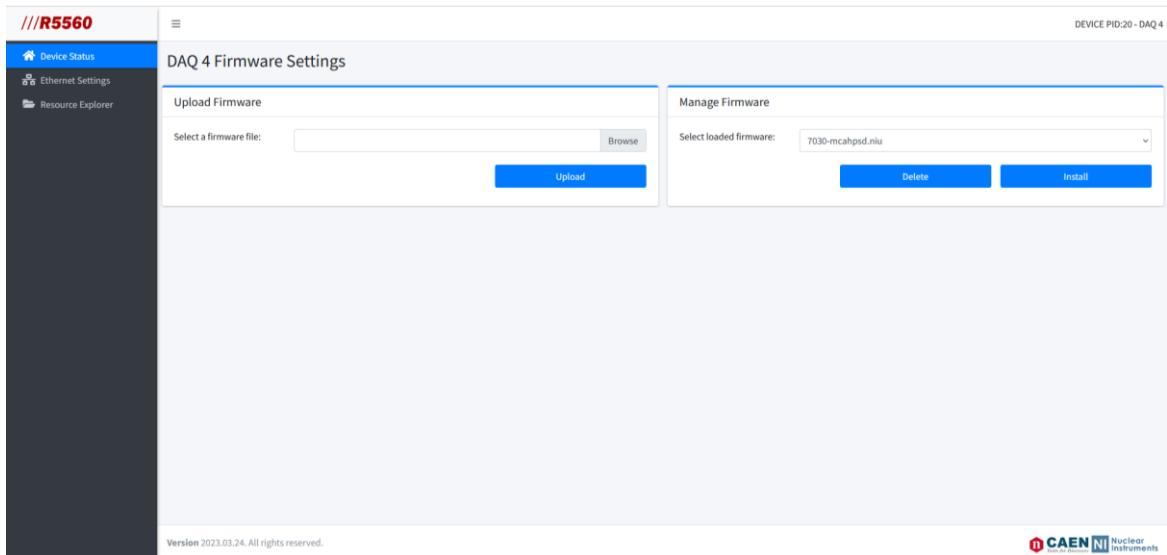

| <b>DAQ section Web Interface .....</b>        | <b>46</b> |

| Connection .....                              | 46        |

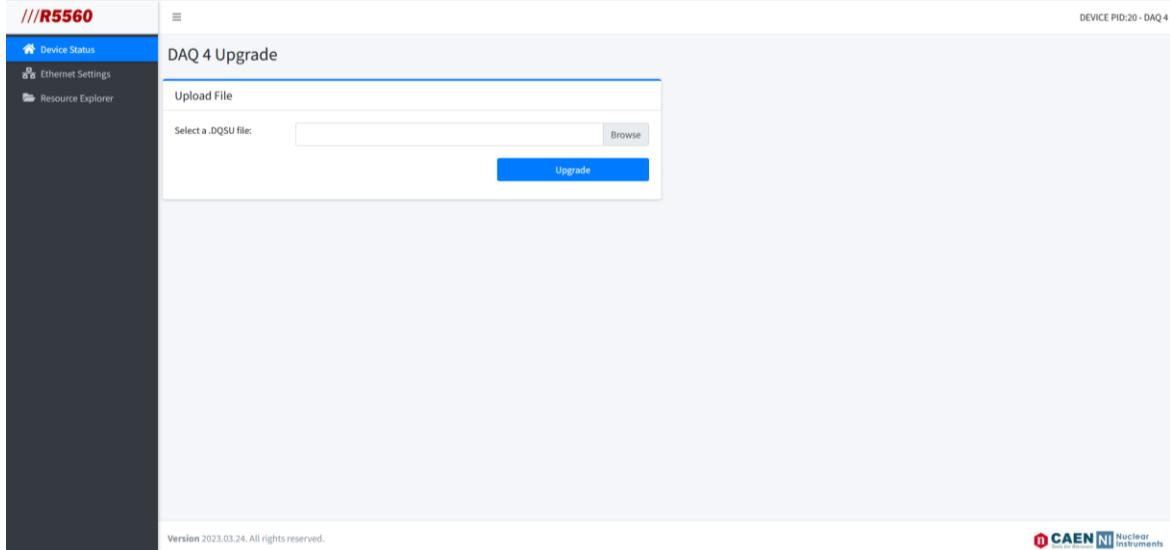

| Device Status and firmware upgrade .....      | 46        |

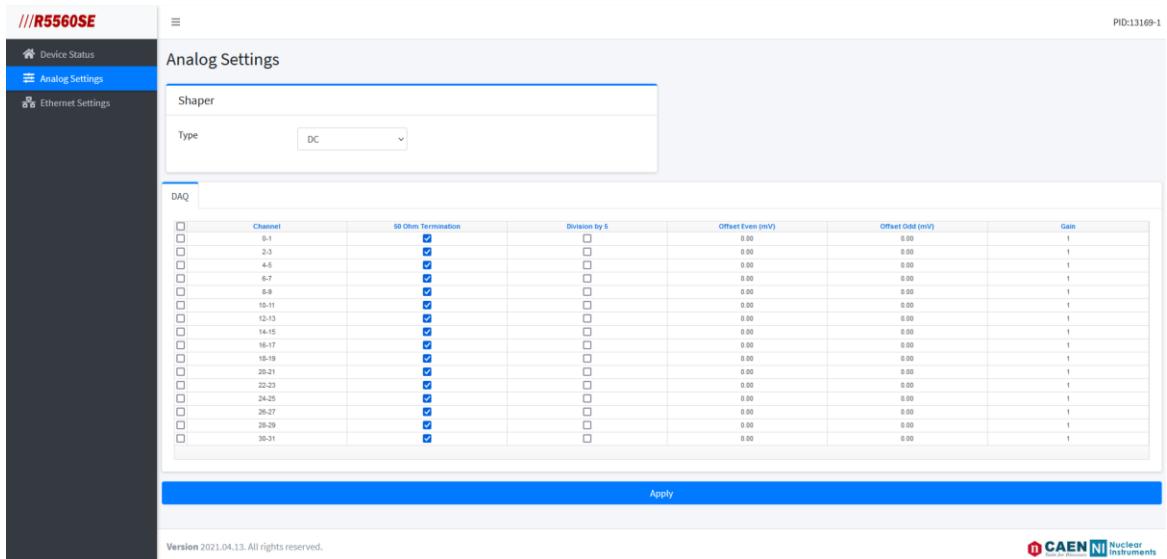

| Analog settings .....                         | 48        |

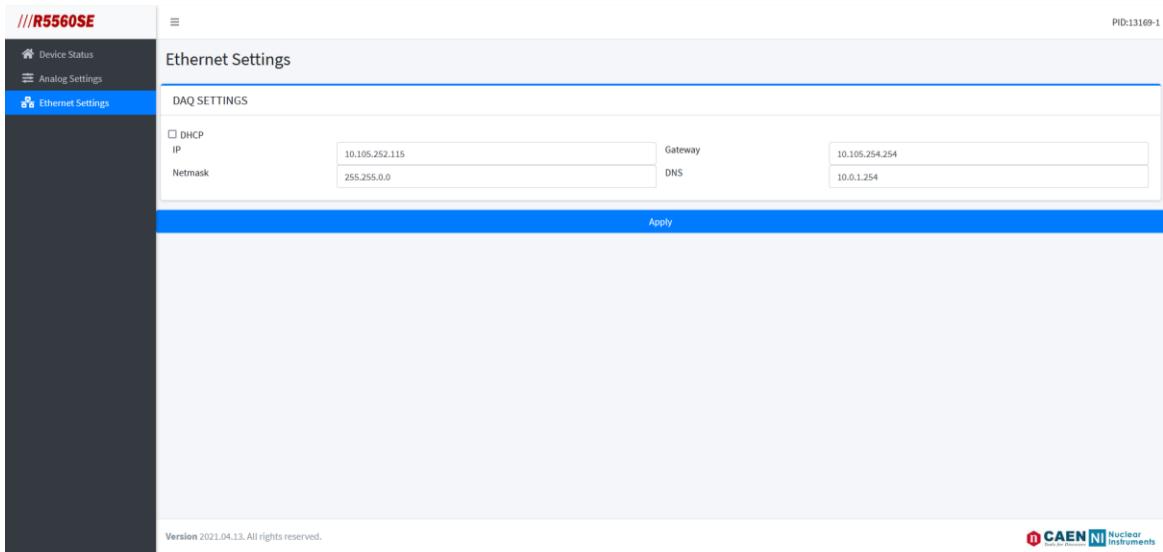

| Ethernet settings.....                        | 48        |

| Resource Explorer (beta).....                 | 49        |

| <b>14 Firmware Developing .....</b>           | <b>50</b> |

| Firmware design: the processing core .....    | 50        |

| Default firmware .....                        | 51        |

| <b>15 Drivers &amp; Libraries.....</b>        | <b>53</b> |

| Drivers installation .....                    | 53        |

| R5560 SDK for default firmware.....           | 53        |

| <b>16 Open Hardware Readout Software.....</b> | <b>57</b> |

| Software installation.....                    | 57        |

| Board connection .....                        | 59        |

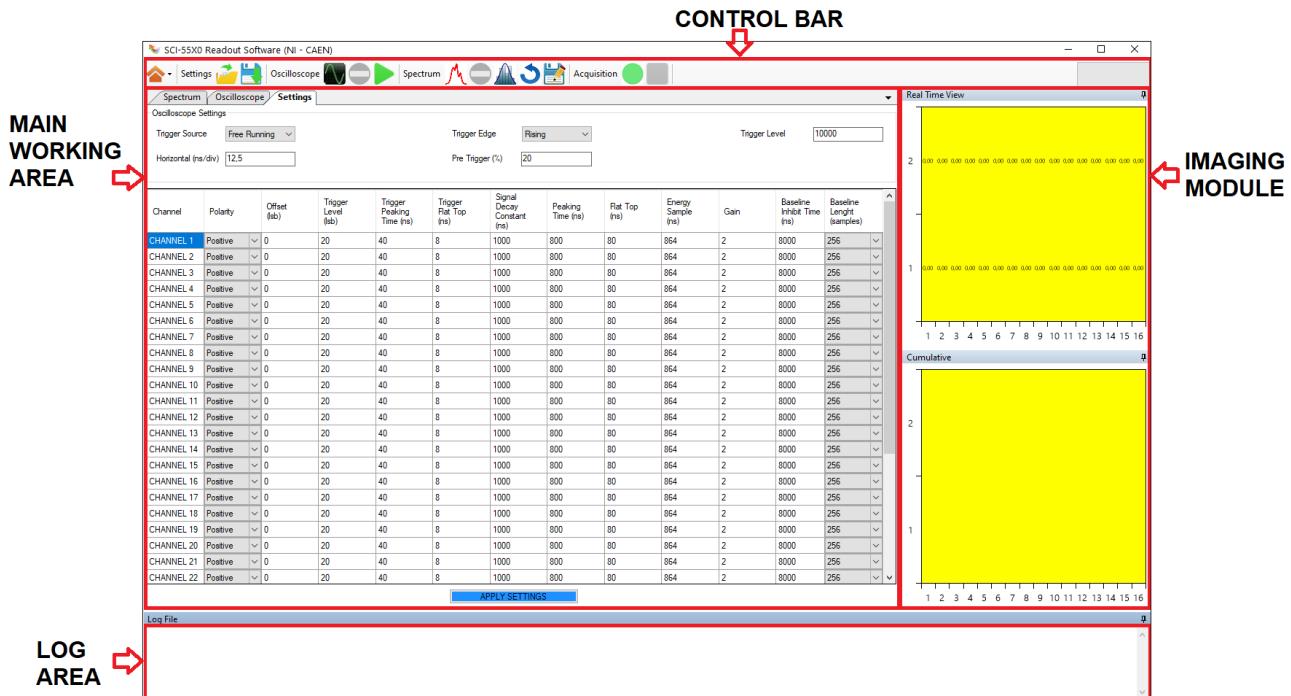

| Software GUI Description .....                | 60        |

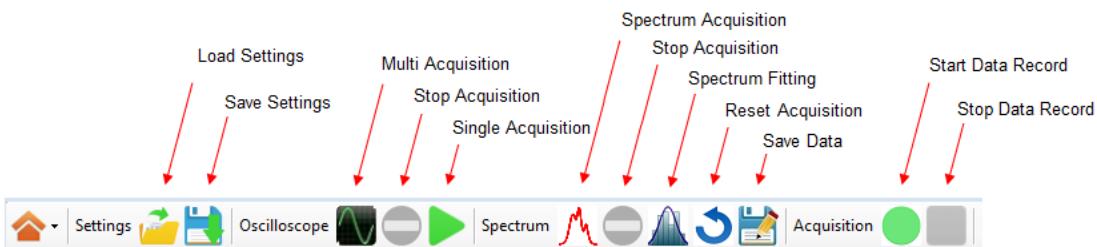

| Control Bar.....                              | 61        |

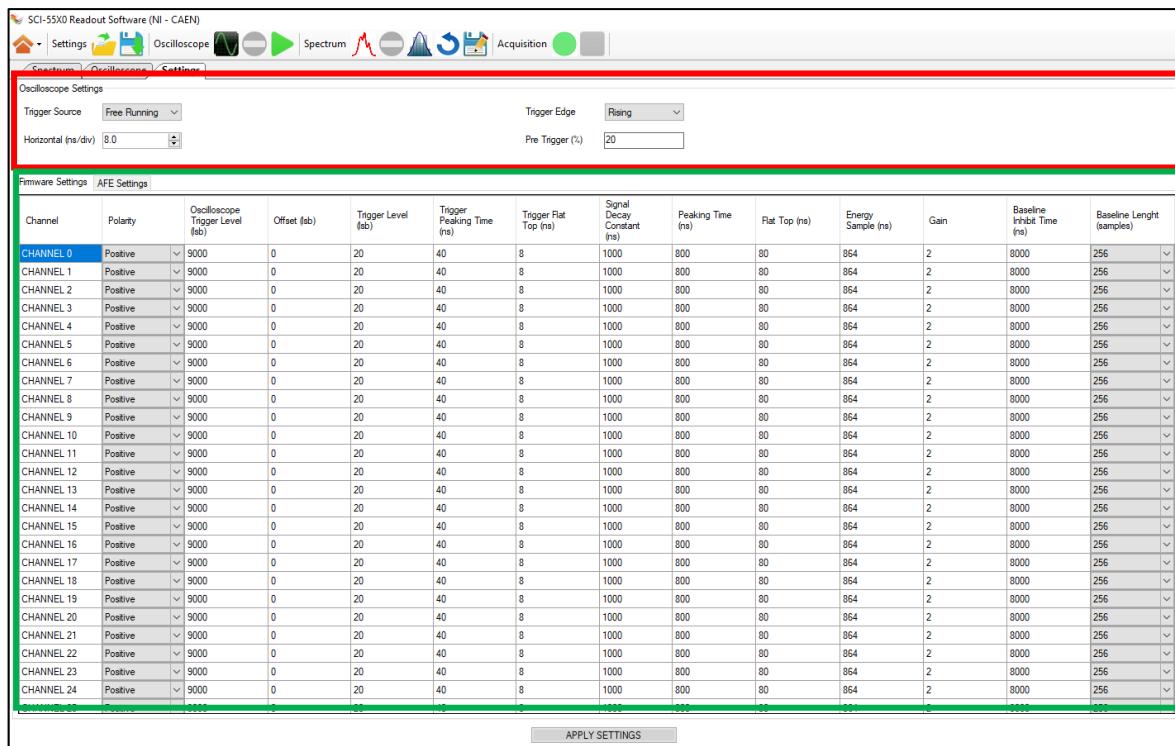

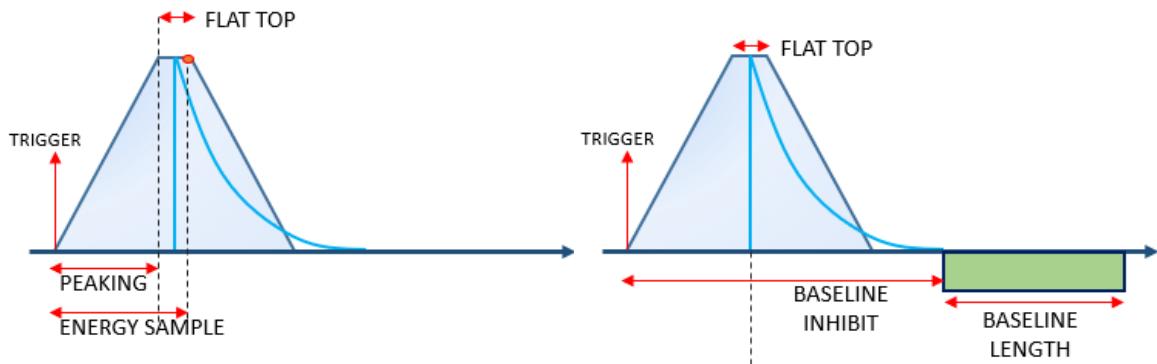

| Settings Tab.....                             | 62        |

| Oscilloscope Tab.....                         | 65        |

| Spectrum Tab .....                            | 66        |

| Imaging Module .....                          | 68        |

| How to Perform a Fit .....                    | 68        |

| How to Save Data .....                        | 69        |

| <b>17 Appendix .....</b>                      | <b>71</b> |

| <b>Ethernet Protocol</b> .....                | 71        |

| TCP WEB SERVER .....                          | 71        |

| FIFO SERVER .....                             | 72        |

| JSON SERVER .....                             | 72        |

| <b>Optical Link Protocol</b> .....            | 72        |

| <b>Libraries usage examples</b> .....         | 74        |

| <b>18 Instructions for Cleaning .....</b>     | <b>77</b> |

| Cleaning the Touchscreen .....                | 77        |

| Cleaning the air vents .....                  | 77        |

| General cleaning safety precautions .....     | 77        |

| <b>19 Disposal.....</b>                       | <b>78</b> |

| <b>20 Technical Support.....</b>              | <b>79</b> |

## List of Figures

|                                                                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.1: block diagram of the R5560/R5560SE. AFE sections are implemented in the R5560SE version only.....                                             | 12 |

| Figure 5.1: SCI-Compiler USB Dongle and keys for license activation.....                                                                                  | 16 |

| Figure 9.1: installing the device into a 19" rack .....                                                                                                   | 21 |

| Figure 10.1: R5560 front panel view and dimensions. .....                                                                                                 | 22 |

| Figure 10.2: R5560 rear panel view and dimensions.....                                                                                                    | 22 |

| Figure 10.3: R5560 side view and dimensions. .....                                                                                                        | 22 |

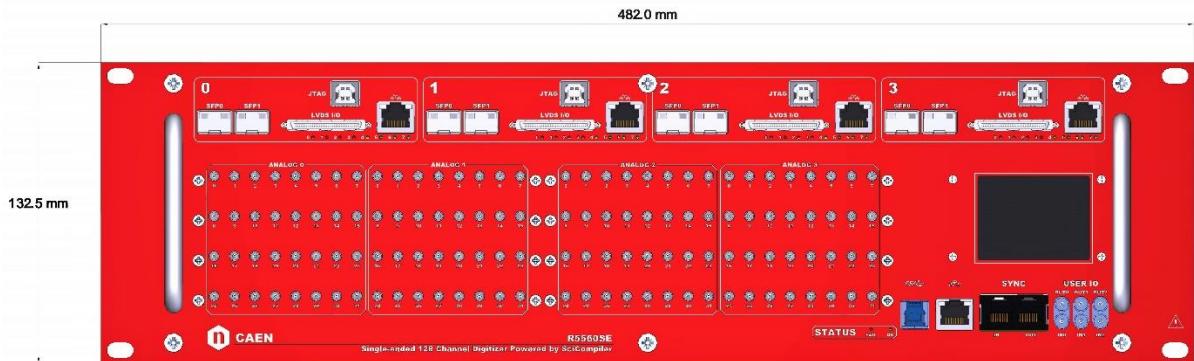

| Figure 10.4: R5560SE Front panel view and dimensions. .....                                                                                               | 23 |

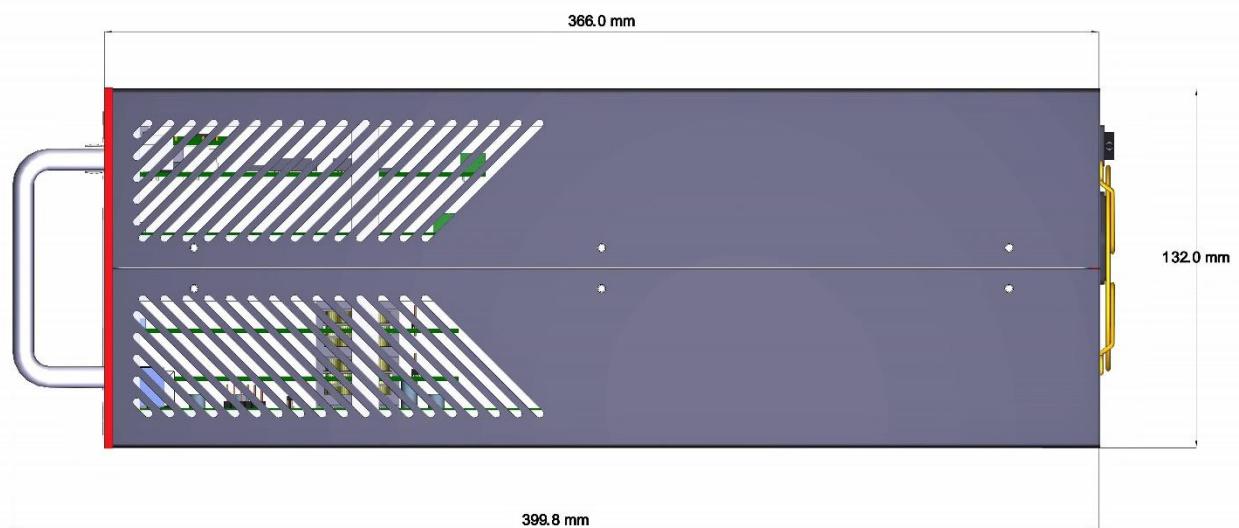

| Figure 10.5: R5560SE Rear panel view and dimensions.....                                                                                                  | 23 |

| Figure 10.6: R5560SE side view and dimensions. .....                                                                                                      | 23 |

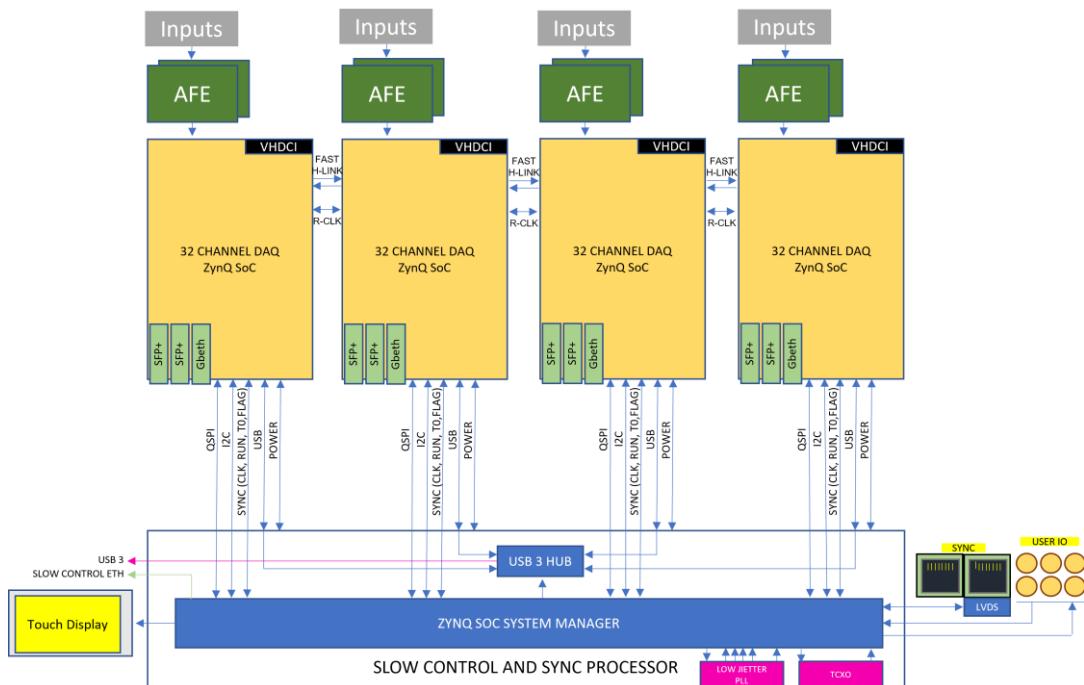

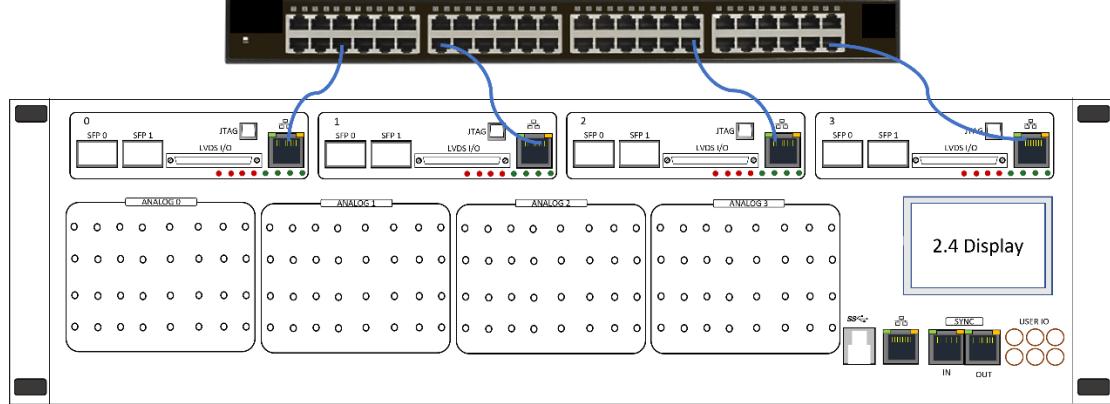

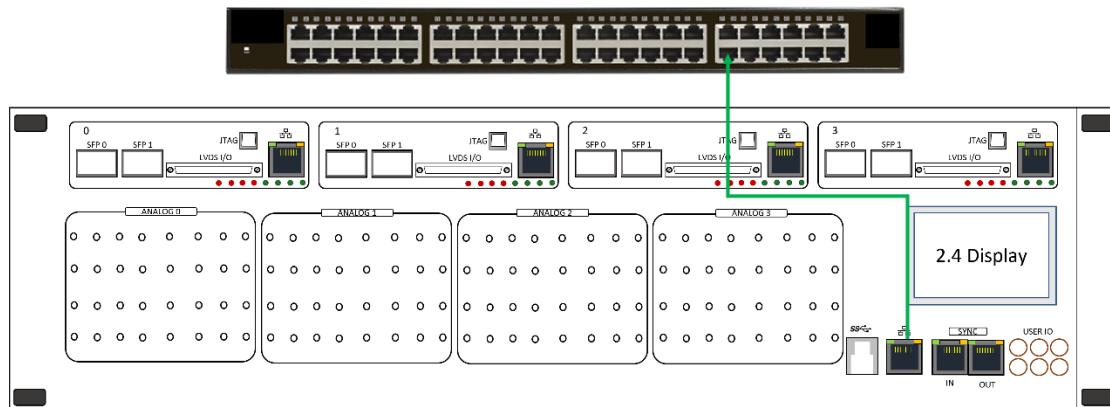

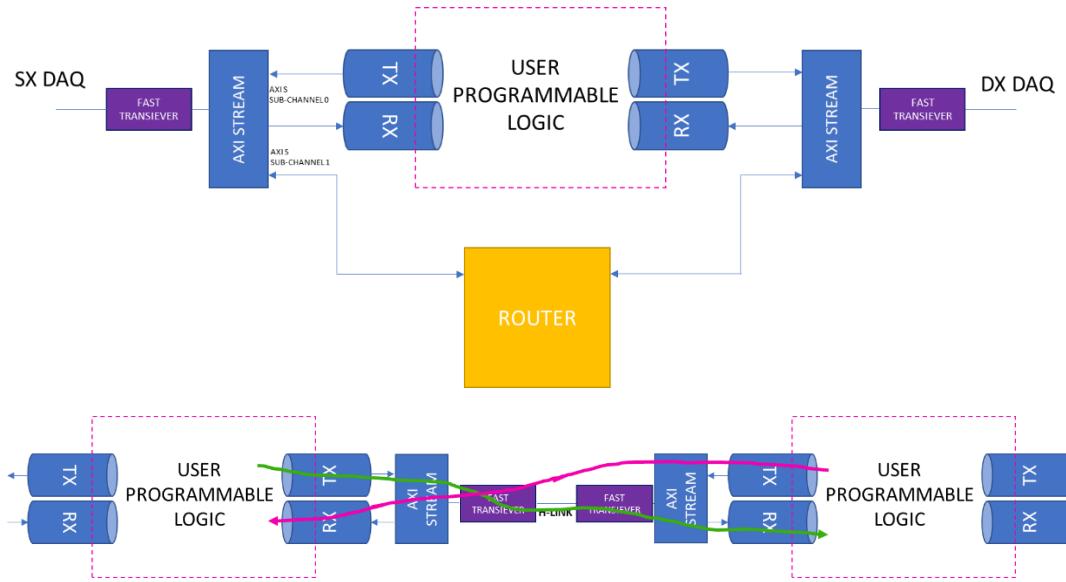

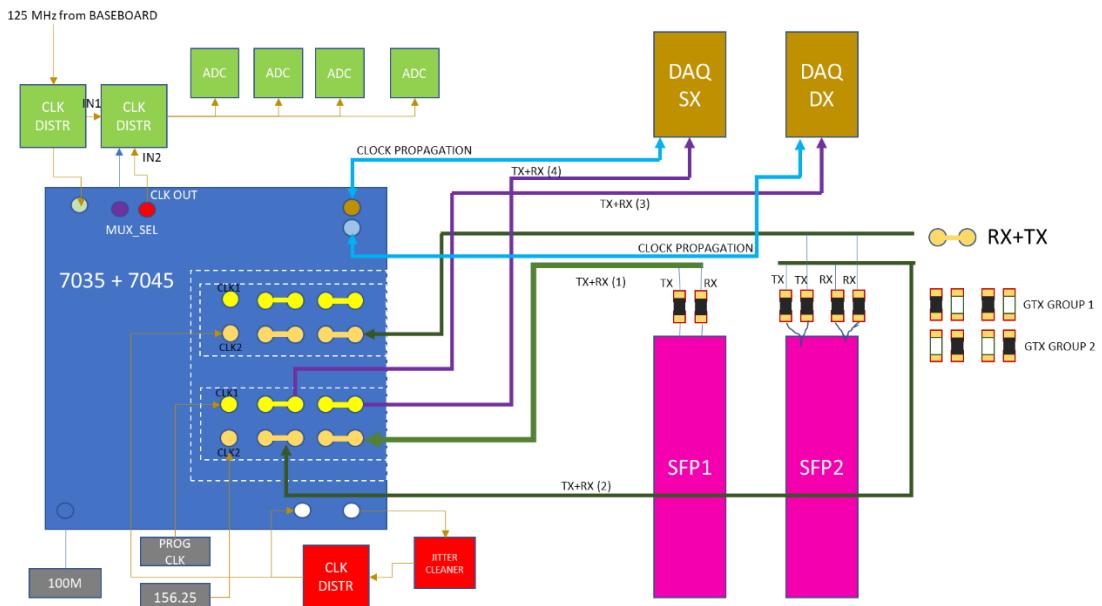

| Figure 11.1: the complete block diagram of R5560SE. The R5560 works the same without the AFE boards.....                                                  | 27 |

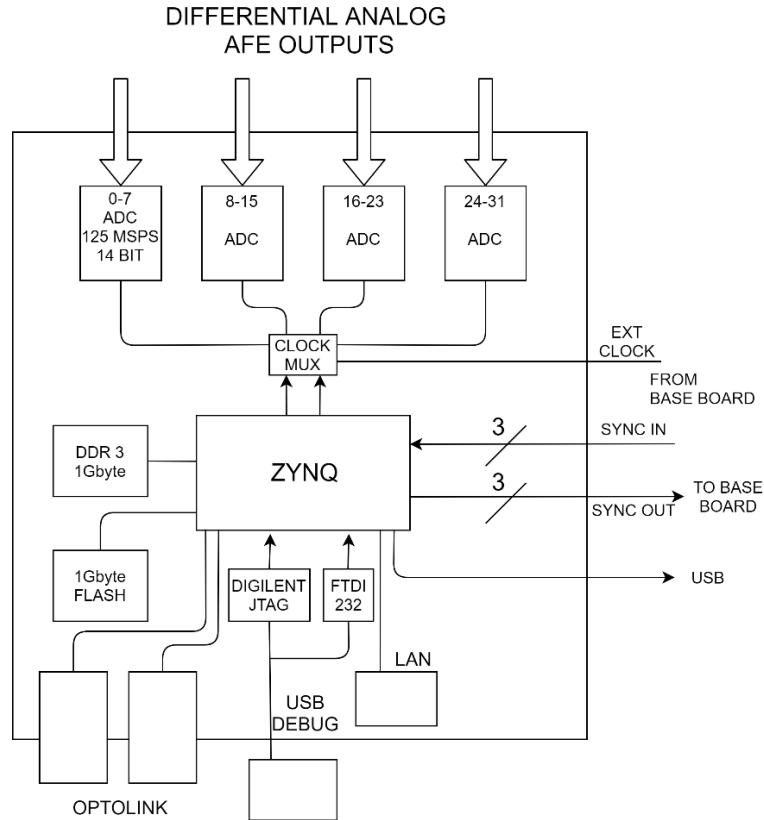

| Figure 11.2: block diagram of a single DAQ section of the R5560/R5560SE. Signals interconnecting the DAQ with the baseboard and AFE boards are shown..... | 29 |

|                                                                                                                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

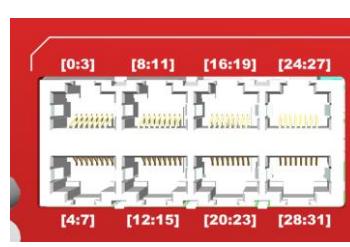

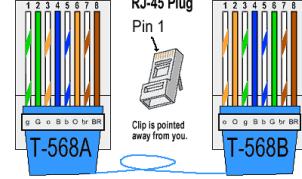

| Figure 11.3: RJ45 analog connector pinout: The pinout for the first group of channels [1:4] is shown. The same ordering can be applied to the subsequent groups. ....                                                       | 29 |

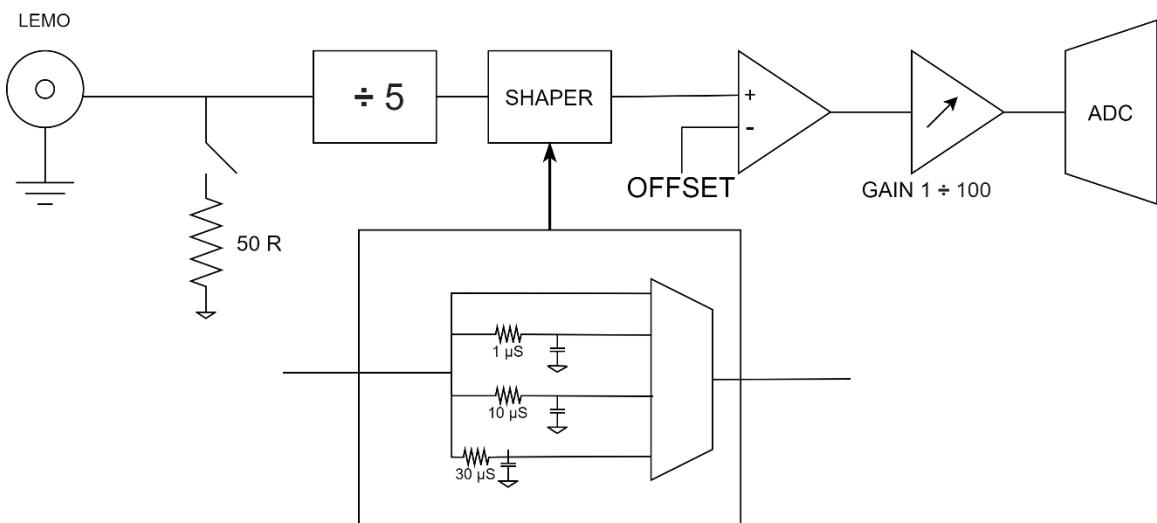

| Figure 11.4: block diagram of the AFE section of the R5560SE. ....                                                                                                                                                          | 30 |

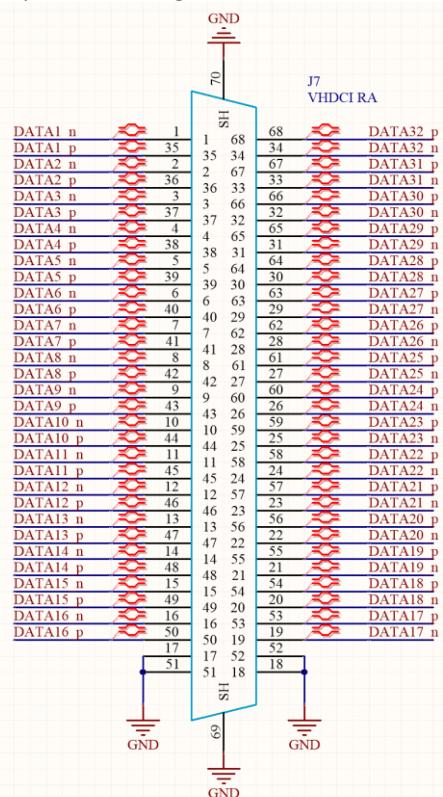

| Figure 11.5: pinout of the LVDS digital connectors of the R5560SE. ....                                                                                                                                                     | 31 |

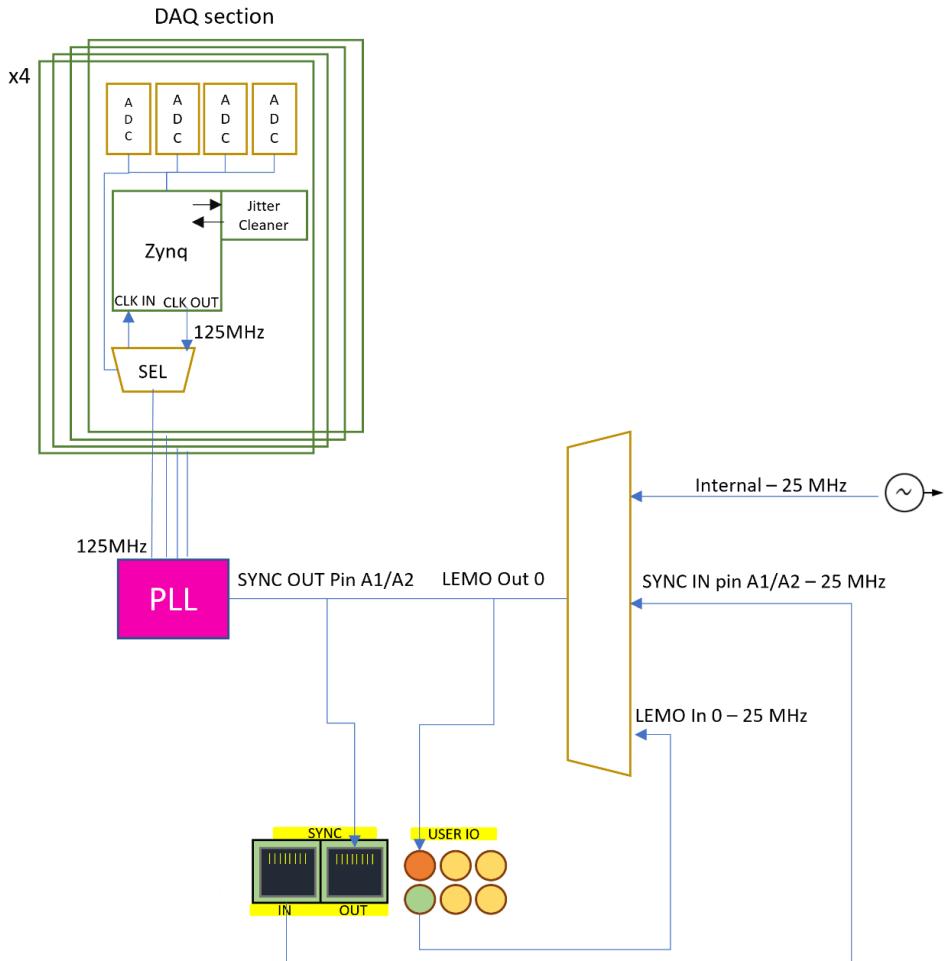

| Figure 11.6: scheme of the clock distribution on the R5560/R5560SE ....                                                                                                                                                     | 35 |

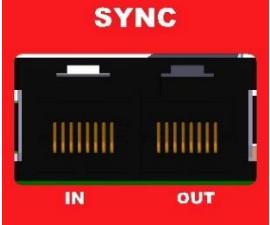

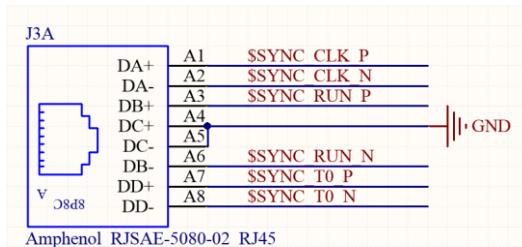

| Figure 11.7: pinout of the SYNC RJ45 connector of the R5560SE ....                                                                                                                                                          | 35 |

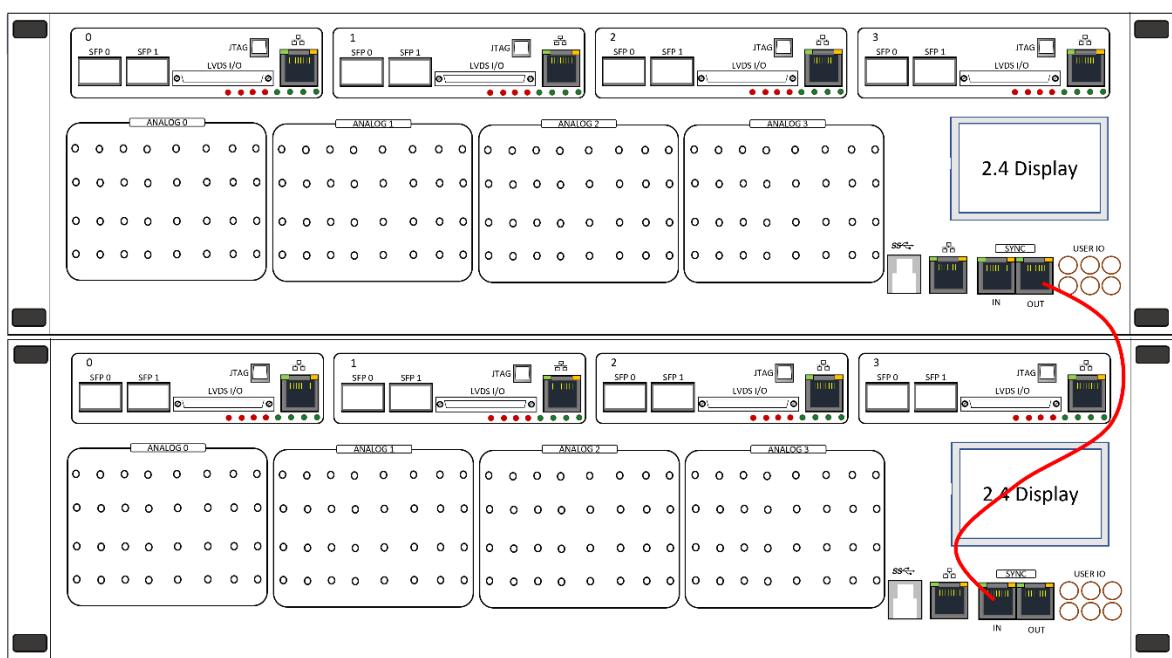

| Figure 11.8: synchronization connection between two R5560SE boards using a single Ethernet cable. Slave board (bottom) is receiving synchronization signals on SYNC IN connector from the master board (top) SYNC OUT. .... | 36 |

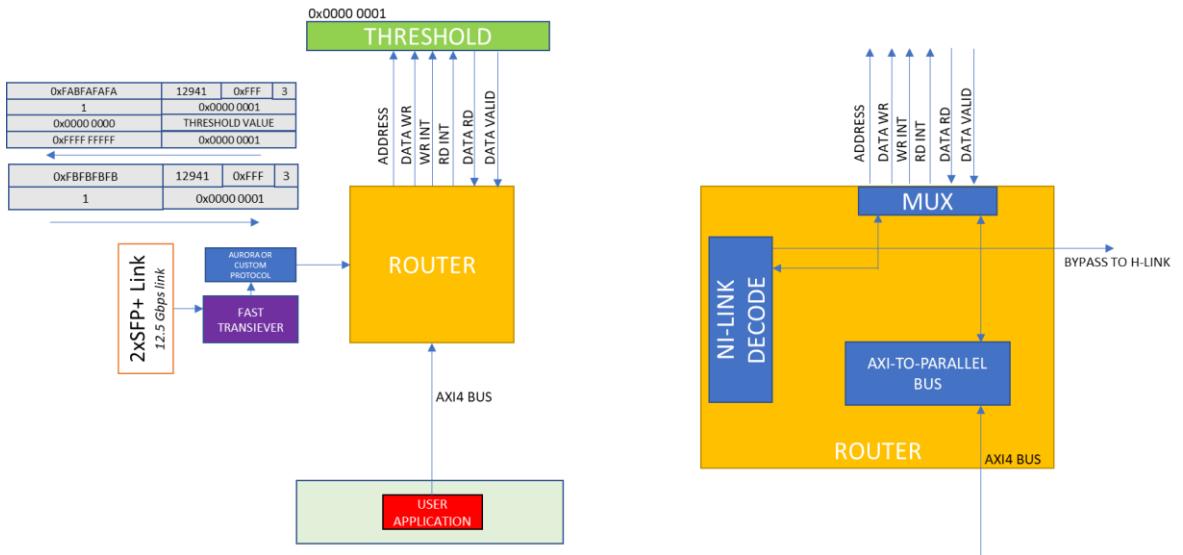

| Figure 11.9: example of the router operation for data transfer. ....                                                                                                                                                        | 37 |

| Figure 11.10: data transferring of two R5560SE sections, using the router or the H-LINK. ....                                                                                                                               | 37 |

| Figure 12.1: the main page of the Touchscreen display. ....                                                                                                                                                                 | 38 |

| Figure 12.2: the Ethernet tabs on the touchscreen display. ....                                                                                                                                                             | 39 |

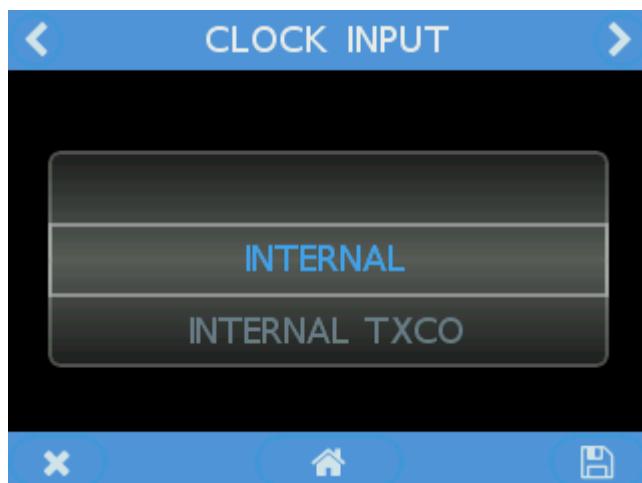

| Figure 12.3: the CLOCK tab. ....                                                                                                                                                                                            | 39 |

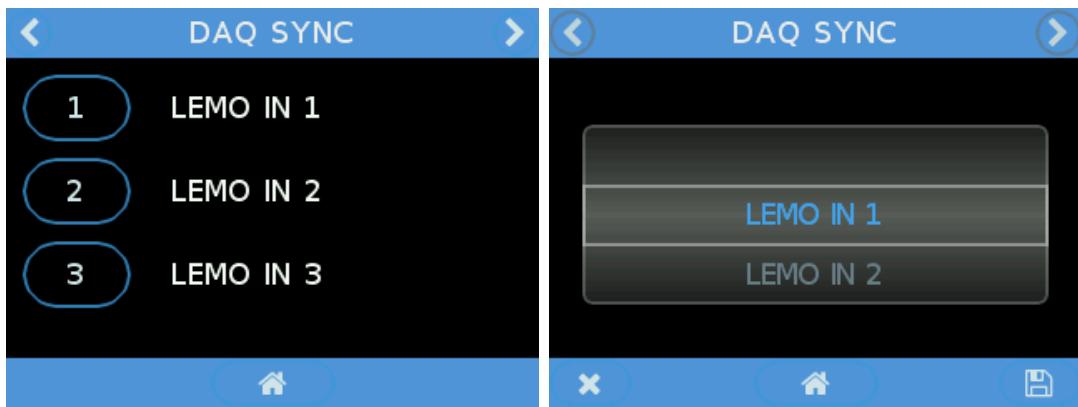

| Figure 12.4: the DAQ SYNC tab. ....                                                                                                                                                                                         | 40 |

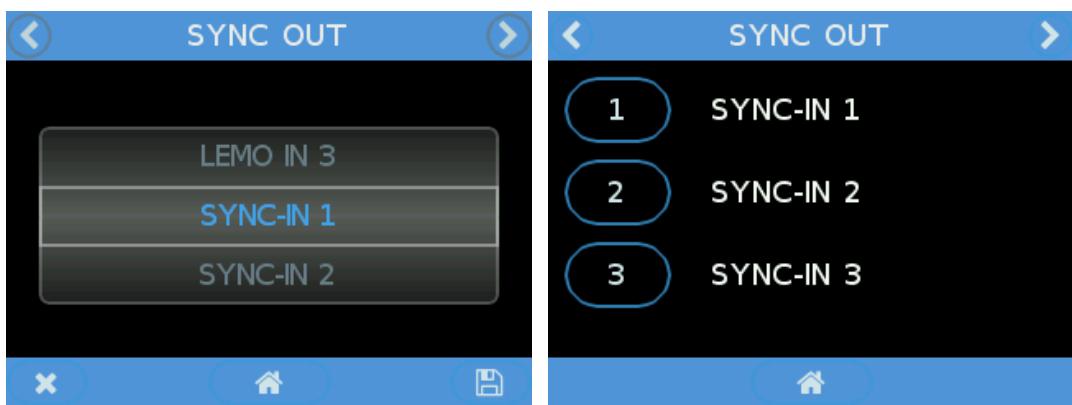

| Figure 12.5: the SYNC OUT tab. ....                                                                                                                                                                                         | 40 |

| Figure 12.6: the LEMO OUT tab. ....                                                                                                                                                                                         | 40 |

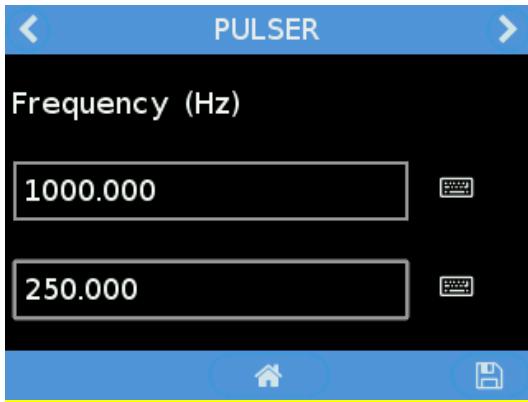

| Figure 12.7: the LEMO OUT tab. ....                                                                                                                                                                                         | 41 |

| Figure 12.8: the TEMPERATURE, DAQ LAN STATUS and DAQ INFO tabs. ....                                                                                                                                                        | 41 |

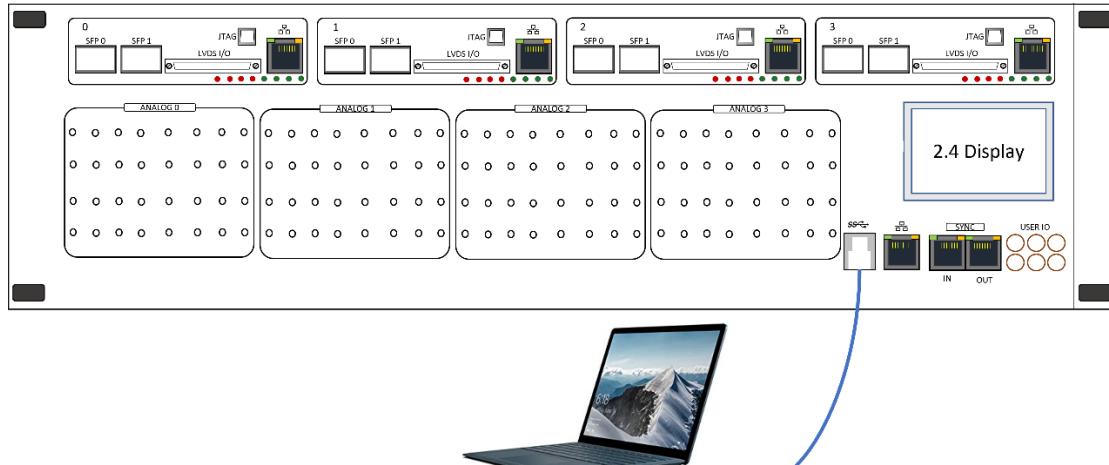

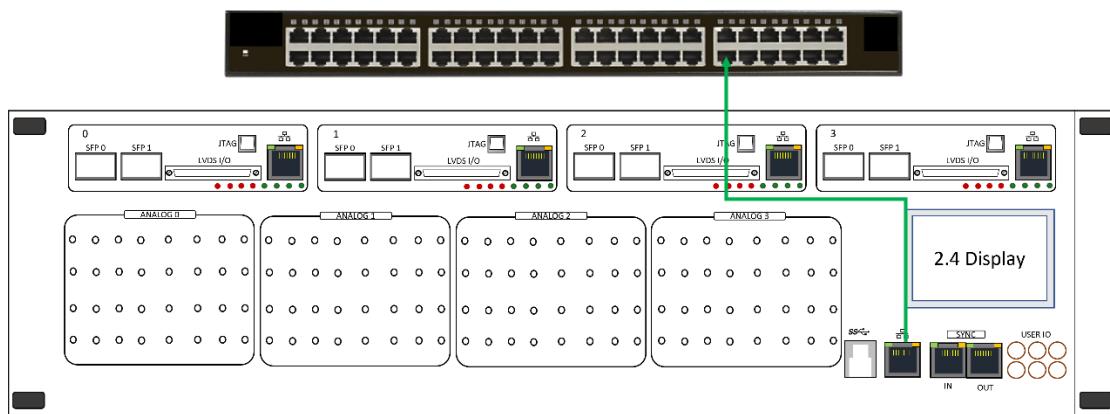

| Figure 13.1: connection scheme to access the baseboard Web interface. The baseboard port can be connected to the network or directly to a PC Ethernet port. ....                                                            | 42 |

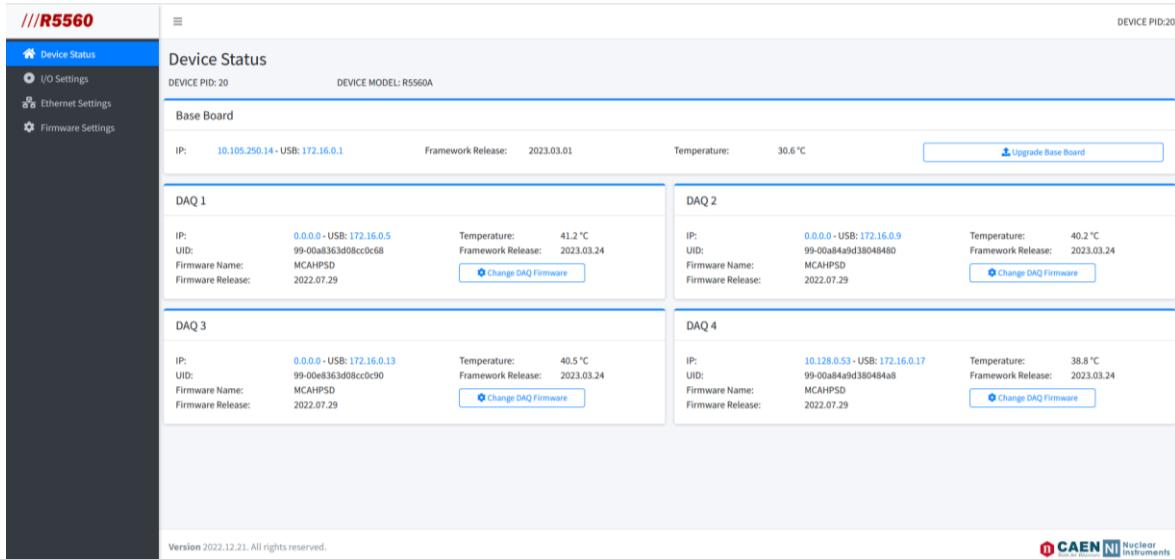

| Figure 13.2: the Home page of the baseboard Web interface. ....                                                                                                                                                             | 43 |

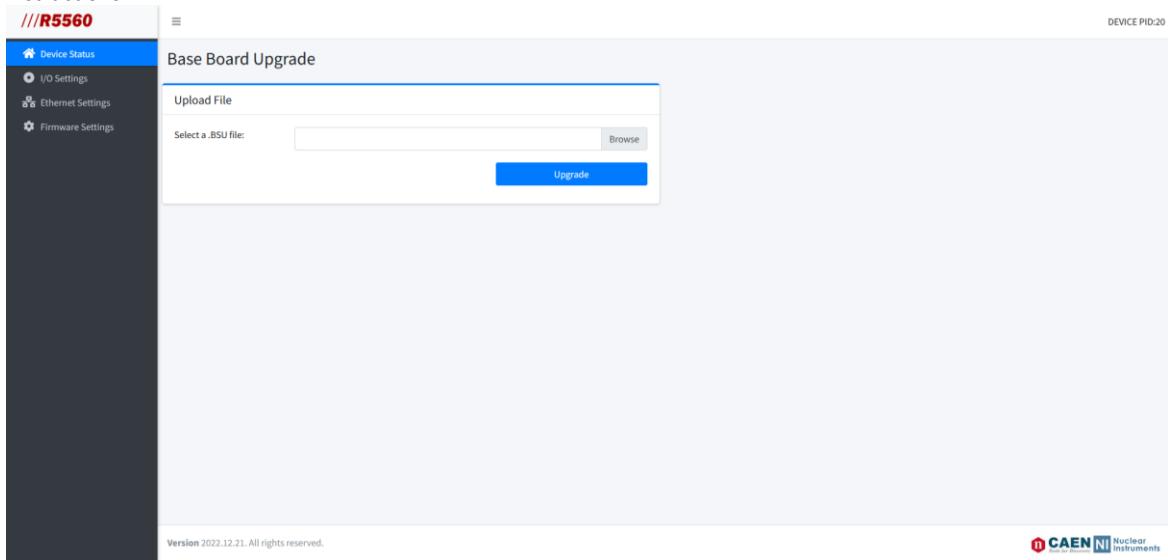

| Figure 13.3: upgrade of the OS of the board from the baseboard Web interface. ....                                                                                                                                          | 43 |

| Figure 13.4: the Analog Settings page of the baseboard Web Interface. ....                                                                                                                                                  | 44 |

| Figure 13.5: the I/O Settings page of the baseboard Web interface. ....                                                                                                                                                     | 45 |

| Figure 13.6: the Ethernet Settings page of the baseboard Web interface. ....                                                                                                                                                | 45 |

| Figure 13.7: the Ethernet Settings page of the baseboard Web interface. ....                                                                                                                                                | 46 |

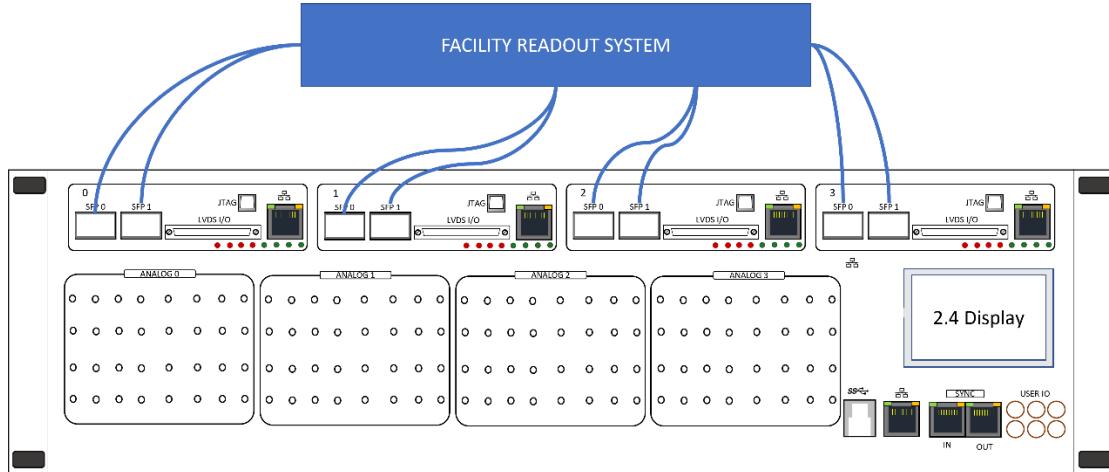

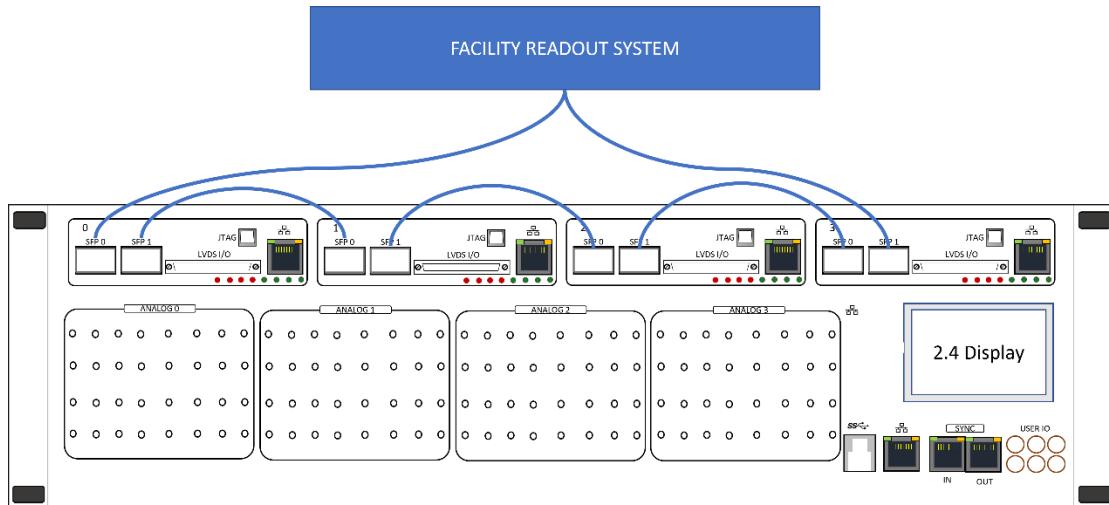

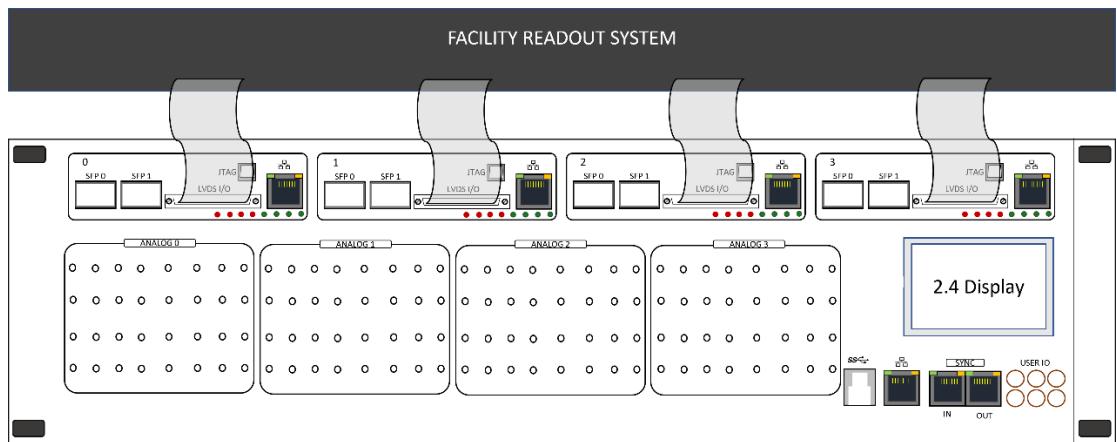

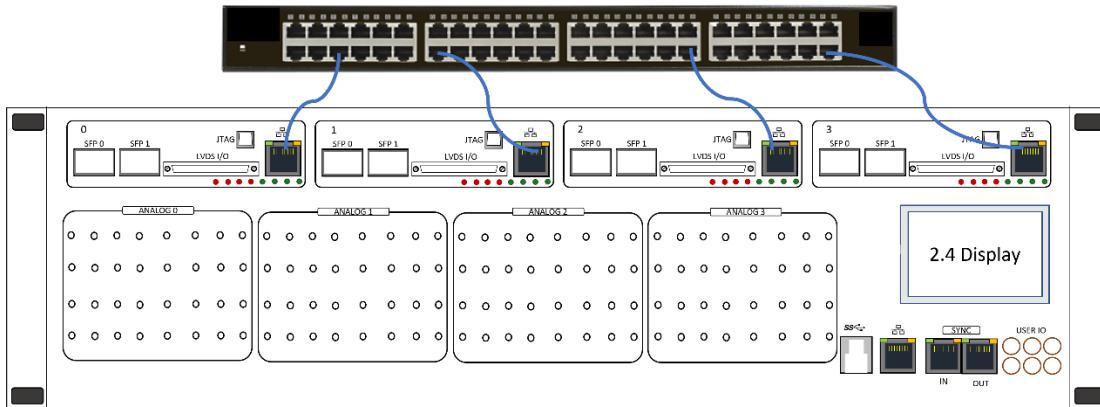

| Figure 13.8: connection scheme to access the DAQ section Web interface. Each port can be connected independently to the network or directly to a PC Ethernet port. ....                                                     | 46 |

| Figure 13.9: the Home page of the DAQ section Web interface. ....                                                                                                                                                           | 47 |

| Figure 13.10: upgrade of the OS of the board from the DAQ Web interface. ....                                                                                                                                               | 47 |

| Figure 13.11: upgrade of the firmware from the DAQ section Web Interface. ....                                                                                                                                              | 48 |

| Figure 13.12: the Analog Settings page of the DAQ section Web Interface. ....                                                                                                                                               | 48 |

| Figure 13.13: the Ethernet Settings page of the DAQ section Web interface. ....                                                                                                                                             | 49 |

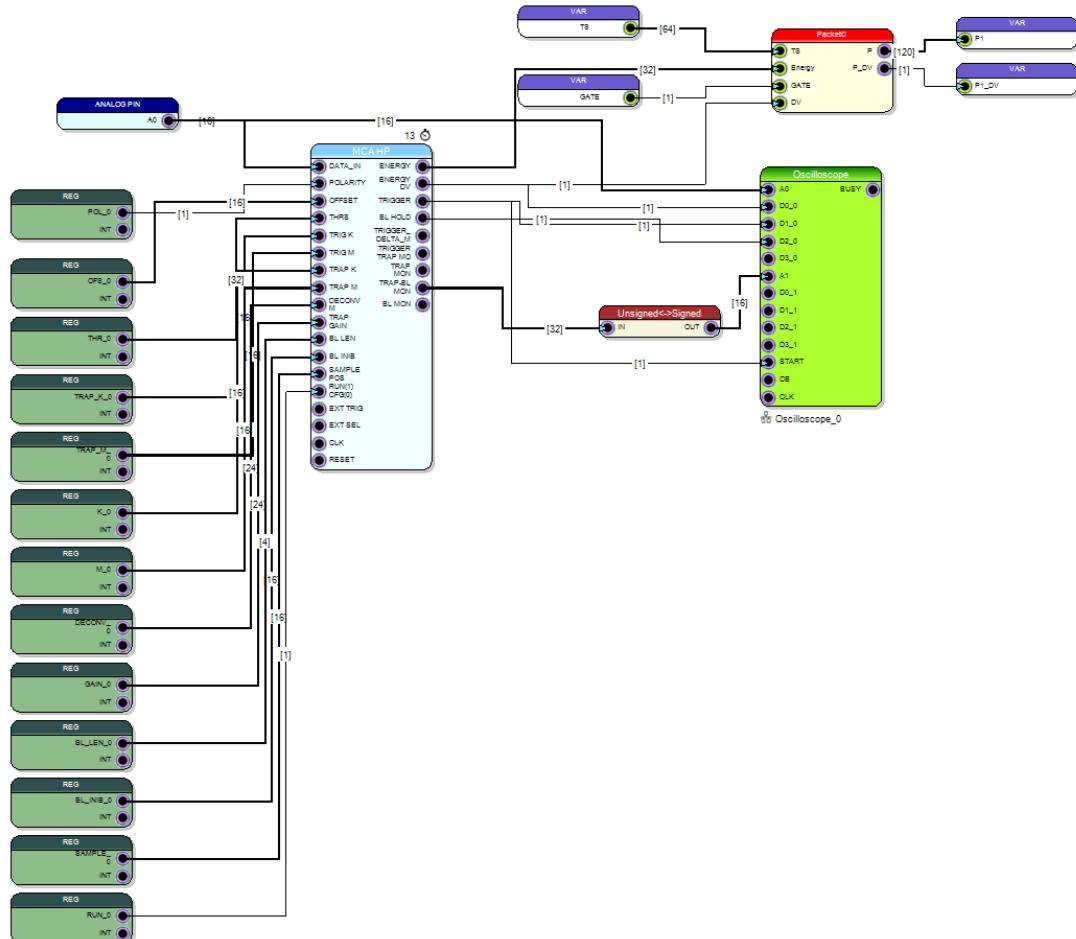

| Figure 14.1: SCI-Compiler scheme for single channel data processing in the default firmware. ....                                                                                                                           | 51 |

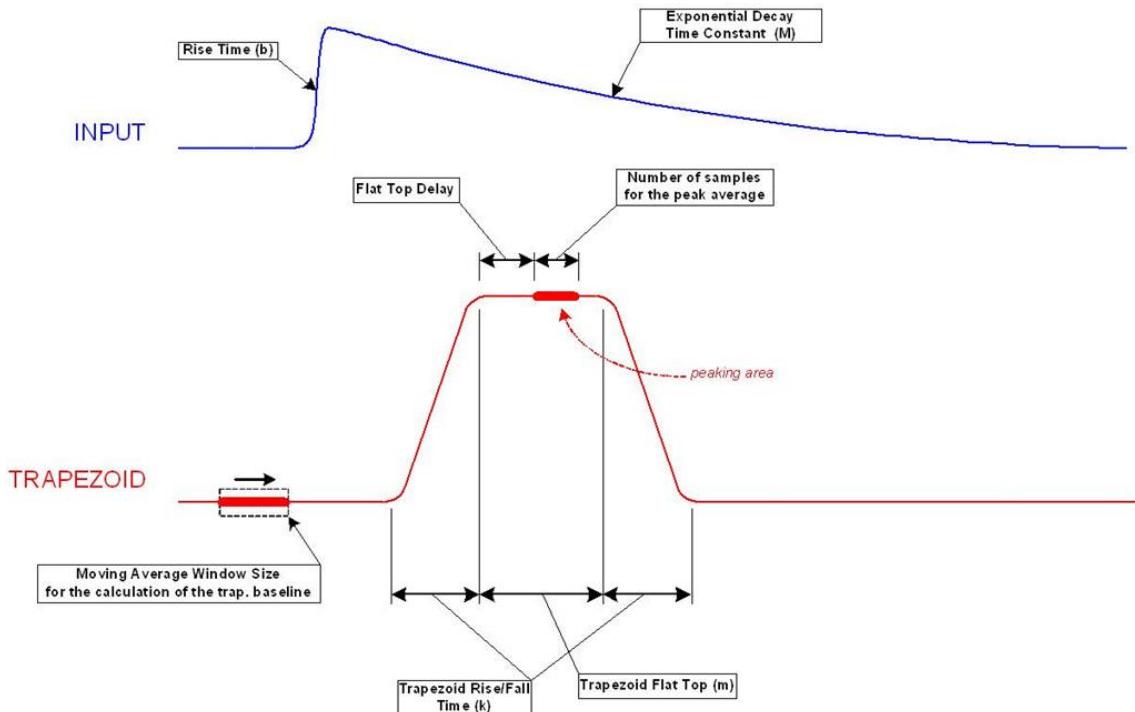

| Figure 14.2: the trapezoid method used in the board default firmware. ....                                                                                                                                                  | 52 |

| Figure 16.1: the "Connection" window at start-up of the Open Hardware Readout Software. ....                                                                                                                                | 60 |

| Figure 16.2: the main window of the Open Hardware Readout Software. The main areas are highlighted. ....                                                                                                                    | 61 |

| Figure 16.3: the Control Bar of the Open Hardware Readout Software. ....                                                                                                                                                    | 61 |

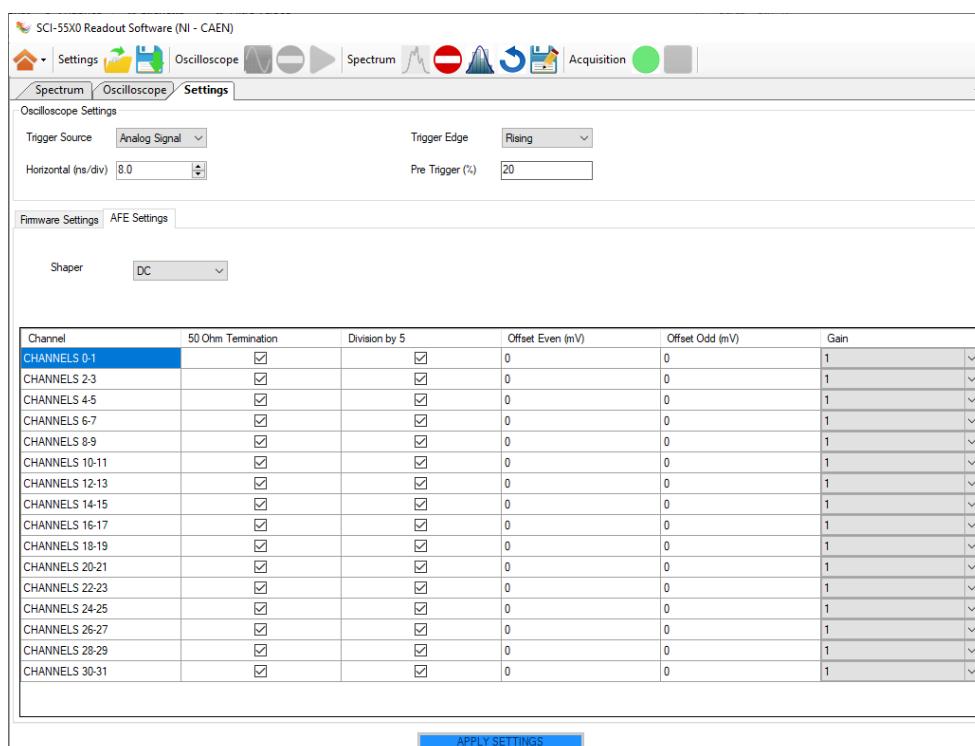

| Figure 16.4: the Settings Tab of the Open Hardware Readout Software. ....                                                                                                                                                   | 62 |

| Figure 16.5: scheme of the trapezoidal energy filter parameters to be set in the Open Hardware Readout Software. ....                                                                                                       | 64 |

| Figure 16.6: the AFE Settings tab in the Open Hardware Readout Software. ....                                                                                                                                               | 64 |

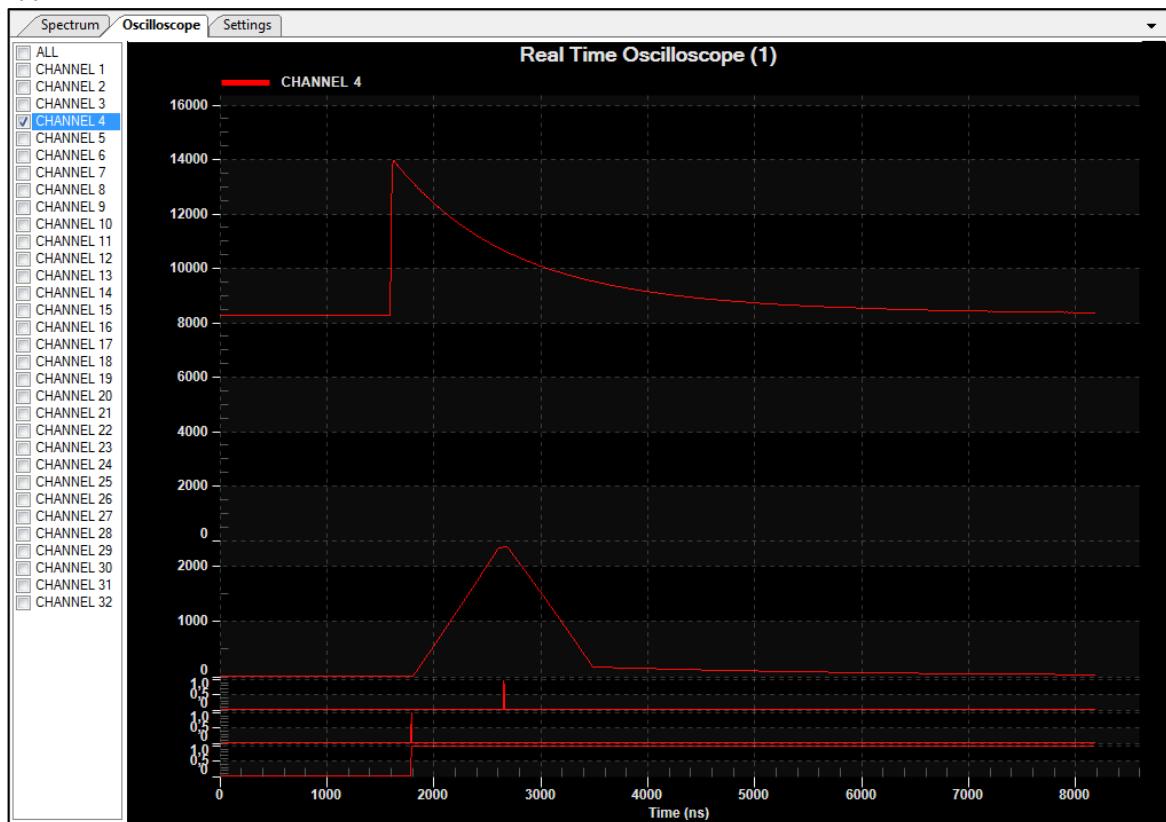

| Figure 16.7: the Oscilloscope Tab of the Open Hardware Readout Software. Here only signals for channel 4 are displayed. ....                                                                                                | 65 |

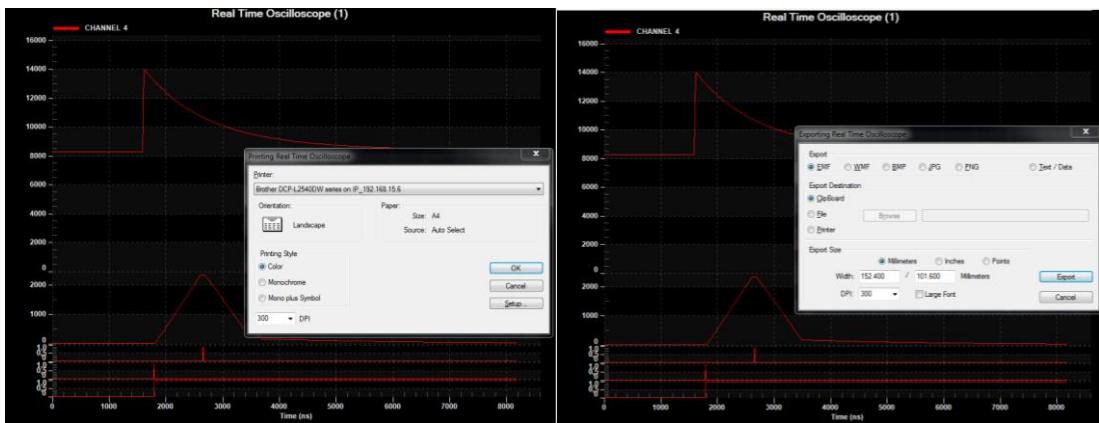

| Figure 16.8: printing (left) and saving to file (right) the current view of the Oscilloscope Tab ....                                                                                                                       | 66 |

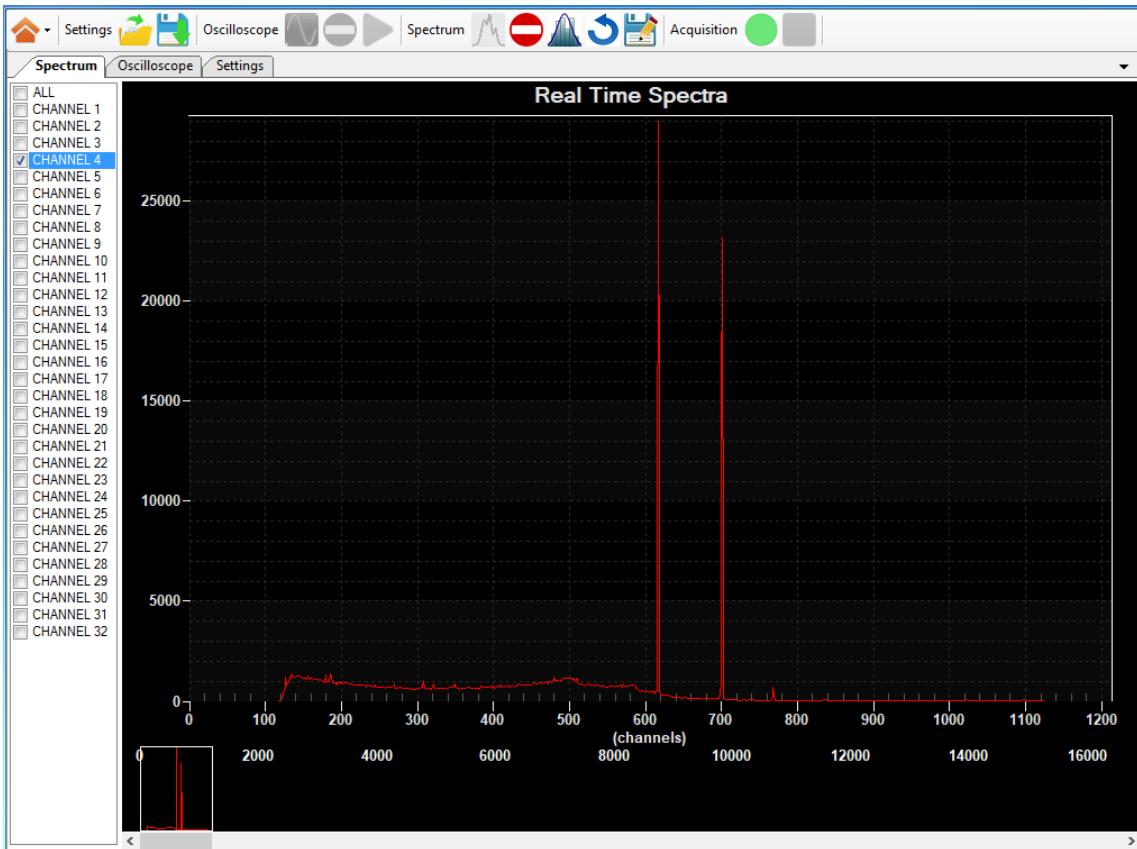

| Figure 16.9: the Spectrum Tab of the Open Hardware Readout Software. Here only the spectrum for channel 4 is displayed. ....                                                                                                | 67 |

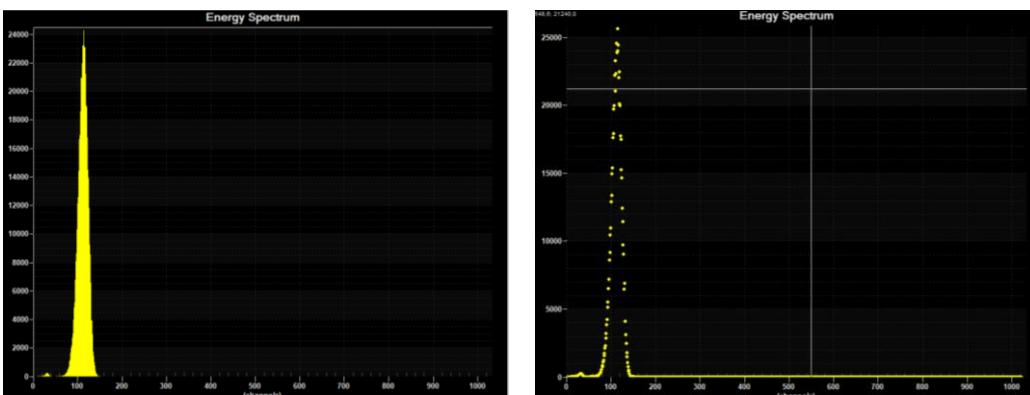

| Figure 16.10: spectra shown in different plot modes (left = Area, right = Dot). ....                                                                                                                                        | 67 |

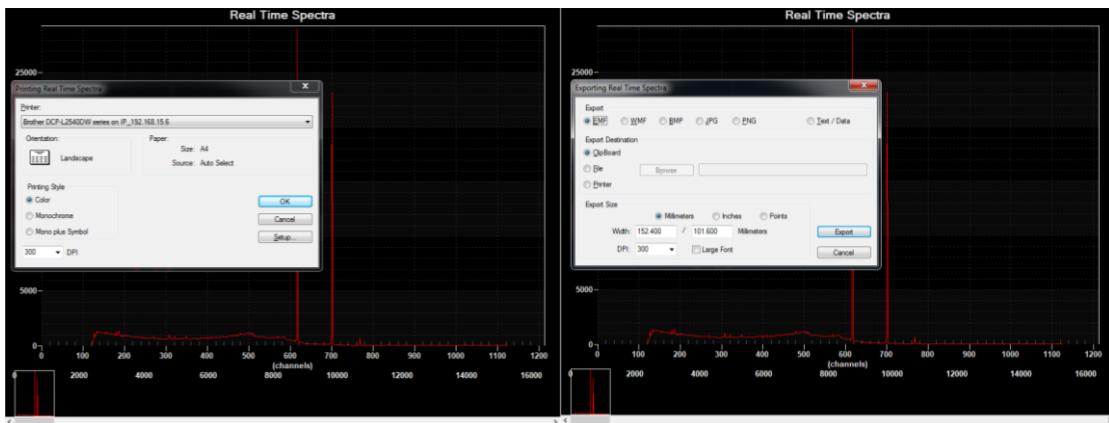

| Figure 16.11: printing (left) and saving to file (right) the current view of the Spectrum Tab. ....                                                                                                                         | 68 |

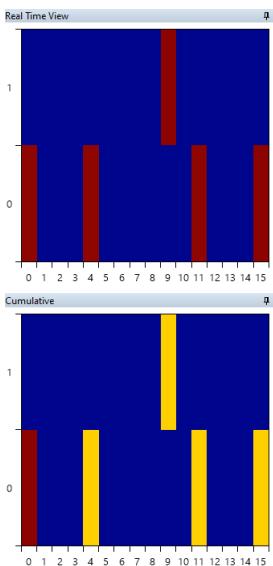

| Figure 16.12: the Imaging Module of the Open Hardware Readout Software, where it is possible to see 5 channels acquiring energy data. ....                                                                                  | 68 |

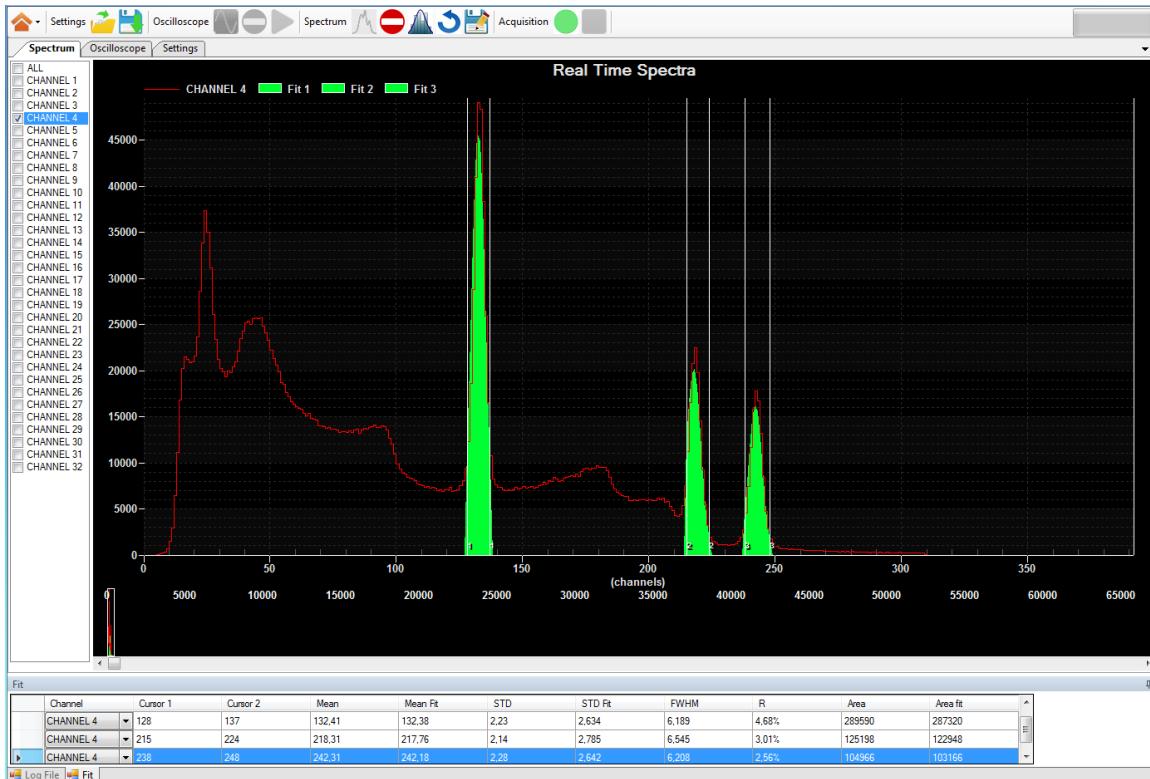

| Figure 16.13: the fitting tool of the Open Hardware Readout Software. ....                                                                                                                                                  | 69 |

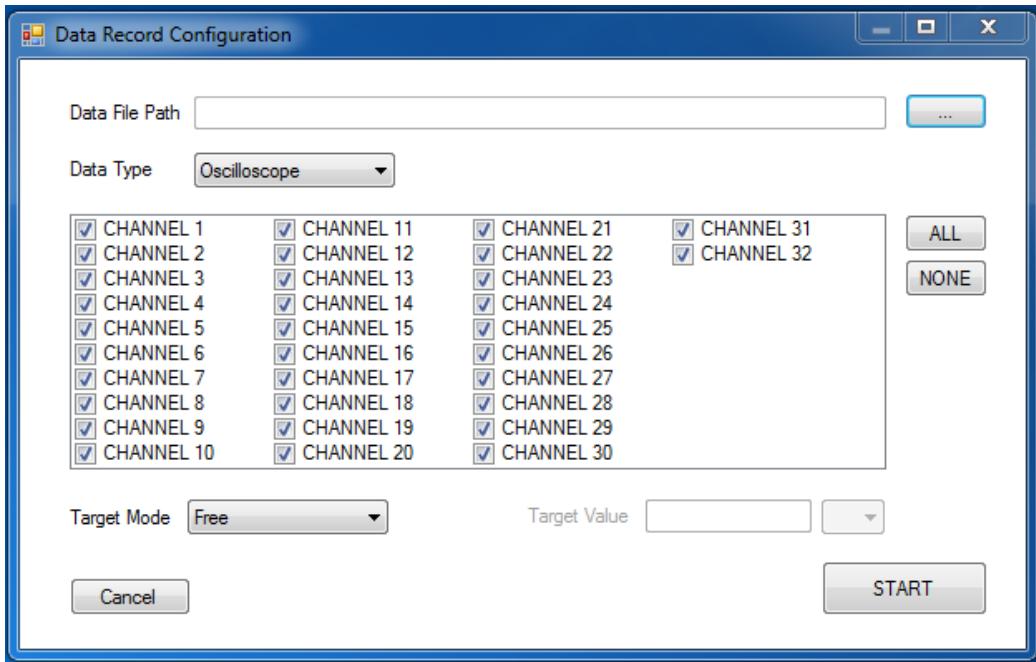

| Figure 16.14: the Data Record Configuration window. ....                                                                                                                                                                    | 70 |

| Figure 17.1: scheme for optical links operation for R5560SE. ....                                                                                                                                                           | 73 |

| Figure 17.2: scheme for optical links operation for R5560SEB ....                                                                                                                                                           | 74 |

## List of Tables

|                                                                  |    |

|------------------------------------------------------------------|----|

| Table 1.1: table of available board models and accessories. .... | 9  |

| Table 2.1: operating limits for R5560SE connectors. ....         | 11 |

|                                                                     |    |

|---------------------------------------------------------------------|----|

| Table 4.1: technical specifications for the R5560 and R5560SE.....  | 14 |

| Table 11.1: differential parameters for the R5560 analog input..... | 30 |

# 1 Introduction

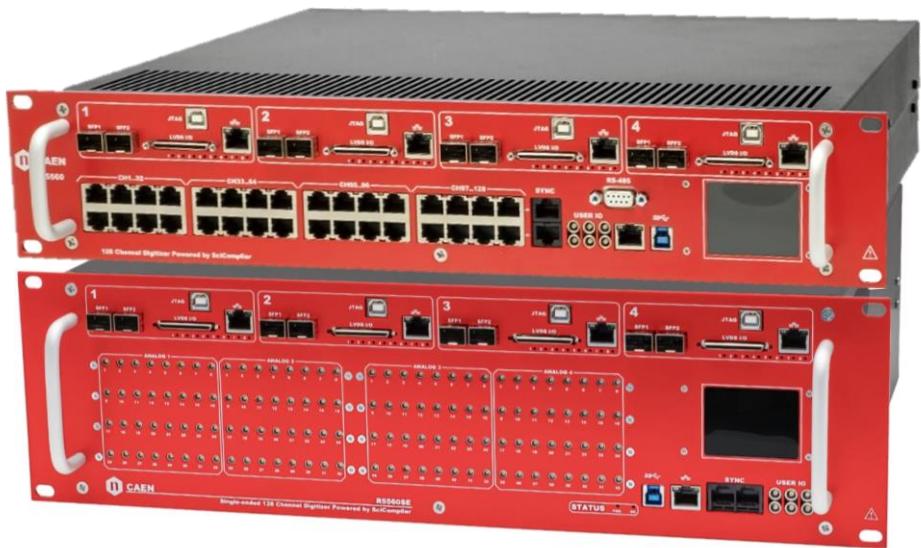

The R5560/R5560SE is a 19" rack-mount 128 Channels 14-bit 125MS/s **Open FPGA** Digitizer with **Differential or Single-Ended** inputs, designed to attain programmable data processing capabilities.

The R5560SE is an optimal solution for **large experiments**, usually requiring fast digitization of analog signals and usage of several digital lines to interface with external systems. The board supports **multi-board synchronization** through a single CAT5e cable, with the possibility scale up to thousands of channels. Moreover, the **rack-mount** form factor simplifies the experimental setup in case of multi-board systems, where an effective space management is often a constraint.

Thanks to its programmability, the board can fit several applications. In fact, it is possible to take advantage of the powerful SoC mounted onboard (Xilinx Zynq®-7030 or 7035 models) to write a **custom pulse processing algorithm** on the open FPGA as well as build a middleware/software that fits the needs of the application of interest.

The device is designed to operate in laboratory environment under the supervision of skilled technicians.

The R5560 features differential analog input on RJ45 connectors while the R5560SE features single-ended analog inputs on MCX connectors with an **advanced and versatile analog frontend**: it is possible to configure the gain, input impedance, offset on each single channel and also integrate a programmable shaper, making the device an optimum choice for gamma-rays applications.

The R5560/R5560SE is capable to manage simultaneously **digital** and **analog** signals to implement many functionalities required by physics experiments: signal digitization, complex trigger logic, Pulse Height Analysis with MCA capabilities, Time Tagging, Pulse Shape Discrimination, Scaler, Counters and so on.

Thanks to the Open FPGA and programmable analog frontend, the R5560SE can be used for a wide range of applications:

- Charge integration for the readout of SiPM, Silicon Detectors, PMTs

- Neutron detectors readout

- Trapezoidal filter PHA for HPGe readout

- Pulse shape discrimination

- Continuous reset or transistor reset preamplifier readout

The R5560/R5560SE is fully supported by **SCI-Compiler**, a Windows-based graphical development system for **easy FPGA programming**. This tool allows to develop and compile the firmware code using graphical blocks which represents the functionalities needed for firmware implementation (for example oscilloscope, TDC, MCA, charge integration, etc). SCI-Compiler automatically generates the VHDL firmware code starting only from logic blocks and virtual instruments that can be connected together in the GUI and, moreover, it allows usage of the compatible Sci-SDK in Windows, Linux (refer to **[RD1]** for more details).

A complete, ready-to-use default firmware is provided for free and open source. The default firmware manages the basic waveform digitization and pulse height analysis, and it is preloaded on the board. The user can open the default firmware project in SCI-Compiler and modify it in order to customize, for example, the trigger logic, the data online processing or integrate it in a larger system.

Available board models and accessories are listed below.

| Ordering options |                                                                  |               |

|------------------|------------------------------------------------------------------|---------------|

| R5560A           | R5560A – 128 Ch. 14 bit 125 MS/s Digitizer-7030                  | WR5560AXAAAA  |

| R5560B           | R5560B – 128 Ch. 14 bit 125 MS/s Digitizer-7035                  | WR5560BXAAAA  |

| R5560SE          | R5560SE – 128 Ch. 14 bit 125 MS/s Digitizer single-ended – 7030  | WR5560SEXAAA  |

| R5560SEB         | R5560SEB – 128 Ch. 14 bit 125 MS/s Digitizer single-ended - 7035 | WR5560SEBXAA  |

| Accessories      |                                                                  |               |

| SW55             | SCI-Compiler User Firmware Generator                             | WSW555XAAAAAA |

| RCS1Y            | 1 year remote customization service + upgrade for Sci-Compiler   | WSW55RCSXAAA  |

| RCS5Y            | 5 years remote customization service + upgrade for Sci-Compiler  | WSW55RCSX5YA  |

**Table 1.1:** table of available board models and accessories.

## 2 Safety Notices

**N.B. Read carefully the “Precautions for Handling, Storage and Installation” document provided with the product before starting any operation.**

The following HAZARD SYMBOLS may be reported on the unit:

|                                                                                     |                                   |

|-------------------------------------------------------------------------------------|-----------------------------------|

|    | Caution, refer to product manual  |

|    | Caution, risk of electrical shock |

|    | Protective conductor terminal     |

|   | Earth (Ground) Terminal           |

|  | Alternating Current               |

|  | Three-Phase Alternating Current   |

The following symbol may be reported in the present manual:

|                                                                                     |                           |

|-------------------------------------------------------------------------------------|---------------------------|

|  | General warning statement |

|-------------------------------------------------------------------------------------|---------------------------|

The symbol could be followed by the following terms:

- **DANGER:** indicates a hazardous situation which, if not avoided, will result in serious injury or death.

- **WARNING:** indicates a hazardous situation which, if not avoided, could result in death or serious injury.

- **CAUTION:** indicates a situation or condition that, if not avoided, could cause physical injury or damage the product and / or its environment.

To avoid potential hazards, use the product only as specified. Only qualified personnel should perform service procedures.

**Avoid Electric Overload.** To avoid electric shock or fire hazard, do not power a load outside of its specified range.

**Avoid Electric Shock.** To avoid injury or loss of life, do not connect or disconnect cables while they are connected to a voltage source.

**Do Not Operate without Covers.** To avoid electric shock or fire hazard, do not operate this product with covers or panels removed.

**Do Not Operate in Wet/Damp Conditions.** To avoid electric shock, do not operate this product in wet or damp conditions.

**Do Not Operate in an Explosive Atmosphere.** To avoid injury or fire hazard, do not operate this product in an explosive atmosphere.

**Do Not Operate with Suspected Failures.** If you suspect this product to be damaged, please contact Technical Support.

The following operating limits must be respected:

| Net class                 | Connector    | Unit                              | Min                | Max                 |

|---------------------------|--------------|-----------------------------------|--------------------|---------------------|

| Power                     | /            | Voltage                           | 90 V <sub>ac</sub> | 250 V <sub>ac</sub> |

| USER IO                   | LEMO         | Voltage                           | -0.1 V             | 3.6 V               |

| Digital lines             | Digital 2.5V | Voltage (3.3 V I/O bank selected) | 0 V                | 2.7 V               |

|                           |              | Current                           |                    | 10 mA               |

|                           | LVDS         | Voltage                           | 0.5 V              | 3 V                 |

|                           |              | Current                           |                    | 10 mA               |

|                           |              | Common Mode                       | 0.9 V              | 1.75 V              |

|                           | I2C/Serial   | Voltage                           | 0                  | 3.5 V               |

|                           | RS485/RS422  | Voltage                           | 0V                 | +5V                 |

| Analog Differential Input | RJ45         | Voltage                           |                    | 2 V <sub>pp</sub>   |

|                           |              | Common Mode                       | 0.5 V              | 3.8 V               |

|                           |              | V+,V- Absolute Range              | 0.5 V              | 3.8 V               |

| Analog SE Input           | MCX          | Voltage                           |                    | 1.5 V <sub>pp</sub> |

|                           |              | Common Mode                       | 0.5 V              | 3.8 V               |

|                           |              | V+,V- Absolute Range              | 0.5 V              | 3.8 V               |

Table 2.1: operating limits for R5560SE connectors.

**WARNING:** the digital lines are directly connected to the FPGA I/Os. Violation in maximum absolute rating illustrated in this document will likely destroy the FPGA. There is no buffer or protection on this line. That is necessary because we want to preserve the possibility to operate at different voltages and with both single ended and differential signals.

**THIS DEVICE SHOULD BE INSTALLED AND USED BY SKILLED TECHNICIANS ONLY OR UNDER THEIR SUPERVISION**

## 3 Block Diagram

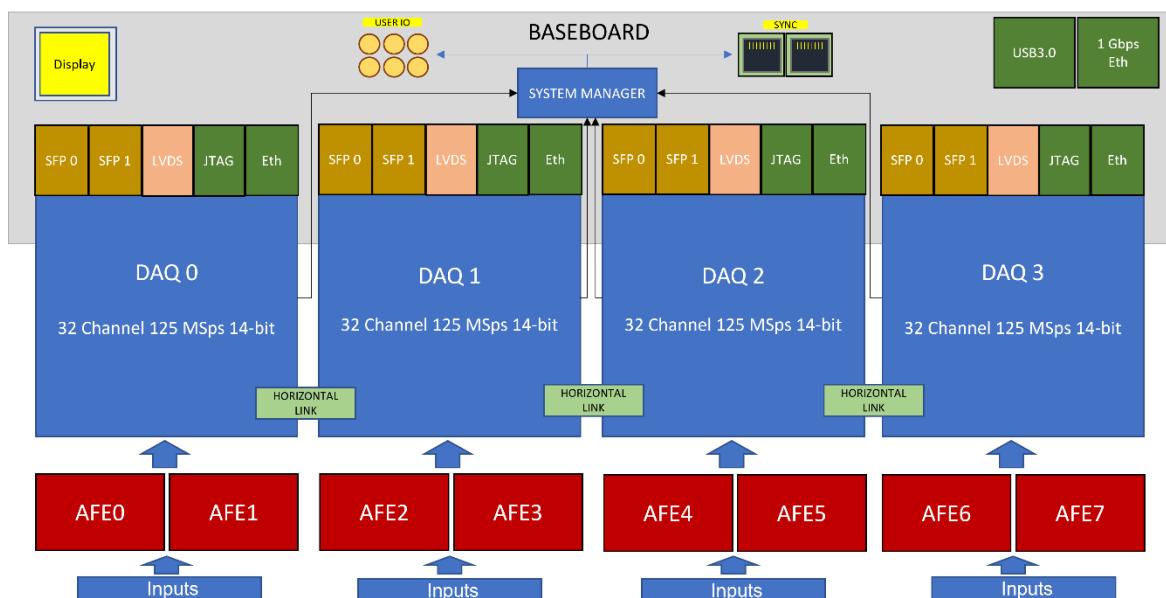

The R5560 is based on Xilinx Zynq-7000, a powerful System-on-Chip that uses a large programmable logic for massive real-time signal processing and a Dual Core 1GHz ARM processor for Ethernet communication and data post-processing. The board core is organized in 4 sections with **DAQ capabilities** and **Digital Interface**, each reading out 32 analog channels and hosting 32 configurable digital LVDS I/Os on VHDCI connector.

The R5560/R5560SE is organized as shown in **Figure 3.1**:

- **4 DAQ sections:** the DAQ section is the core of the system and it implements the analog-to-digital conversion, running the custom firmware generated by the SCI-Compiler. It is based on **Xilinx Zynq-7000**, a powerful System-on-Chip that uses a large programmable logic for massive real-time signal processing and a Dual Core 1GHz ARM processor for data post-processing. The DAQ section hosts readout interface (Optical Link, 1Gb Ethernet) and a JTAG USB connector, that allows for direct access to the FPGA for on-the-fly firmware upload and debug. The JTAG also gives access to the integrated USB-to-UART converter, which is useful to interface with a Linux console.

- **8 AFE sections (R5560SE only):** each DAQ is connected to two **analog frontend boards (AFE)**. The first AFE manages the analog input channels from 0 to 15 while the second the channels from 16 to 31. The AFE's function is to amplify the signal, regulate the offset, select the impedance, the input division and the shaping of the signal.

- the **baseboard** is used to interconnect all the board sections. It features a system manager to route digital signals from the DAQ to the SYNC connectors and USER IOs (and vice versa). It hosts the USB3.0 and 1Gbps Ethernet ports for slow control and cumulative readout of the 4 DAQ sections.

**Figure 3.1:** block diagram of the R5560/R5560SE. AFE sections are implemented in the R5560SE version only.

# 4 Technical Specifications

| TECHNICAL                      |                                                                                                                                                                                                  |                                                                                                                                                       |                                                                           |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|

| <b>POWER REQUIREMENTS</b>      | <b>Voltage:</b> 100-240 V <sub>ac</sub> $\pm$ 10%<br><b>Frequency:</b> 50/60 Hz<br><b>Typ. Power consumption:</b> 0.8 A @ 220 V <sub>ac</sub><br><b>Fuse:</b> 2A, 250V – 5 mm x 20 mm            |                                                                                                                                                       |                                                                           |  |  |

| <b>ANALOG INPUT – R5560</b>    | <b>Channels</b><br>128 Differential inputs                                                                                                                                                       | <b>Connector</b><br>32x CAT5e RJ45                                                                                                                    | <b>Bandwidth</b><br>125 MHz                                               |  |  |

|                                | <b>Impedance</b><br>$Z_{\text{diff}} = 100 \Omega$                                                                                                                                               | <b>Full Scale Range</b><br>$2 V_{\text{pp}}$                                                                                                          |                                                                           |  |  |

| <b>ANALOG INPUT – R5560SE</b>  | <b>Channels</b><br>128 single-ended inputs on MCX                                                                                                                                                |                                                                                                                                                       |                                                                           |  |  |

|                                | <b>Impedance</b><br>50 $\Omega$ /1 k $\Omega$ programmable                                                                                                                                       | <b>Analog Coarse Gain</b><br>[x1:x100]                                                                                                                | <b>Full Scale Range</b><br>[0.015 V <sub>pp</sub> : 1.5 V <sub>pp</sub> ] |  |  |

|                                | <b>Bandwidth</b><br>60 MHz                                                                                                                                                                       |                                                                                                                                                       |                                                                           |  |  |

|                                | Programmable DC offset adjustment on each input in the full scale range                                                                                                                          |                                                                                                                                                       |                                                                           |  |  |

| <b>DIGITAL I/Os</b>            | <b>Channels</b><br>4 x 32 Differential                                                                                                                                                           | <b>Connector</b><br>4x VHDCI                                                                                                                          | <b>Signal Type</b><br>LVCMOS 2.5V<br>LVDS<br>BLVDS                        |  |  |

|                                | <b>Impedance</b><br>$Z_{\text{diff}} = 100 \Omega$                                                                                                                                               | <b>Coupling</b><br>DC                                                                                                                                 |                                                                           |  |  |

| <b>USER I/Os</b>               | <b>Impedance</b><br>50 $\Omega$                                                                                                                                                                  | <b>Coupling</b><br>DC                                                                                                                                 |                                                                           |  |  |

| <b>DIGITAL CONVERSION</b>      | <b>Resolution</b><br>14 bits                                                                                                                                                                     | <b>Sampling Rate</b><br>125 MS/s Simultaneously on each channel                                                                                       |                                                                           |  |  |

| <b>CLOCK GENERATION</b>        | <b>125 MHz ADC clock</b><br>Clock sources: internal/external <ul style="list-style-type: none"> <li>Internal 25 MHz oscillator</li> <li>External 25 MHz – USER IN 0 or SYNC connector</li> </ul> |                                                                                                                                                       |                                                                           |  |  |

| <b>TRIGGER</b>                 | <b>Trigger Source</b><br><i>Internal/External</i> : managed by the default firmware                                                                                                              | <b>Trigger Propagation</b><br>Through USER I/Os and Sync Connector                                                                                    |                                                                           |  |  |

|                                | <i>Complex trigger logic</i> : implementable by the user on the open FPGA                                                                                                                        | <b>Trigger Time Stamp</b><br><i>Default FW</i> : 32-bit counter, 8 ns resolution, 26-day range;<br><i>Custom FW</i> : defined by the firmware design  |                                                                           |  |  |

| <b>SYNCHRONIZATION</b>         | <b>Clock Propagation</b><br>USER I/Os connectors<br>SYNC Connector                                                                                                                               | <b>Acquisition Synchronization</b><br>Through programmable LEMO<br>Through dedicated SYNC Connector                                                   |                                                                           |  |  |

|                                | <b>Open FPGA</b><br>4x Xilinx Zynq-7000 SoC:<br>Z-7030 (R5560A, R5560SEA)<br>Z-7035 model (R5560B, R5560SEB)                                                                                     | <b>Sync connector allows to cascade multiple units and synchronize them with a single standard CAT5e cable</b>                                        |                                                                           |  |  |

| <b>MEMORY</b>                  | 1 GByte of memory for list readout on each SoC                                                                                                                                                   |                                                                                                                                                       |                                                                           |  |  |

|                                | Up to 8kS/ch for simultaneous waveform readout                                                                                                                                                   |                                                                                                                                                       |                                                                           |  |  |

| <b>COMMUNICATION INTERFACE</b> | <b>Ethernet (readout)</b><br>4 x 1Gbps (4 Gbps cumulative speed)                                                                                                                                 | All readout interfaces allow to perform the same task at different speed and using different media. They can be used independently or simultaneously. |                                                                           |  |  |

|                                | <b>Ethernet (slow control)</b><br>1 Gbps (slow control is an additional port, not required if the fast readout ethernet is used)                                                                 | The different readout interface allows to integrate the R5560SE in existing experimental environment.                                                 |                                                                           |  |  |

|                                | <b>Optical Link</b>                                                                                                                                                                              |                                                                                                                                                       |                                                                           |  |  |

|                              |                                                                                                                                                                                         |                                                                 |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                              | Slots for 8 x 10Gbps SFP+ transceivers<br>(communication protocol <u>not</u> implemented by default)                                                                                    |                                                                 |

|                              | <b>USB 3.0</b><br>1x USB 3.0 readout                                                                                                                                                    |                                                                 |

|                              | <b>PARALLEL TTL/LVDS Readout</b><br>Readout through the VHDCI digital I/O on custom protocol                                                                                            |                                                                 |

| <b>FIRMWARE</b>              | <b>Default</b><br>-Waveform recording and Pulse Height Analysis<br>- Ethernet communication                                                                                             | <b>Custom</b><br>Use SCI-Compiler to develop your own firmware! |

| <b>SOFTWARE</b>              | <ul style="list-style-type: none"> <li>• <b>Open Hardware Readout Software</b> to manage the default firmware</li> <li>• <b>SCI-Compiler</b> for custom firmware development</li> </ul> |                                                                 |

| <b>MECHANICAL</b>            |                                                                                                                                                                                         |                                                                 |

| <b>FORM FACTOR</b>           | R5560 - 19", 2U Rack-mount<br>R5560SE - 19", 3U Rack-mount                                                                                                                              |                                                                 |

| <b>DIMENSIONS (H/W/L)</b>    | R5560 - 88/482.0/367.0 (396 with handles) mm<br>R5560SE - 132.5/482.0/366.0 (399.8 with handles) mm                                                                                     |                                                                 |

| <b>ENVIRONMENTAL</b>         |                                                                                                                                                                                         |                                                                 |

| <b>ENVIRONMENTAL</b>         | Indoor use                                                                                                                                                                              |                                                                 |

| <b>OPERATING TEMPERATURE</b> | Operating Temperature -20 °C ÷ 50 °C                                                                                                                                                    |                                                                 |

| <b>OPERATING HUMIDITY</b>    | 25% ÷ 95% RH non condensing                                                                                                                                                             |                                                                 |

| <b>STORAGE TEMPERATURE</b>   | -30 °C ÷ +80 °C                                                                                                                                                                         |                                                                 |

| <b>STORAGE HUMIDITY</b>      | 5% ÷ 90% RH non condensing                                                                                                                                                              |                                                                 |

| <b>ALTITUDE</b>              | ≤2000 m                                                                                                                                                                                 |                                                                 |

| <b>POLLUTION DEGREE</b>      | 2                                                                                                                                                                                       |                                                                 |

| <b>OVERVOLTAGE CATEGORY</b>  | II                                                                                                                                                                                      |                                                                 |

| <b>EMC ENVIRONMENT</b>       | Commercial and light industrial                                                                                                                                                         |                                                                 |

| <b>IP DEGREE</b>             | IPX0 enclosure, not for wet location                                                                                                                                                    |                                                                 |

| <b>REGULATORY</b>            |                                                                                                                                                                                         |                                                                 |

| <b>COMPLIANCE</b>            | <ul style="list-style-type: none"> <li>• EMC: CE 2014/30/EU Electromagnetic compatibility Directive</li> <li>• Safety: CE 2014/35/EU Low Voltage Directive</li> </ul>                   |                                                                 |

**Table 4.1:** technical specifications for the R5560 and R5560SE.

## 5 Packaging and compliancy

The R5560/R5560SE is available as 19" rackmount module housed in an aluminium case.

The unit is inspected by CAEN before the shipment, and it is guaranteed to leave the factory free of mechanical or electrical defects.

When receiving the unit, the user is strictly recommended to inspect for any damage which may have occurred during transportation. Particularly, inspect for exterior damages like broken connectors and check that the panel is not scratched or cracked.

All packing material should be held on until the inspection has been completed. If damage is detected, the user must file a claim with the carrier immediately and notify CAEN.

Before installing the unit, make sure to read thoroughly the safety rules and installation requirements (Sec. **Safety Notices**), then place the package content onto your bench.

The content of the delivered package standardly consists of the part list shown in the table below (

**Table 5.1**). All the official documentation, firmware updates, software tools, and accessories are available on [www.caen.it](http://www.caen.it) at the product web page.

|                                                                                     | Part               | Description                                                                               | Qty |

|-------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------|-----|

|    | R5560/R5560SE      | 128 Ch. 14 bit 125 MS/s Digitizer                                                         | x1  |

|  | Power supply cable | Standard C13 power supply chord                                                           | x1  |

|  | USB cable          | USB 2.0 141/5HS type A-B I/O cable L=2MT                                                  | x1  |

|  | Ethernet cable     | ETHERNET CAT6 cable L=2MT                                                                 | x4  |

|  | SCI-Compiler       | USB Dongle for SCI-Compiler software<br><b>(if included in your board purchase order)</b> | x1  |

|  | User guide         | UM6952 – R5560/R5560SE User Manual                                                        | x1  |

**Table 5.1:** delivered kit.

**CAUTION:** to manage the product, consult the operating instructions provided.

It is recommended to:

- Inspect containers for damage during shipment. Report any damage to the freight carrier for possible insurance claims.

- Check that all the components received match those listed on the enclosed packing list. (CAEN cannot accept responsibility for missing items unless we are notified promptly of any discrepancies.)

- Open shipping containers; be careful not to damage contents.

- Inspect contents and report any damage. The inspection should confirm that there is no exterior damage to the unit such as broken knobs or connectors and that the front panel and display face are not scratched or cracked. Keep all packing material until the inspection has been completed.

- If damage is detected, file a claim with carrier immediately and notify CAEN service.

- If equipment must be returned for any reason, carefully repack equipment in the original shipping container with original packing materials if possible. Please contact CAEN service.

- If equipment is to be installed later, place equipment in original shipping container and store in a safe place until ready to install

**DO NOT SUBJECT THE ITEM TO UNDUE SHOCK OR VIBRATIONS**

**DO NOT BUMP, DROP OR SLIDE SHIPPING CONTAINERS**

**DO NOT LEAVE ITEMS OR SHIPPING CONTAINERS UNSUPERVISED IN AREAS WHERE UNTRAINED PERSONNEL MAY MISHANDLE THE ITEMS**

**USE ONLY ACCESSORIES WHICH MEET THE MANUFACTURER SPECIFICATIONS**

## SCI-Compiler License

R5560SE is compatible with SCI-Compiler ([RD1][RD2]), the Windows-based CAEN **firmware generator and compiler** for **easy FPGA programming**. It is an **automatic code generator** that, starting from a graphical block diagram, generates a VHDL piece of code that implements the required function. The software uses a prebuilt library set containing macroblocks implementing complex functions (MCA, Oscilloscope, Digitizer, TDC) that the user can connect one with each other. SCI-Compiler is also able to generate C libraries and drivers to be used in **Windows**, **Linux** and **macOS** for DAQ software implementation.

**Note:** SCI-Compiler full version works upon the purchase of a license, contact CAEN at [info@caen.it](mailto:info@caen.it) for more information.

**Note:** the board needs a runtime license to run SCI-Compiler-based firmware, contact CAEN at [info@caen.it](mailto:info@caen.it) for more information.

**Note:** a 30D trial version of SCI-Compiler is available for free at [www.sci-compiler.com](http://www.sci-compiler.com).

Full version of SCI-Compiler is accessible after activation of the **software license** on CAEN website using the **SERIAL NUMBER** and an **ACTIVATION** key provided together with the USB Dongle. The USB Dongle must be plugged into the PC to run SCI-Compiler full version. The generated firmware can be uploaded on each compatible board that has been activated with a **SCI-Compiler Runtime license** on CAEN website. Refer to [RD1] and [RD2] for more details.

**Figure 5.1:** SCI-Compiler USB Dongle and keys for license activation.

**Note:** user is not allowed to use the code generated by the SCI-Compiler on boards different from R5560SE. Even using a small part of the code generate by the SCI-Compiler on a custom design board or other products is an explicit violation of the license terms and it is an offense against CAEN S.p.A and Nuclear Instruments S.R.L.

## 6 PID (Product Identifier)

PID is the CAEN product identifier, an incremental number greater than 10000 that is unique for each product. The PID is on a label affixed to the product (**Fig. 6.1**) and it is even stored in an on-board non-volatile memory readable via touchscreen, Web Interface or Readout Software (see Chap. **Touchscreen Display Guide**, **Web Interface** and **Open Hardware Readout** Software).

**Fig. 6.1:**PID location taking a CAEN rack unit as an example (the number in the picture and the device model are purely indicative)

## 7 Power Requirements

The R5560/R5560SE is powered by an internal 100/240V-12V AC/DC stabilized power supply.

The power supply chord is included in the delivered kit and it is connected to equipment using an IEC C14 connector on the back panel. The power chord is a standard wall IEC C13.

## 8 Cooling Management

The R5560/R5560SE board can operate in the temperature range -20 °C ÷ 50 °C.

Air flow fans are installed onboard. The user must take care to provide a proper cooling to the board with external fan if the board is used in an enclosure or if the board is installed in a setup with poor air flow.

Excessive temperature will, in first instance, reduce the performance and the quality of the measurements and can also damage the board.

The unit dissipates almost 100W. Please do not close the rear fan holes to avoid unit overheating. If in a single rack tower, multiple units are installed, please consider external fans or rack mounted air conditioning system.

If the board is stored in cold environmental, please check for water condensation before power on.

The board has not been tested for radiation hardness. High energy particle can be source of soft error and can damage the FPGA. If used in strong proton or neutron beams, arrange proper shielding or remote the sensor with a custom cable.

### Cleaning the air vents

CAEN recommends to occasionally clean the air vents on all vented sides of the board. Lint, dust, and other foreign matter can block the vents and limit the airflow. Be sure to unplug the board before cleaning the air vents and follow the general cleaning safety precautions.

## 9 Installing the device

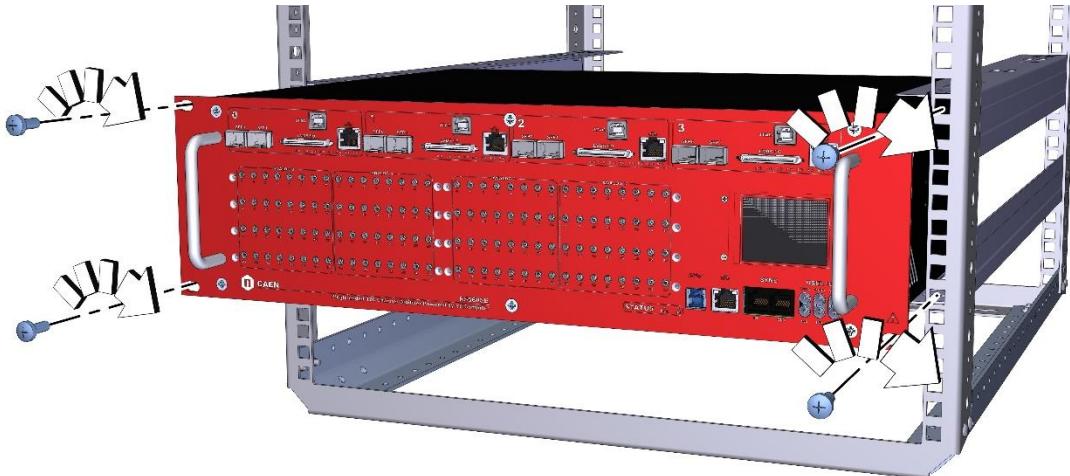

The device should be installed in 19" rack as detailed in the following steps:

1. Ensure you have the correct bolts needed to secure the device in your rack (bolts not included)

2. Carefully slide the system into an available 3U space in your 19-inch rack.

3. Screw the four locking bolts

4. Connect power supply chord to the AC power supply C14 inlet connector on the rear panel

Figure 9.1: installing the device into a 19" rack

**ONLY QUALIFIED PERSONNEL SHOULD PERFORM INSTALLATION OPERATIONS**

**DO NOT INSTALL THE EQUIPMENT SO THAT IT IS DIFFICULT TO ACCESS THE SWITCH AND POWER CONNECTION ON THE BACK PANEL**

**IT IS RECOMMENDED THAT A CIRCUIT-BREAKER IS NEAR THE EQUIPMENT**

**THE SAFETY OF ANY SYSTEM THAT INCORPORATES THE DEVICE IS UNDER THE RESPONSIBILITY OF THE ASSEMBLER OF THE SYSTEM**

Do not use the device and contact technical support if one of these situations is verified:

- Enclosure integrity is compromised

- Insulation of HV chord is damaged (if present)

- The indication led or display is not performing as required (e.g. led not working, display with incorrect graphic)

- Fans are not working (if present)

# 10 Panels Description

## R5560 dimensions

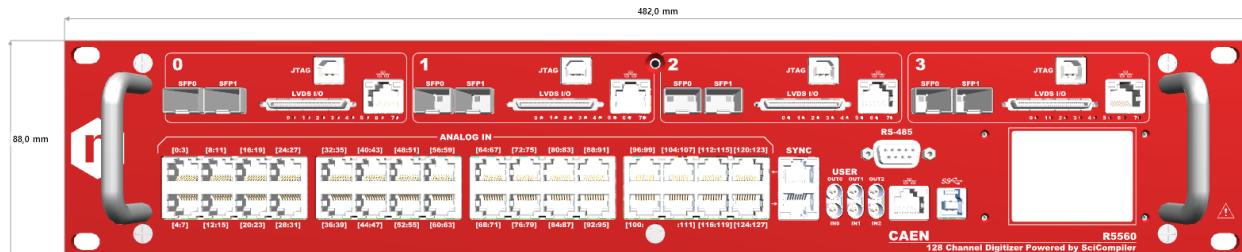

The R5560 unit is housed in a standard 2U 19" rackmount aluminium box.

Figure 10.1: R5560 front panel view and dimensions.

Figure 10.2: R5560 rear panel view and dimensions.

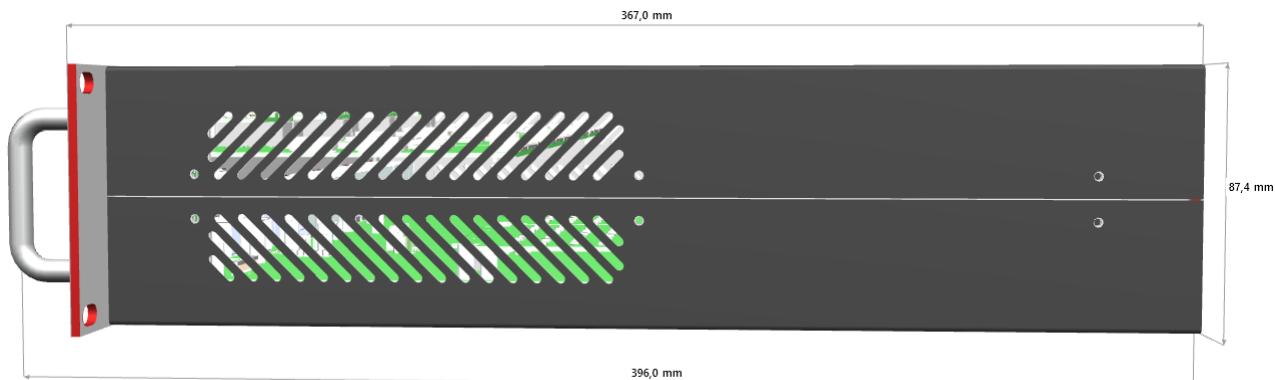

Figure 10.3: R5560 side view and dimensions.

## R5560SE dimensions

The R5560SE unit is housed in a standard 3U 19" rackmount aluminium box.

**Figure 10.4:** R5560SE Front panel view and dimensions.

**Figure 10.5:** R5560SE Rear panel view and dimensions.

**Figure 10.6:** R5560SE side view and dimensions.

## Front Panel

| DIFFERENTIAL ANALOG INPUT – R5560 only                                              |                                                                                                                                                           |                                                                                                       |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|    | <b>FUNCTION</b>                                                                                                                                           | <b>MECHANICAL Specs</b>                                                                               |

|                                                                                     | 8 x RJ45 connectors carrying 32 analog differential signals. Compatible with standard Ethernet cable CAT5e with standard ethernet pinout                  | Series: RJ45.<br>Suggested plug: Ethernet crimp plug<br>Suggested cable: Cat5e or Cat6 ethernet cable |

|                                                                                     | <b>ELECTRICAL Specs</b>                                                                                                                                   | <b>PINOUT</b>                                                                                         |

|                                                                                     | Sign. type: differential (Analog 0...3V Common Mode, 2Vpp differential signal).<br>Coupling: DC.<br>$Z_{diff}$ : 100 $\Omega$ .                           |                    |

| SINGLE-ENDED ANALOG INPUT – R5560SE only                                            |                                                                                                                                                           |                                                                                                       |

|   | <b>FUNCTION</b>                                                                                                                                           | <b>MECHANICAL Specs</b>                                                                               |

|                                                                                     | Input connectors from CH0 to CH31 on four different sections. They receive the single-ended input analog signals.                                         | Series: MCX                                                                                           |

|                                                                                     | <b>ELECTRICAL Specs</b>                                                                                                                                   |                                                                                                       |

|                                                                                     | Input dynamics: [1.5 : 0.015] V <sub>pp</sub><br>Input impedance: 50 $\Omega$ / 1k $\Omega$                                                               |                                                                                                       |

| JTAG                                                                                |                                                                                                                                                           |                                                                                                       |

|  | <b>FUNCTION</b>                                                                                                                                           | <b>MECHANICAL Specs</b>                                                                               |

|                                                                                     | Connector for direct FPGA access in order to perform fast firmware download and FPGA signals monitor and probing                                          | Series: USB 2.0 - B                                                                                   |

|                                                                                     | <b>ELECTRICAL Specs</b>                                                                                                                                   |                                                                                                       |

|                                                                                     | Standard: compliant with USB 2.0                                                                                                                          |                                                                                                       |

| ETHERNET                                                                            |                                                                                                                                                           |                                                                                                       |

|  | <b>FUNCTION</b>                                                                                                                                           | <b>MECHANICAL Specs</b>                                                                               |

|                                                                                     | 1 Gbps Ethernet interface                                                                                                                                 | Series: RJ45                                                                                          |

|                                                                                     | <ul style="list-style-type: none"> <li>4 ports for high-speed readout, one for each section</li> <li>1 port for slow control</li> </ul>                   |                                                                                                       |

|                                                                                     |  Slow control communication is not implemented in the default firmware |                                                                                                       |

|                                                                                     | <b>ELECTRICAL Specs</b>                                                                                                                                   |                                                                                                       |

|                                                                                     | <i>Not available</i>                                                                                                                                      |                                                                                                       |

| OPTICAL LINK                                                                        |                                                                                                                                                           |                                                                                                       |

|  | <b>FUNCTION</b>                                                                                                                                           | <b>MECHANICAL Specs</b>                                                                               |

|                                                                                     | Slot for SFP+ connector. 10 Gbps optical transceiver can be inserted here                                                                                 | Series SFP+ socket                                                                                    |

|                                                                                     |  SFP+ transceivers are <u>not</u> provided with the board kit          |                                                                                                       |

|                                                                                                                                                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  Optical link communication is not implemented in the default firmware |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                   |

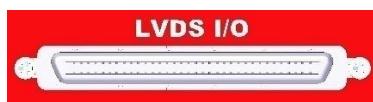

| <b>LVDS I/O</b>                                                                                                                                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                   |

|                                                                        | <b>FUNCTION</b><br>68-pin connector carrying 32/64 differential input digital signals<br><b>ELECTRICAL Specs</b><br>Sign. type: differential (LVCMS 2.5V, LVDS, BLVDS).<br>$Z_{diff}$ : 100 $\Omega$                                                                         | <b>MECHANICAL Specs</b><br>Series: VHDCI connector.<br>Type: 71430-0008<br>Manufacturer: TE Connectivity<br>Suggested plug: 68-pin VHDCI<br>Suggested cable: SCSI-5 type.<br><b>PINOUT</b><br> |

| <b>LEDs</b>                                                                                                                                             |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                   |

|                                                                        | <b>FUNCTION</b><br>8 user-configurable LEDs<br><b>ELECTRICAL Specs</b><br><i>Not available</i>                                                                                                                                                                               | <b>MECHANICAL Specs</b><br>Not available                                                                                                                                                                                                                                          |

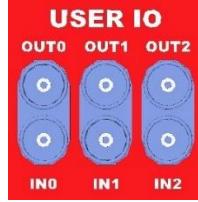

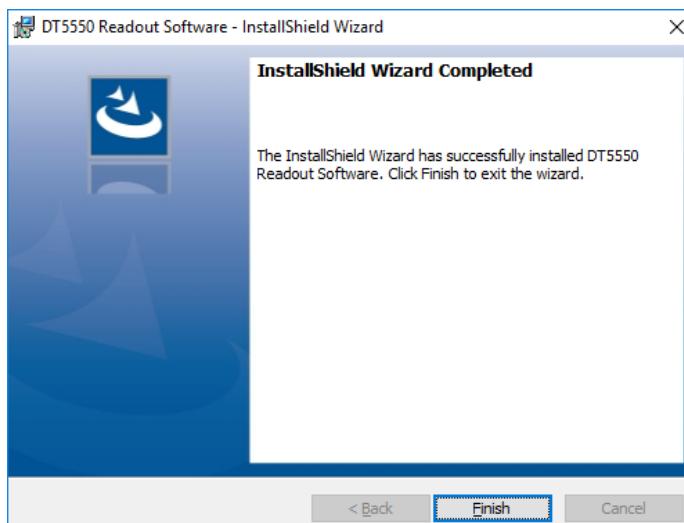

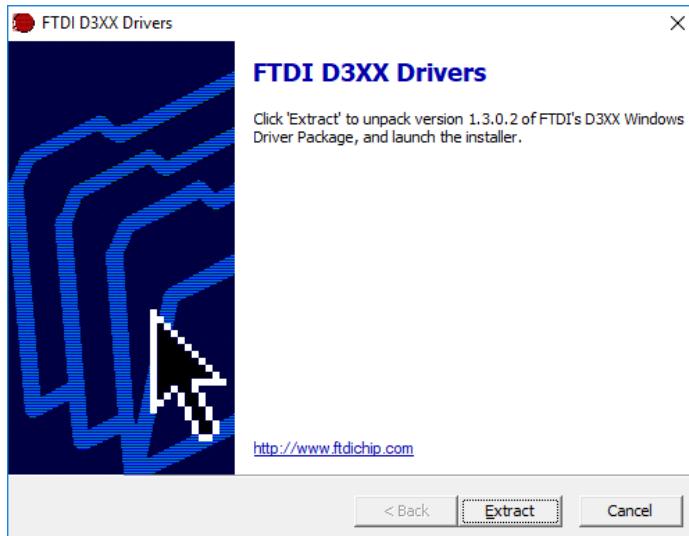

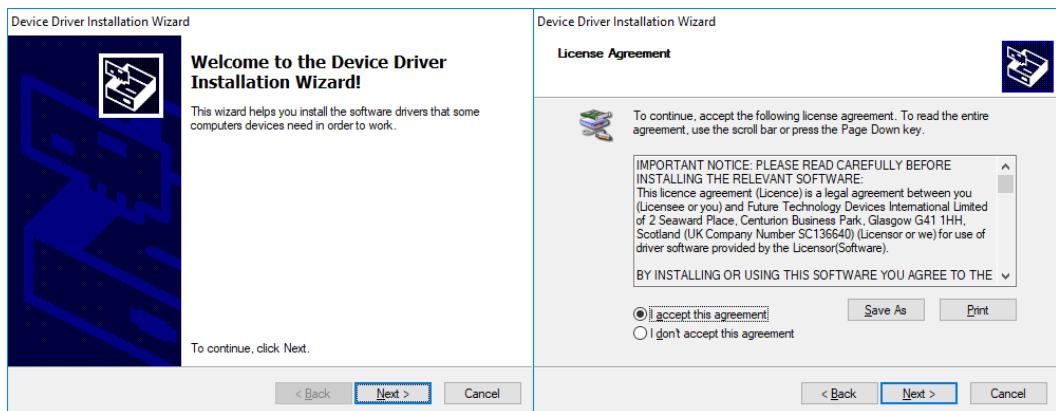

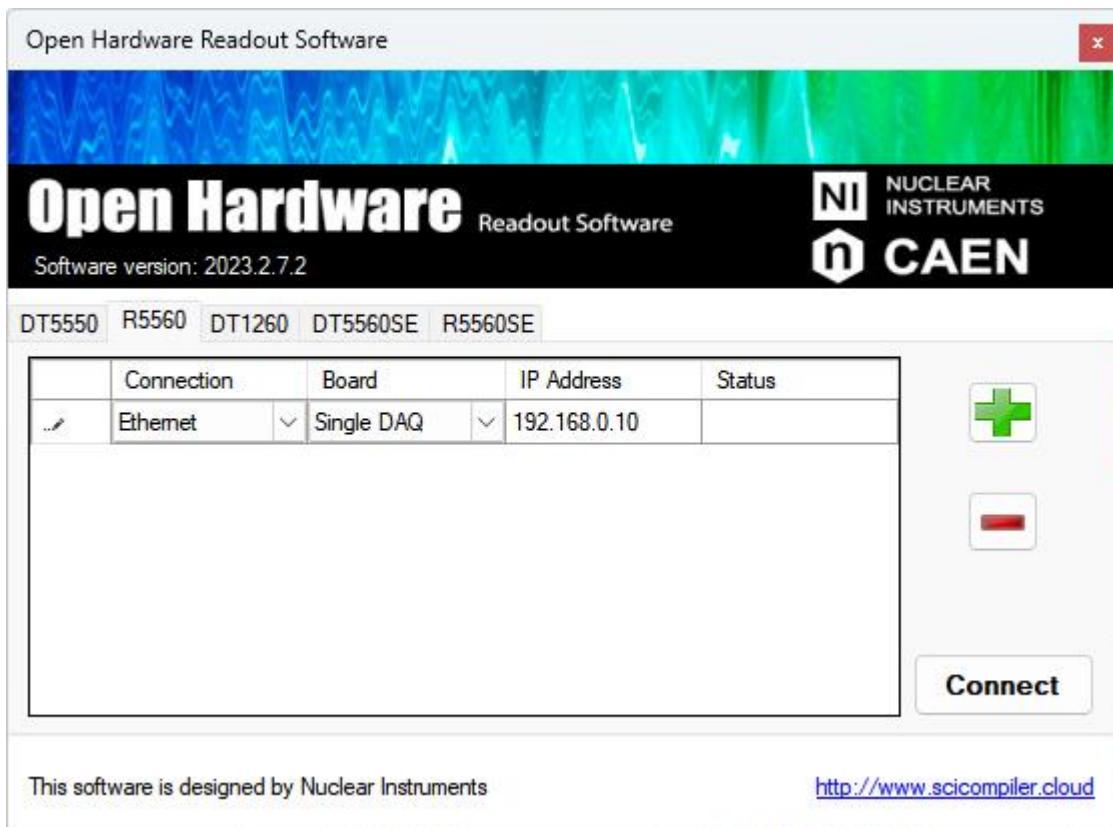

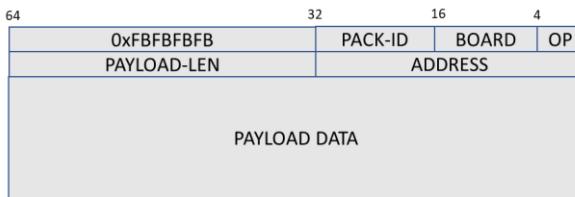

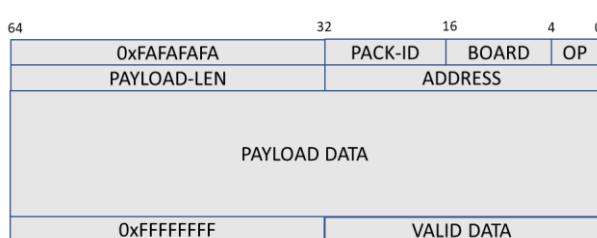

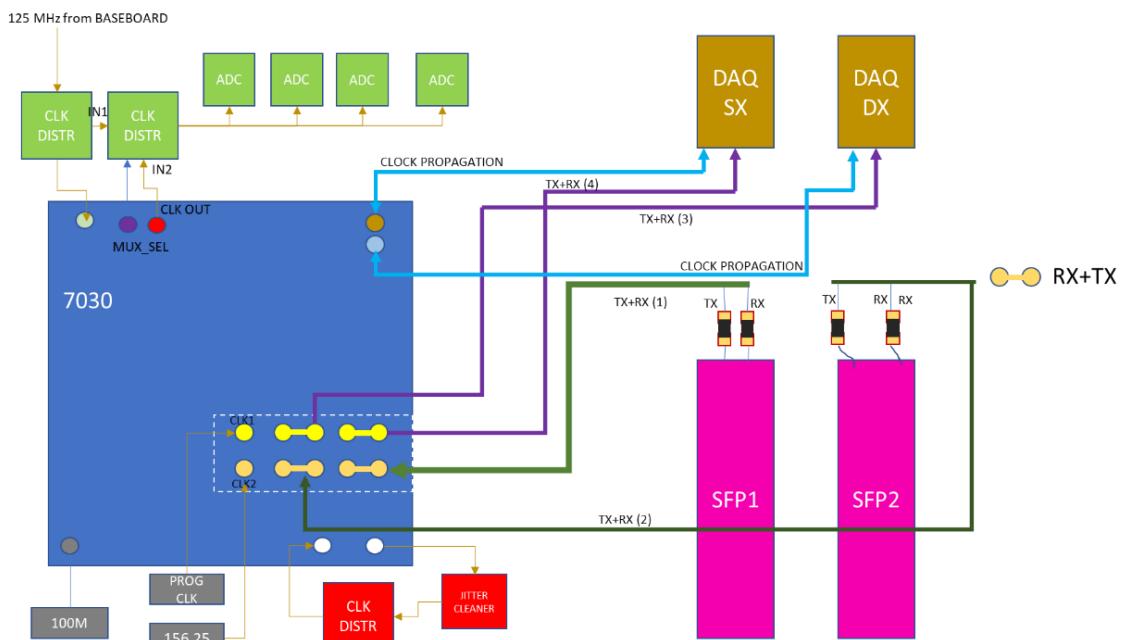

| <b>USER IOs</b>                                                                                                                                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                   |