# PRELIMINARY

User Manual UM6698

## A55PETx

PETIROC Piggyback Board for DT5550W

Rev. 5 - March 2nd, 2022

# Purpose of this User Manual

This User Manual contains the full description of the A55PETx Piggyback Boards family for DT5550W.

## Change Document Record

| Date                             | Revision | Changes                                                                                                                            |

|----------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| November 6 <sup>th</sup> , 2018  | 00       | Initial release                                                                                                                    |

| March 6 <sup>th</sup> , 2019     | 01       | Modified <b>SiPM connection and biasing</b> with additional information on the pitch adapter.<br>Modified <b>Technical Support</b> |

| July 18 <sup>th</sup> , 2019     | 02       | Modified <b>DT5550W Readout Software</b> .<br>Revised <b>SiPM connection and biasing</b>                                           |

| February 21 <sup>st</sup> , 2020 | 03       | Revised <b>DT5550W Readout Software</b> .<br>Added <b>Multiboard readout script</b>                                                |

| July 2 <sup>nd</sup> , 2021      | 04       | Revised <b>Time Measurements</b>                                                                                                   |

| March 2 <sup>nd</sup> , 2022     | 05       | General revision                                                                                                                   |

## Symbols, abbreviated terms and notation

|      |                                 |

|------|---------------------------------|

| ADC  | Analog to Digital Converter     |

| FPGA | Field Programmable Gate Array   |

| OEM  | Original Equipment Manufacturer |

| OS   | Operating system                |

| PHA  | Pulse Height Analysis           |

## Reference Document

- [RD1] PETIROC 2A Datasheet (available on WeeROC website)

- [RD2] UM6697 - DT5550W User Manual

- [RD3] UM6377 – A7585 DT5485 User Manual

- [RD4] DS8241 – Remotization kit datasheet

## Manufacturer contact

**CAEN S.p.A.**

Via Vetraia, 11 55049 Viareggio (LU) - ITALY

Tel. +39.0584.388.398 Fax +39.0584.388.959

[www.caen.it](http://www.caen.it) | [info@caen.it](mailto:info@caen.it)

© CAEN SpA – 2022

## Limitation of responsibility

If the warnings contained in this manual are not followed, CAEN will not be responsible for damage caused by improper use of the device. The manufacturer declines all responsibility for damage resulting from failure to comply with the instructions for use of the product. The equipment must be used as described in the user manual, with particular regard to the intended use, using only accessories as specified by the manufacturer. No modification or repair can be performed.

**Disclaimer**

No part of this manual may be reproduced in any form or by any means, electronic, mechanical, recording, or otherwise, without the prior written permission of CAEN spa.

The information contained herein has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. CAEN spa reserves the right to modify its products specifications without giving any notice; for up to date information please visit [www.caen.it](http://www.caen.it).

**MADE IN ITALY:** We remark that all our boards have been designed and assembled in Italy. In a challenging environment where a competitive edge is often obtained at the cost of lower wages and declining working conditions, we proudly acknowledge that all those who participated in the production and distribution process of our devices were reasonably paid and worked in a safe environment (this is true for the boards marked "MADE IN ITALY", while we cannot guarantee for third-party manufactures).

# Index

|                                                          |           |

|----------------------------------------------------------|-----------|

| <b>Purpose of this User Manual .....</b>                 | <b>2</b>  |

| <b>Change Document Record .....</b>                      | <b>2</b>  |

| <b>Symbols, abbreviated terms and notation .....</b>     | <b>2</b>  |

| <b>Reference Document .....</b>                          | <b>2</b>  |

| <b>Manufacturer contact .....</b>                        | <b>2</b>  |

| <b>Limitation of responsibility .....</b>                | <b>2</b>  |

| <b>Index .....</b>                                       | <b>4</b>  |

| <b>List of Figures .....</b>                             | <b>5</b>  |

| <b>List of Tables .....</b>                              | <b>6</b>  |

| <b>1 Introduction .....</b>                              | <b>7</b>  |

| <b>2 Safety Notices .....</b>                            | <b>8</b>  |

| <b>3 Block Diagram .....</b>                             | <b>10</b> |

| <b>4 Technical Specifications .....</b>                  | <b>11</b> |

| <b>5 Packaging and compliancy .....</b>                  | <b>12</b> |

| <b>6 PID (Product Identifier) .....</b>                  | <b>14</b> |

| <b>7 Power Requirements .....</b>                        | <b>15</b> |

| <b>8 Cooling Management .....</b>                        | <b>16</b> |

| <b>9 Installing the device .....</b>                     | <b>17</b> |

| <b>10 Hardware Description .....</b>                     | <b>18</b> |

| <b>SiPM connection and biasing .....</b>                 | <b>18</b> |

| Pitch Adapter Kit .....                                  | 20        |

| Connecting a matrix in negative-bias configuration ..... | 22        |

| <b>Temperature Feedback .....</b>                        | <b>23</b> |

| <b>Test Pins .....</b>                                   | <b>24</b> |

| <b>Motherboard I/Os .....</b>                            | <b>25</b> |

| <b>11 Functional Description .....</b>                   | <b>27</b> |

| <b>ASIC Trigger Operation .....</b>                      | <b>27</b> |

| <b>External Trigger .....</b>                            | <b>28</b> |

| <b>Charge Measurements .....</b>                         | <b>28</b> |

| <b>Time Measurements .....</b>                           | <b>29</b> |

| <b>Readout Modes .....</b>                               | <b>31</b> |

| Photon Counting .....                                    | 31        |

| Analog Multiplexed Readout .....                         | 32        |

| Fully Digital Readout .....                              | 33        |

| <b>Default trigger logic .....</b>                       | <b>34</b> |

| <b>ASICS configuration .....</b>                         | <b>34</b> |

| <b>12 Firmware and data format .....</b>                 | <b>35</b> |

| <b>13 DT5550W Readout Software .....</b>                 | <b>37</b> |

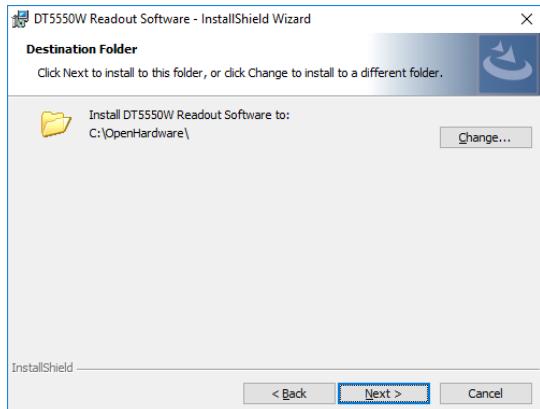

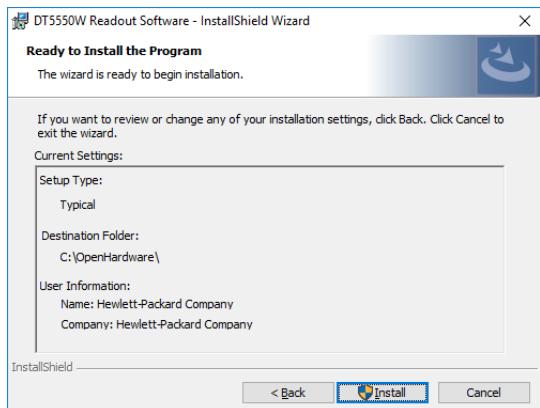

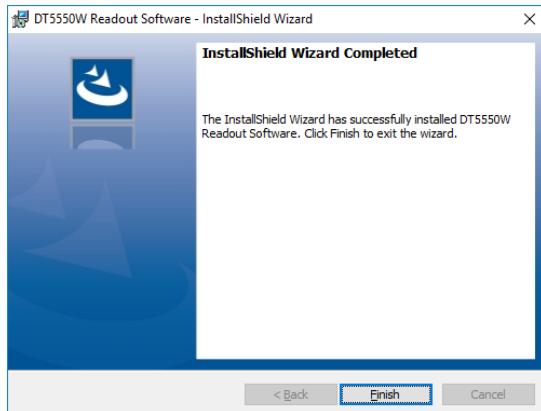

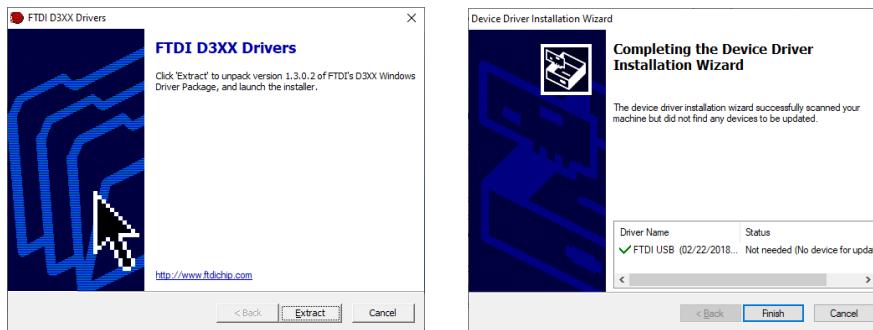

| <b>Software installation .....</b>                       | <b>37</b> |

| <b>Board Connection .....</b>                            | <b>39</b> |

| <b>Software GUI Description .....</b>                    | <b>40</b> |

| Menu and Control Toolbar .....                           | 40        |

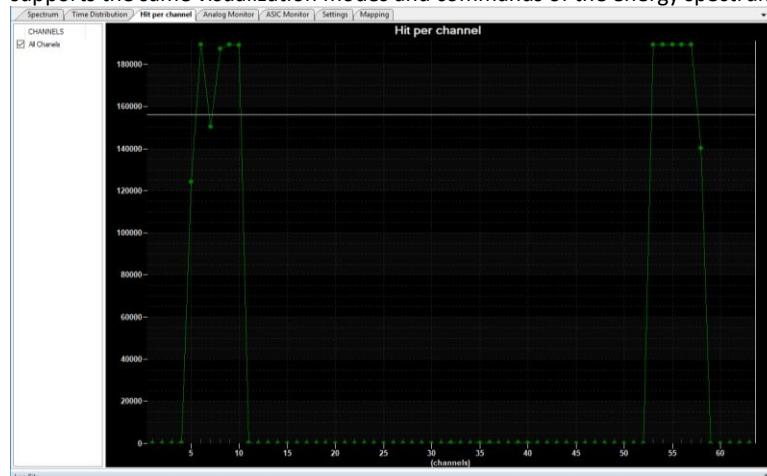

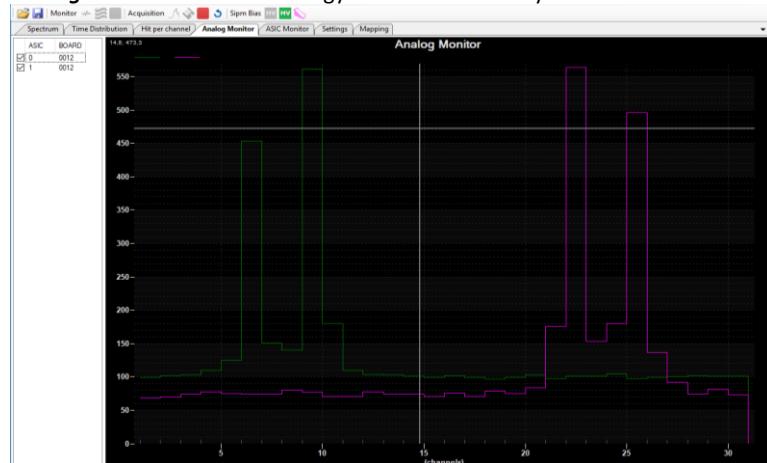

| Main plots .....                                         | 41        |

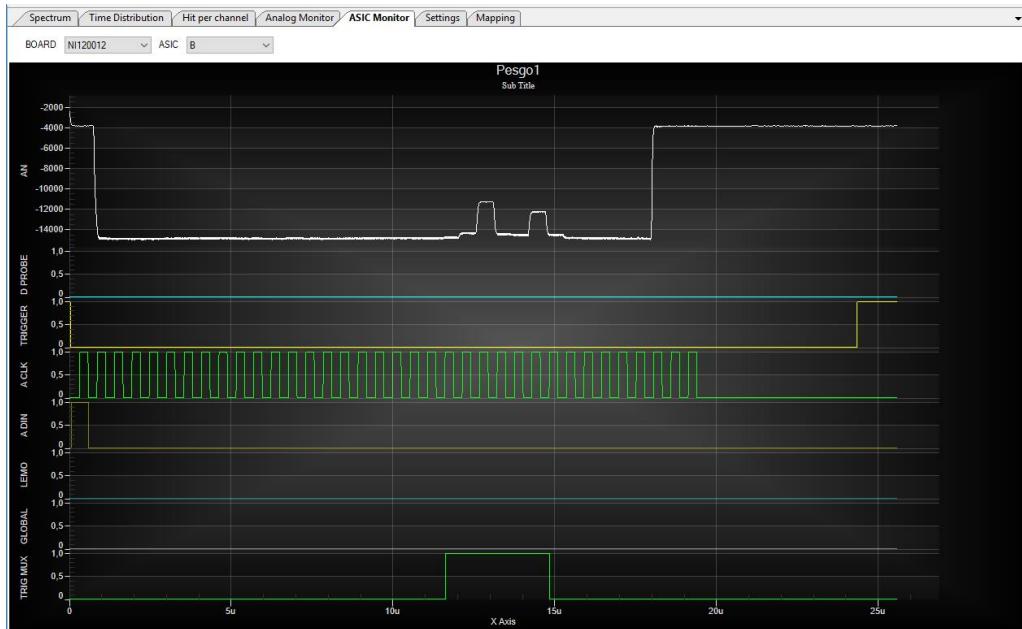

| The ASIC Monitor Tab .....                               | 43        |

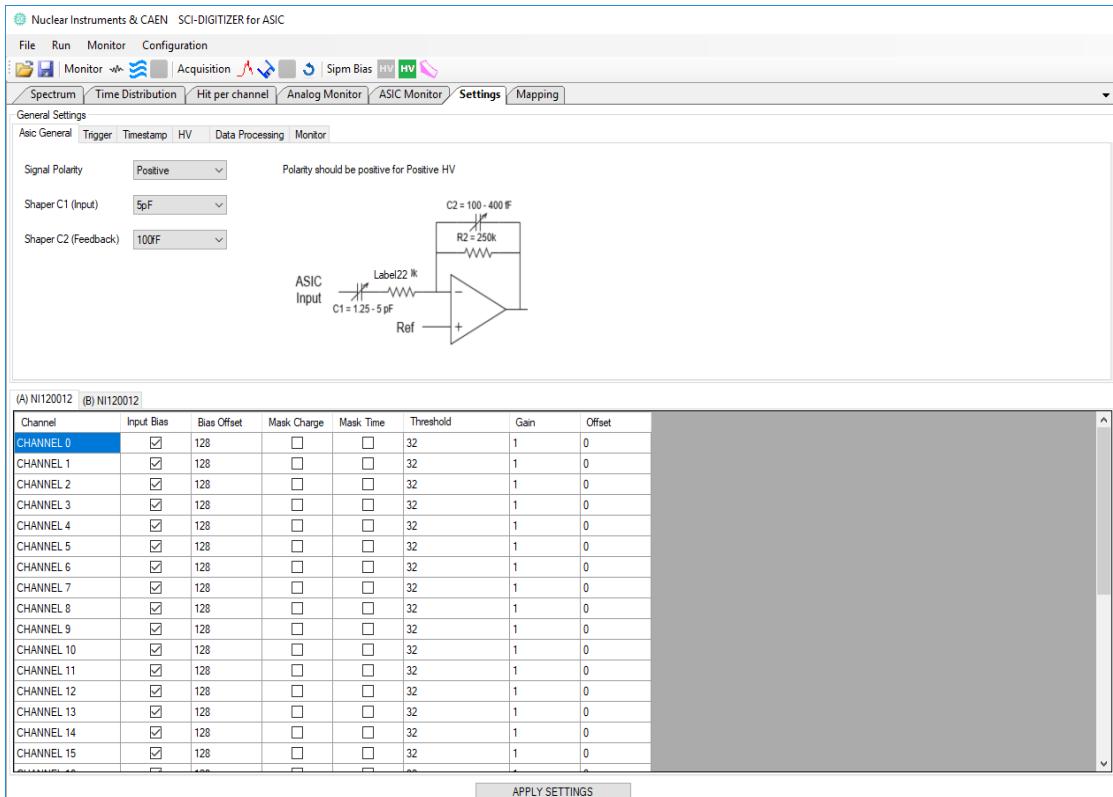

| The Settings Tab .....                                   | 43        |

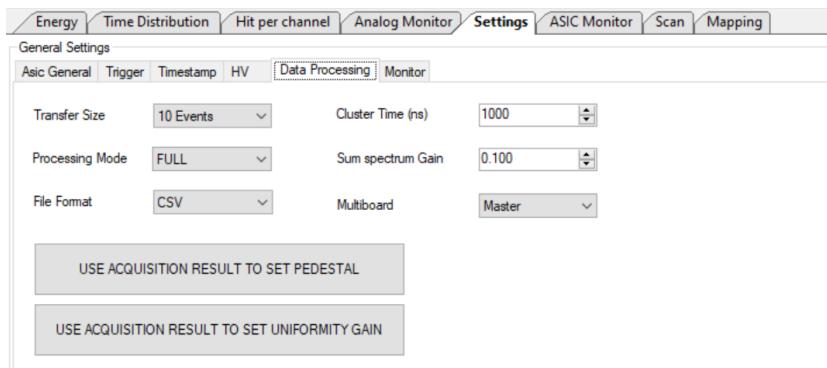

| Data Processing .....                                    | 47        |

| Channel specific settings .....                          | 48        |

|                                                                         |           |

|-------------------------------------------------------------------------|-----------|

| <b>How to perform an acquisition .....</b>                              | <b>49</b> |

| <b>Data Saving Format .....</b>                                         | <b>49</b> |

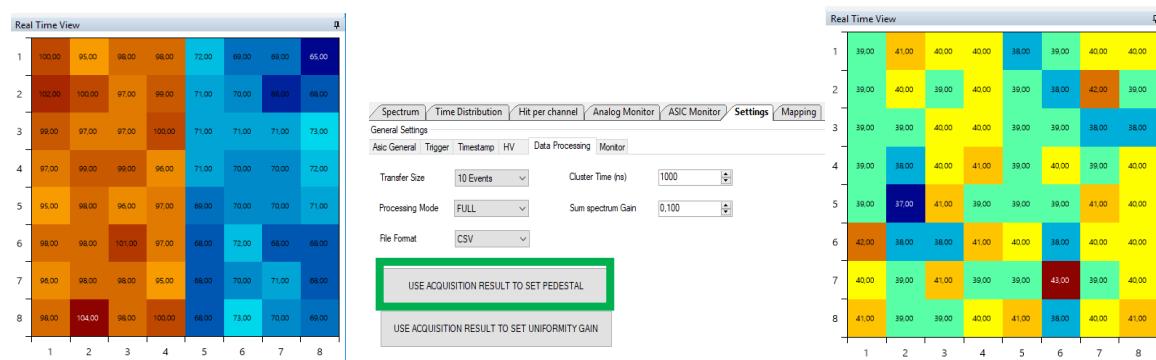

| <b>How to perform pedestal calculation .....</b>                        | <b>51</b> |

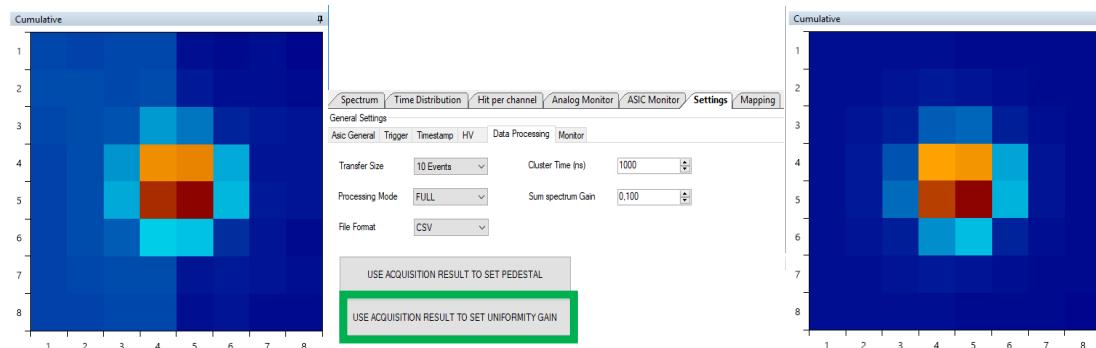

| <b>How to set uniformity gain .....</b>                                 | <b>52</b> |

| <b>14 Appendix .....</b>                                                | <b>53</b> |

| <b>C function to decode binary data coming from A55PETx board .....</b> | <b>53</b> |

| <b>Multiboard readout script .....</b>                                  | <b>55</b> |

| Configuration File .....                                                | 57        |

| Command line parameters .....                                           | 61        |

| Data Format.....                                                        | 61        |

| <b>15 Technical Support.....</b>                                        | <b>62</b> |

## List of Figures

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

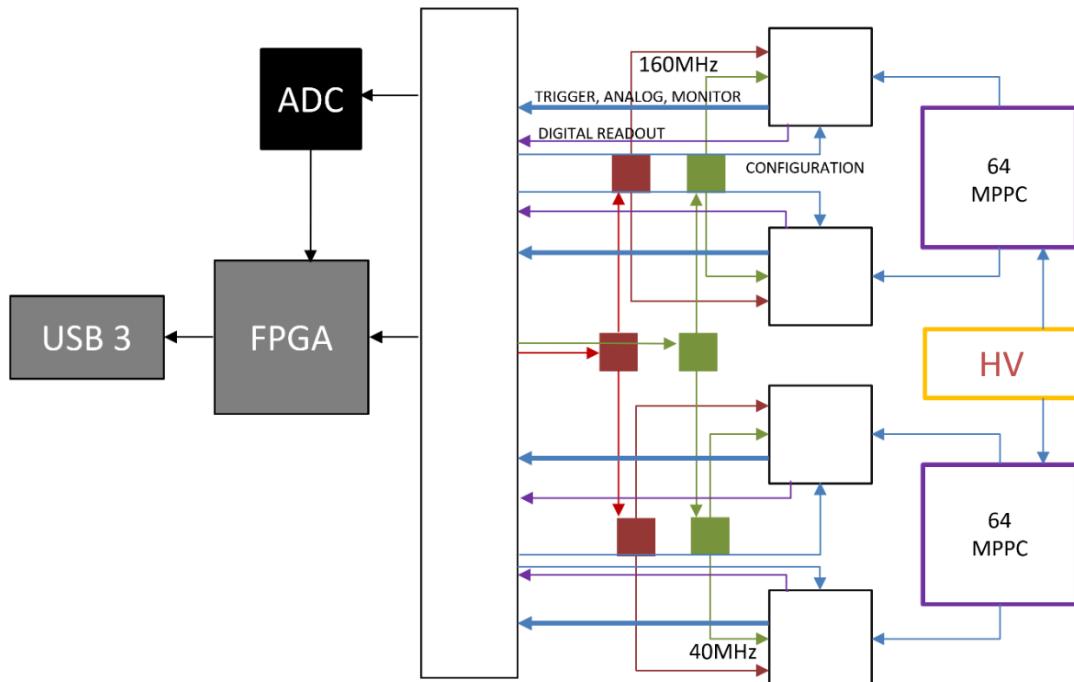

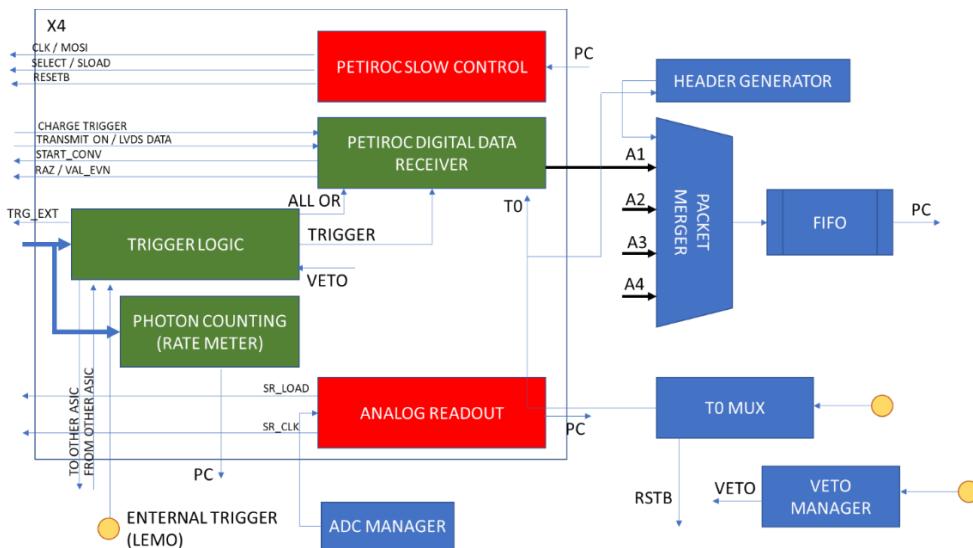

| Figure 3.1: A55PET4 Piggyback Board block diagram with A7585D High Voltage Power Supply for SiPM. On the left, the connections to the DT5550W motherboard components, through the mezzanine connector (big white rectangle), are shown.....                                                                                                                                                                                                                                                                        | 10 |

| Figure 5.1: general view of the DT5550W system, where the piggyback is the upper board.....                                                                                                                                                                                                                                                                                                                                                                                                                        | 12 |

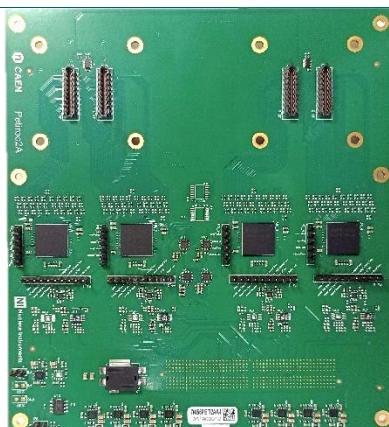

| Figure 10.1: general view (left front side, right: rear side) of the A55PET4 piggyback, shown as example.....                                                                                                                                                                                                                                                                                                                                                                                                      | 18 |

| Figure 10.2: the Hamamatsu S13361-3050AE-08 connected onboard. The grid reports the association between the matrix pixels (A-1 .... H-8) and the ASIC channels (ch0 ... ch31). The green-coloured pixels are connected to ASIC A while yellow-coloured pixels are connected to ASIC B .....                                                                                                                                                                                                                        | 19 |

| Figure 10.3: SiPM connection scheme to the ASIC input lines in standard configuration. N.M. means Not Mounted component.....                                                                                                                                                                                                                                                                                                                                                                                       | 20 |

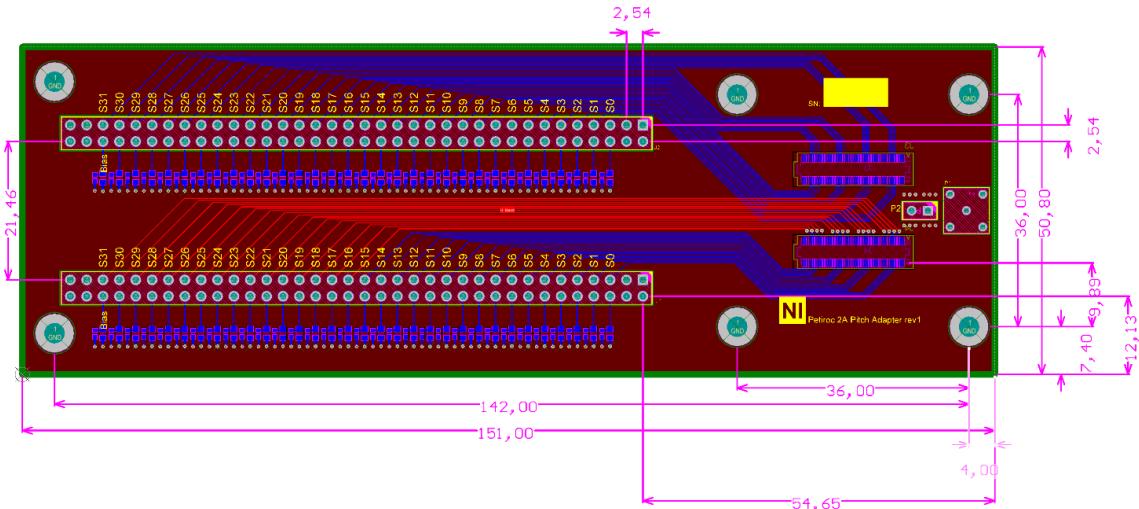

| Figure 10.4: view of the 64-ch pitch adapters. The strip connectors (each for 32 channels), the External HV LEMO and the P2 jumper are clearly visible. ....                                                                                                                                                                                                                                                                                                                                                       | 21 |

| Figure 10.5: dimensions of the pitch adapter. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21 |

| Figure 10.6: SiPM connection scheme to the ASIC and biasing lines when using the pitch adapter kit.....                                                                                                                                                                                                                                                                                                                                                                                                            | 22 |

| Figure 10.7: Top: how to plug the pitch adapter on the board's SiPM connector. The connectors are pressure-pluggable. Bottom: general view of a DT5550W with A55PET4 piggyback and two pitch adapters plugged in. In this configuration, all 128 channels of the DT5550W board are exposed on the strip connectors.....                                                                                                                                                                                            | 22 |

| Figure 10.8: typical connection of a cells of a SiPM matrix with common cathode using negative bias .....                                                                                                                                                                                                                                                                                                                                                                                                          | 23 |

| Figure 10.9: connections of the SiPM to the ASIC input stage, to obtain AC coupling with negative bias voltage. All <i>series components</i> (by default $0\ \Omega$ resistance) must be dismounted and replaced with a $10\ nF$ capacitance. The <i>component to ground</i> can be left not mounted. The hardware components for each input channels, are shown on the right.....                                                                                                                                 | 23 |

| Figure 10.10: the user I2C interface on the motherboard, to be used for external temperature sensor connection. ....                                                                                                                                                                                                                                                                                                                                                                                               | 24 |

| Figure 10.11: the test pins for A55PETx piggyback boards. ....                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24 |

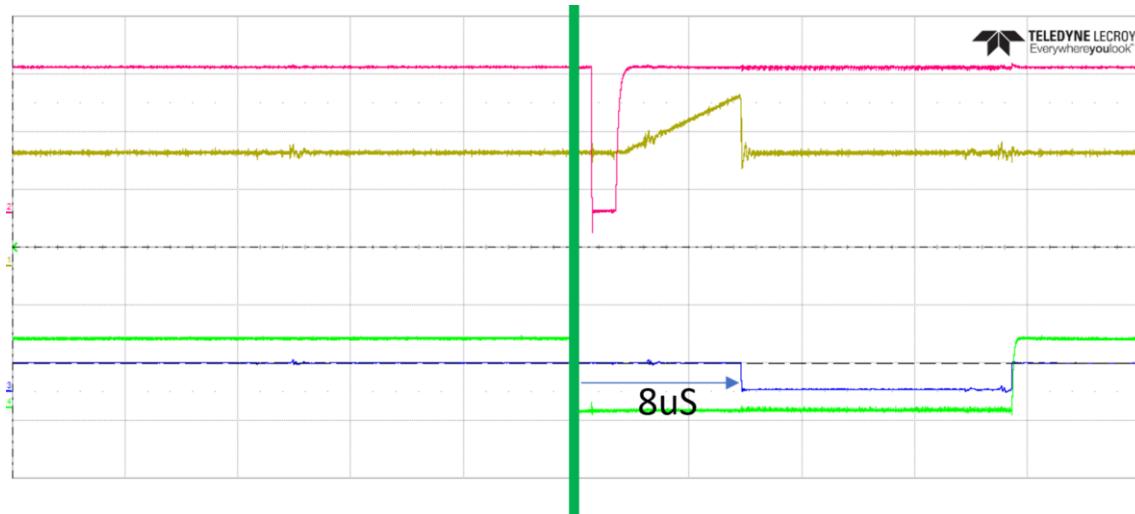

| Figure 10.12: a typical debugging acquisition made at the oscilloscope using test pins. Yellow: the ADC ramp. Magenta: the NOR32 charge trigger. Blue: the Transmit_on signal. Green: The NOR32 time trigger. The charge trigger starts the ADC ramp. When the digital conversion is finished, the ADC ramp falls and the transmit_on signal is set and the ASIC begins to transfer digital data to the FPGA. This happens $8\ \mu s$ after the time trigger, which must be considered as the conversion time..... | 25 |

| Figure 10.13: the programmable LEMO digital I/Os of the DT5550W .....                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26 |

| Figure 11.1: scheme of the PETIROC 2A ASIC.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27 |

| Figure 11.2: the PETIROC 2A trigger scheme .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28 |

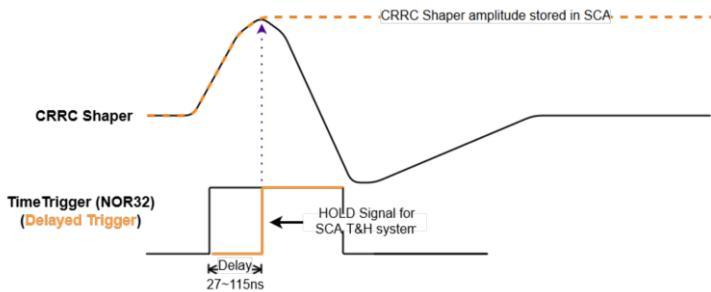

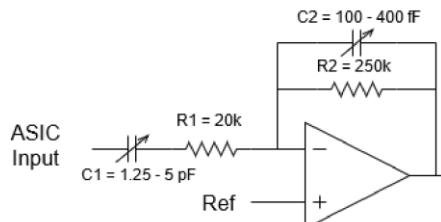

| Figure 11.3: the charge measurement mechanism in PETIROC ASIC.....                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29 |

| Figure 11.4: the RC-CR shaper with adjustable capacitance to change the shape of the output signal. ....                                                                                                                                                                                                                                                                                                                                                                                                           | 29 |

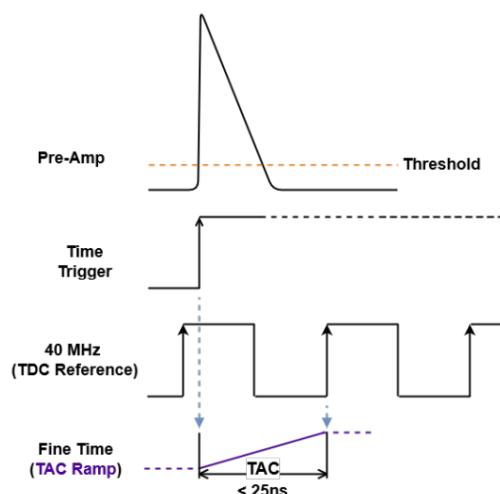

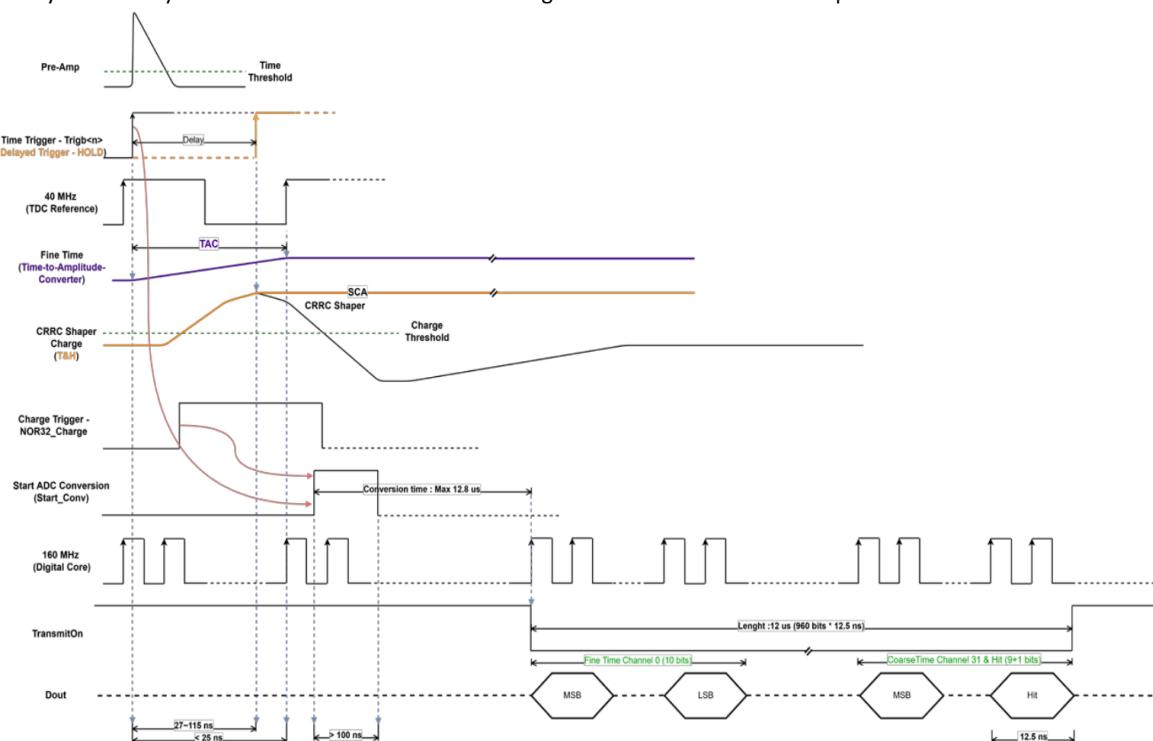

| Figure 11.5: time measurements scheme for PETIROC 2A, using the internal TDC. ....                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30 |

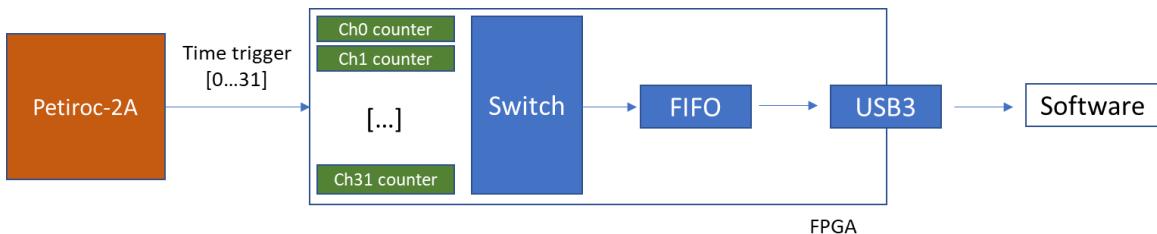

| Figure 11.6: readout scheme of DT5550W and ASIC operating in photon counting mode. ....                                                                                                                                                                                                                                                                                                                                                                                                                            | 32 |

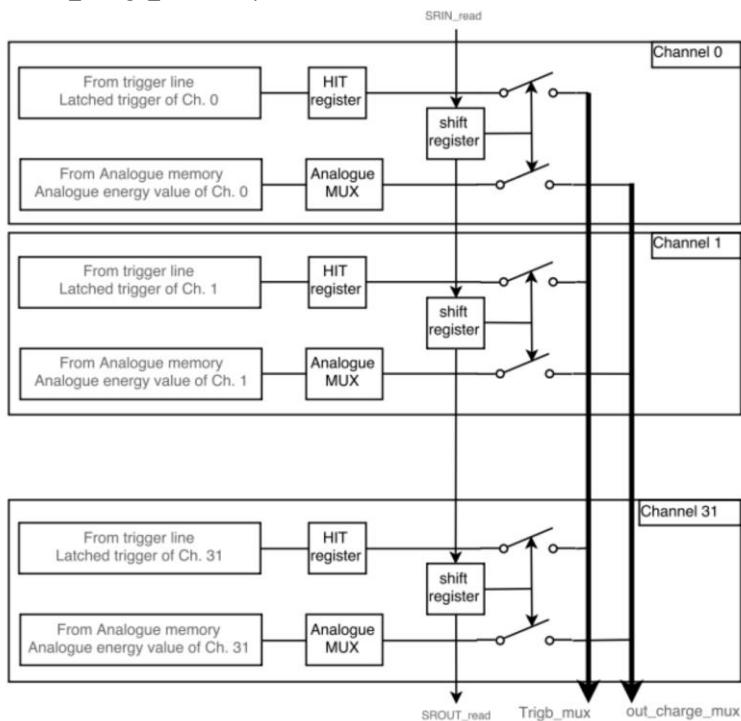

| Figure 11.7: the analog readout scheme of PETIROC 2A, where analog multiplexed data are available as outputs.....                                                                                                                                                                                                                                                                                                                                                                                                  | 32 |

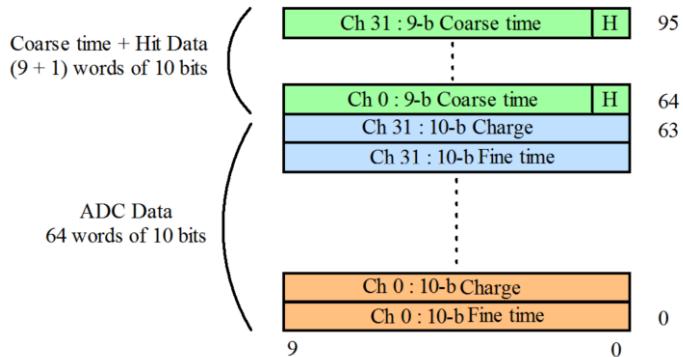

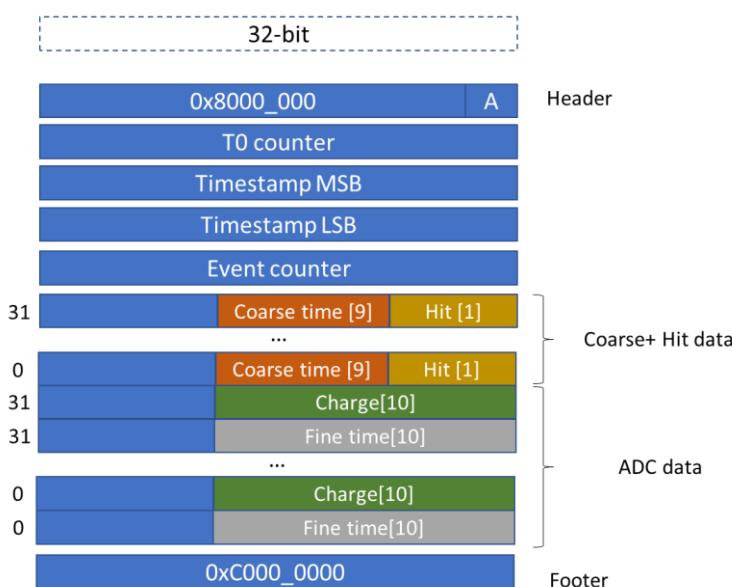

| Figure 11.8: structure of the data packets transferred during digital readout .....                                                                                                                                                                                                                                                                                                                                                                                                                                | 33 |

| Figure 11.9: the digital readout scheme of PETIROC 2A, where data serialization process is shown. ....                                                                                                                                                                                                                                                                                                                                                                                                             | 33 |

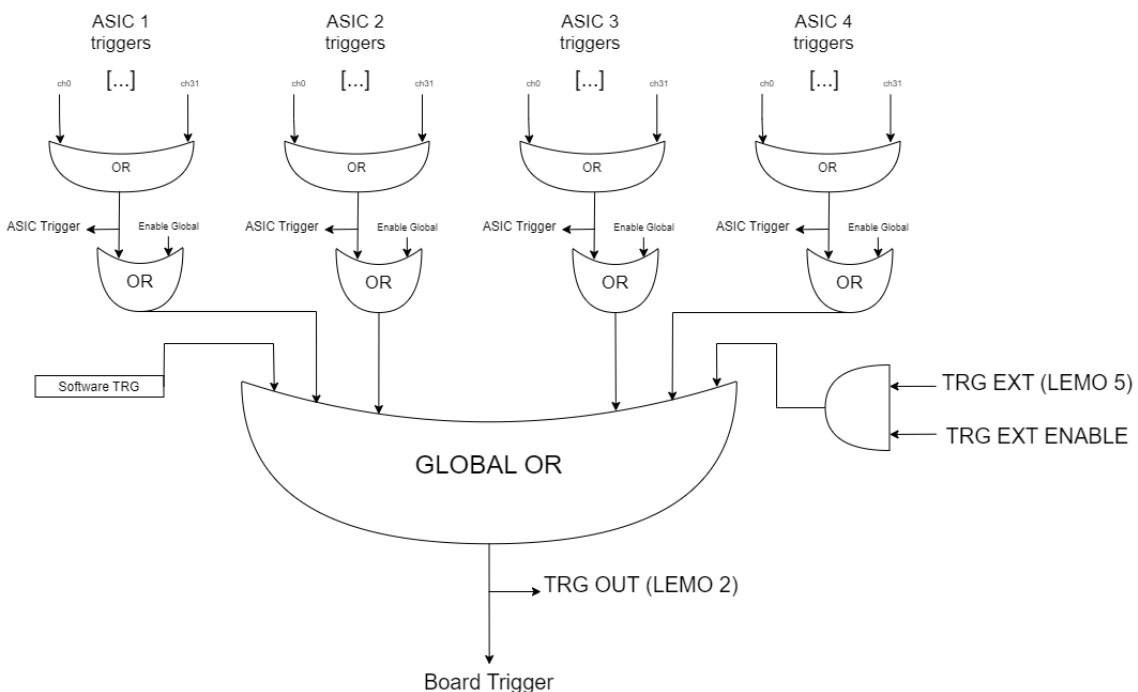

| Figure 11.10: scheme of the triggering logic set in the default firmware loaded on DT5550W for A55PETx management. 34                                                                                                                                                                                                                                                                                                                                                                                              |    |

| Figure 12.1: scheme of the default firmware loaded on DT5550W for A55PETx management. Refer to PETIROC 2A datasheet [RD1] for the meaning of each line of the ASIC involved in the block diagram.....                                                                                                                                                                                                                                                                                                              | 35 |

| Figure 12.2: structure of the data packet sent to the PC using the default firmware.....                                                                                                                                                                                                                                                                                                                                                                                                                           | 35 |

|                                                                                                                                                                                                                                                                                                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

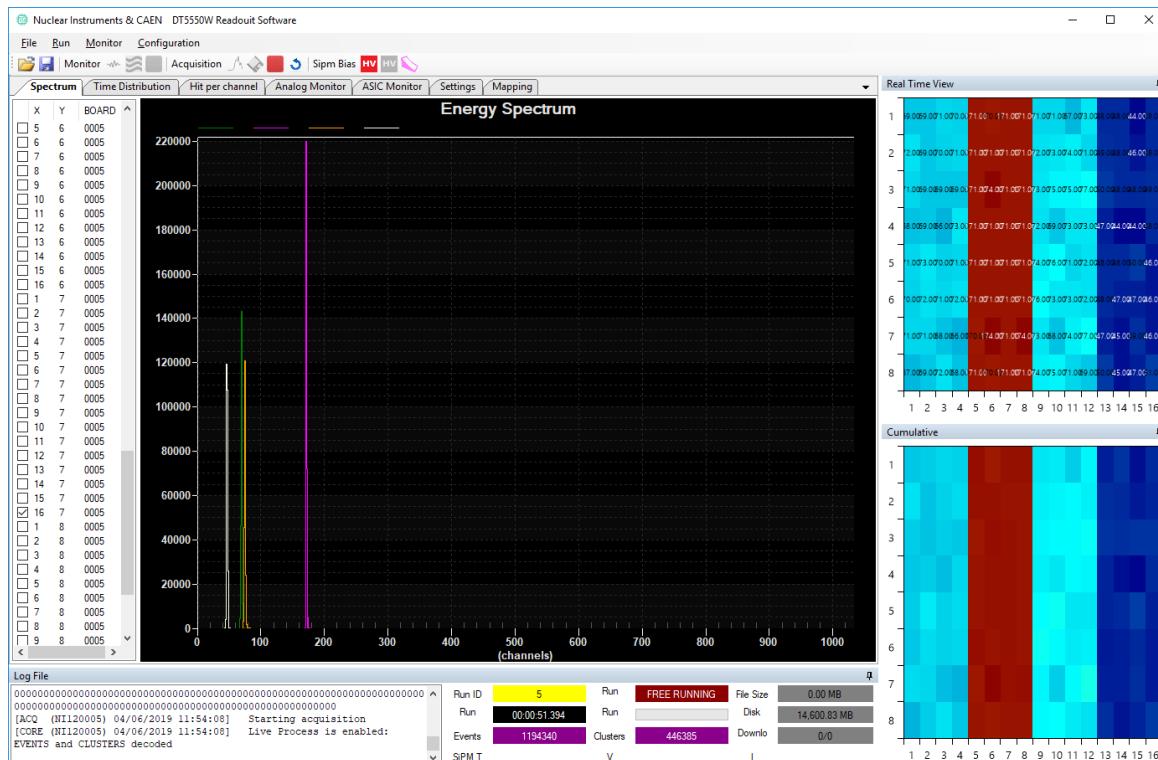

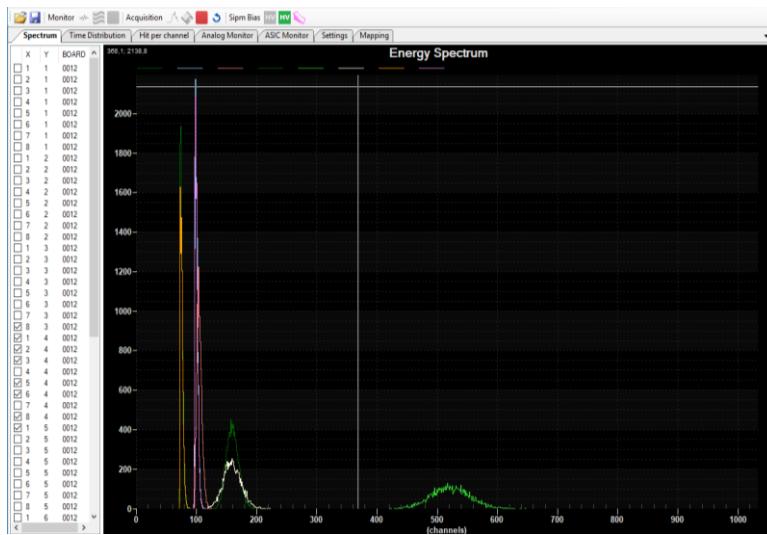

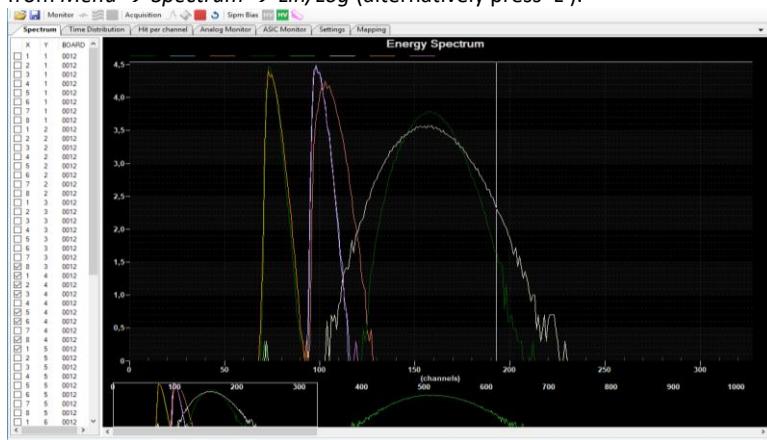

| Figure 13.1: general view of the DT5550W Readout Software. In this example, a pedestal acquisition is being performed with A55PET4 board, using two 64-channel SiPM matrix. ....                                                                                                                 | 37 |

| Figure 13.2: the "Connection" window at start-up of the DT5550W Readout Software .....                                                                                                                                                                                                           | 40 |

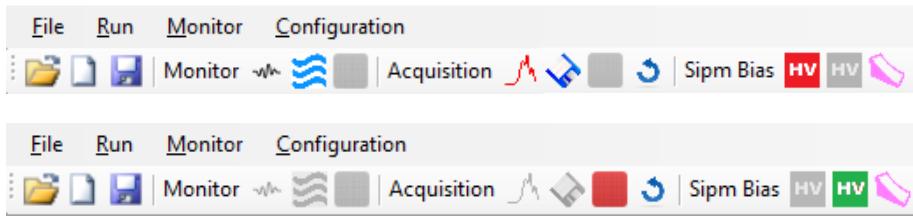

| Figure 13.3: the Menu and Control Toolbar of the DT5550W Readout Software, before (top) and during (bottom) acquisition. ....                                                                                                                                                                    | 40 |

| Figure 13.4: the ASIC Monitor Tab for A55PETx Piggyback. The white plot shows the charge multiplexed output. ....                                                                                                                                                                                | 43 |

| Figure 13.5: the <i>Settings</i> tab for A55PETx piggyback. The top and bottom area are clearly visible. The top area has different tabs for general configuration and the bottom area has a tab for each ASIC. ....                                                                             | 44 |

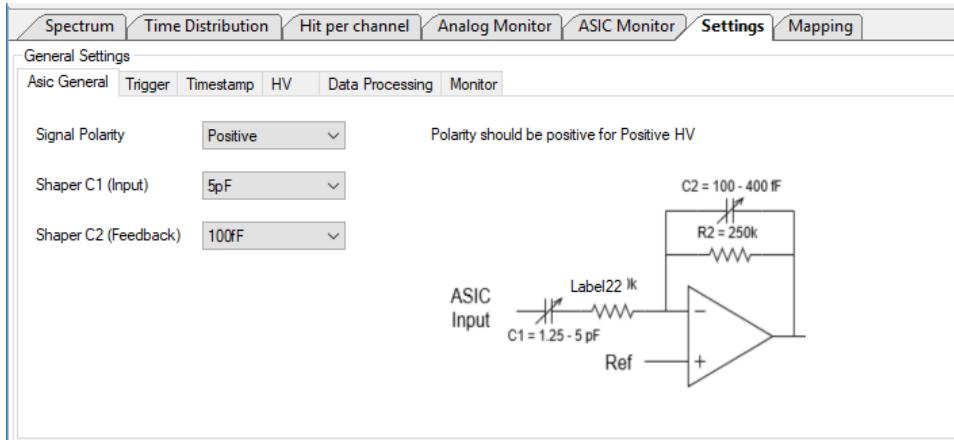

| Figure 13.6: the <i>Asic General</i> subtab of the <i>Settings</i> tab. ....                                                                                                                                                                                                                     | 45 |

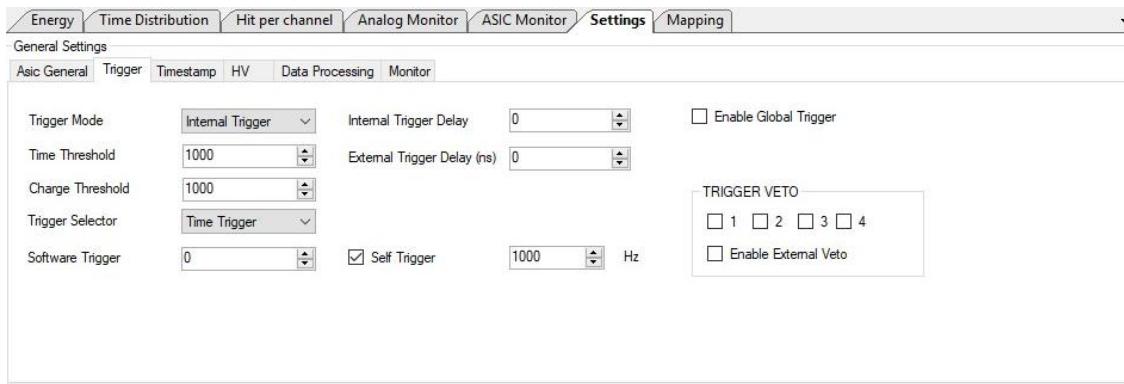

| Figure 13.7: the <i>Trigger</i> subtab of the <i>Settings</i> tab. ....                                                                                                                                                                                                                          | 45 |

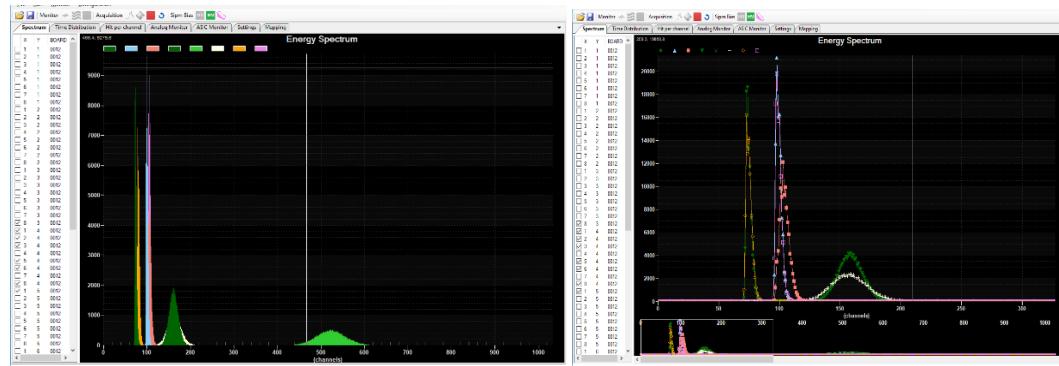

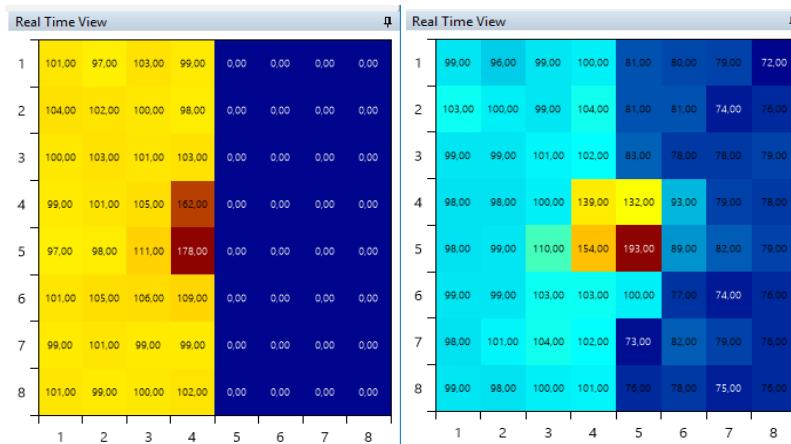

| Figure 13.8: the effect of the global trigger on imaging acquisition. On the left, with the global trigger disabled and a more intense light on ASIC A, this latter is triggering while ASIC B is not triggering. On the right, the global trigger is enabled and both ASICs are acquiring. .... | 46 |

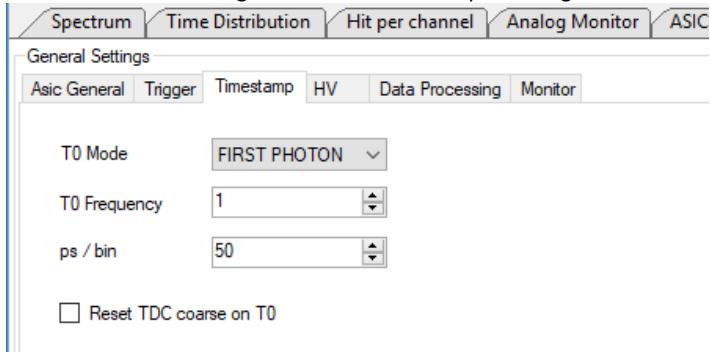

| Figure 13.9: the <i>Timestamp</i> subtab of the <i>Settings</i> tab. ....                                                                                                                                                                                                                        | 46 |

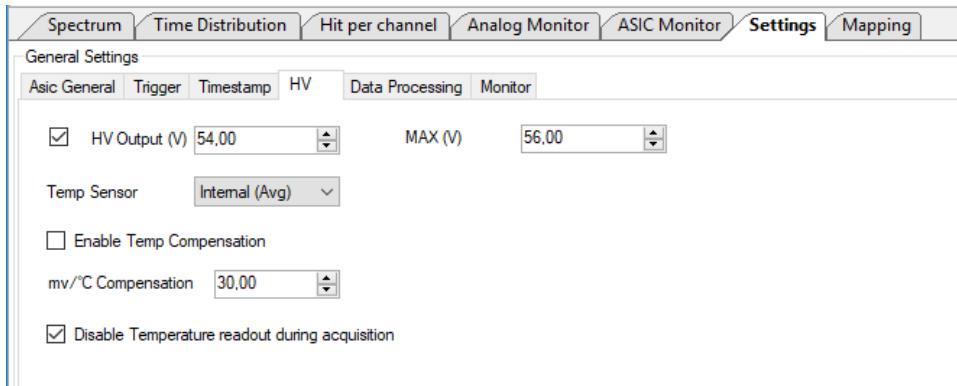

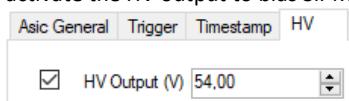

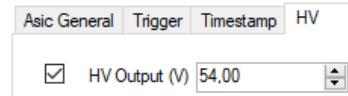

| Figure 13.10: the <i>HV</i> subtab of the <i>Settings</i> tab. ....                                                                                                                                                                                                                              | 47 |

| Figure 13.11: the <i>Data Processing</i> subtab of the <i>Settings</i> tab. ....                                                                                                                                                                                                                 | 47 |

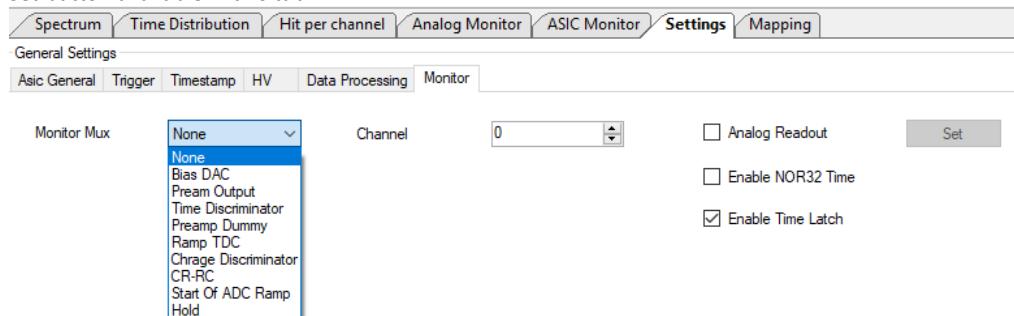

| Figure 13.12: the <i>Monitor</i> subtab of the <i>Settings</i> tab. ....                                                                                                                                                                                                                         | 48 |

| Figure 13.13: the bottom area of the <i>Settings</i> tab, containing the table for ASIC channels specific settings. In this case two ASICs (called A and B) are hosted on the board (NI120012). ....                                                                                             | 48 |

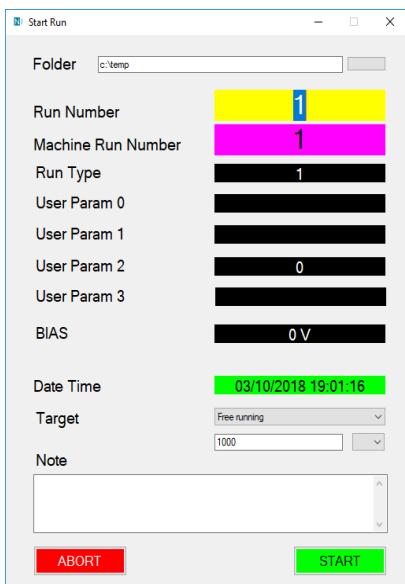

| Figure 13.14: the <i>Start Run</i> window which opens after the acquisition with data saving is started. ....                                                                                                                                                                                    | 49 |

| Figure 13.15: data saved in binary format for A55PETx board .....                                                                                                                                                                                                                                | 50 |

| Figure 13.16: an image of a 64-channel SiPM matrix acquired before (left) and after (right) the pedestal calculation. ....                                                                                                                                                                       | 52 |

| Figure 13.17: the results of pedestal calculation and gain regulation. The image on the right (after compensation of offset and gain) has a more uniform background (deep blue pixels) and small energy differences in neighbouring pixels with respect to the image on the left. ....           | 52 |

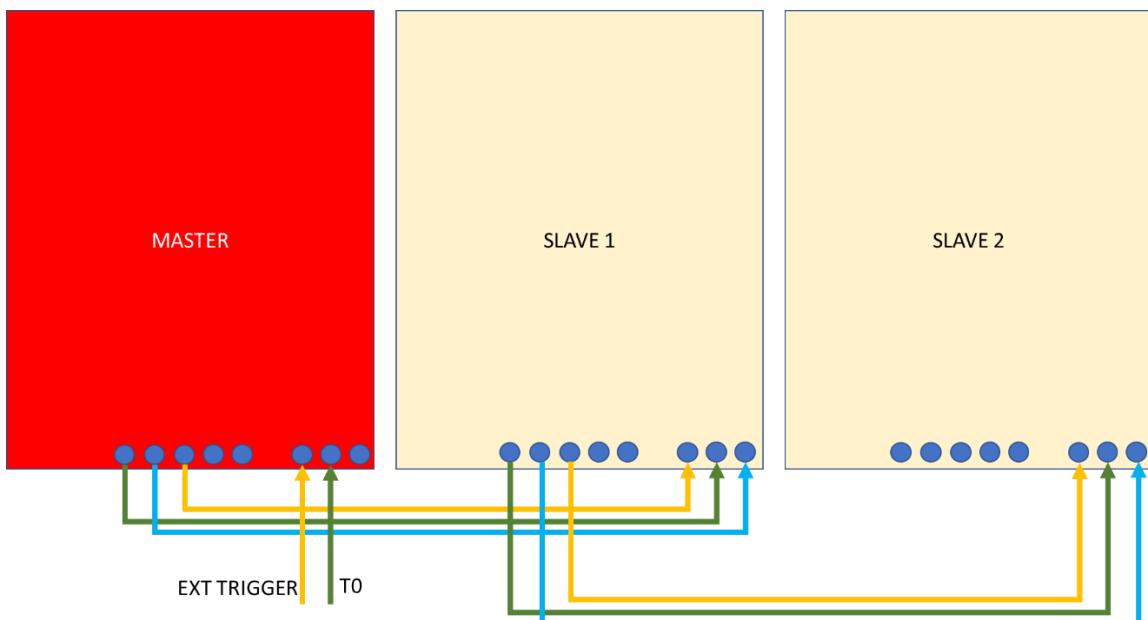

| Figure 14.1: connection of multiple DT5550W+A55PETx boards. The yellow, green and cyan lines are distributing trigger, timing reference and run signal respectively. ....                                                                                                                        | 55 |

## List of Tables

|                                                                                                                  |    |

|------------------------------------------------------------------------------------------------------------------|----|

| Table 1.1: table of available board models and accessories .....                                                 | 7  |

| Table 2.1: operating limits for A55PETx mezzanine connector.....                                                 | 9  |

| Table 4.1: technical specifications of the A55PETx .....                                                         | 11 |

| Table 10.1: description of the main components and connectors of the A55PETx board .....                         | 18 |

| Table 10.2: description of the pitch adapter connectors.....                                                     | 21 |

| Table 10.3: A55PETx test pins description. ....                                                                  | 25 |

| Table 10.4: assignment of the programmable LEMO digital I/Os in the default firmware for A55PETx management..... | 26 |

| Table 13.1: saved data format in <i>Processing Mode</i> = DECODE EVENTS .....                                    | 50 |

| Table 13.2: saved data format in <i>Processing Mode</i> = FULL.....                                              | 51 |

# 1 Introduction

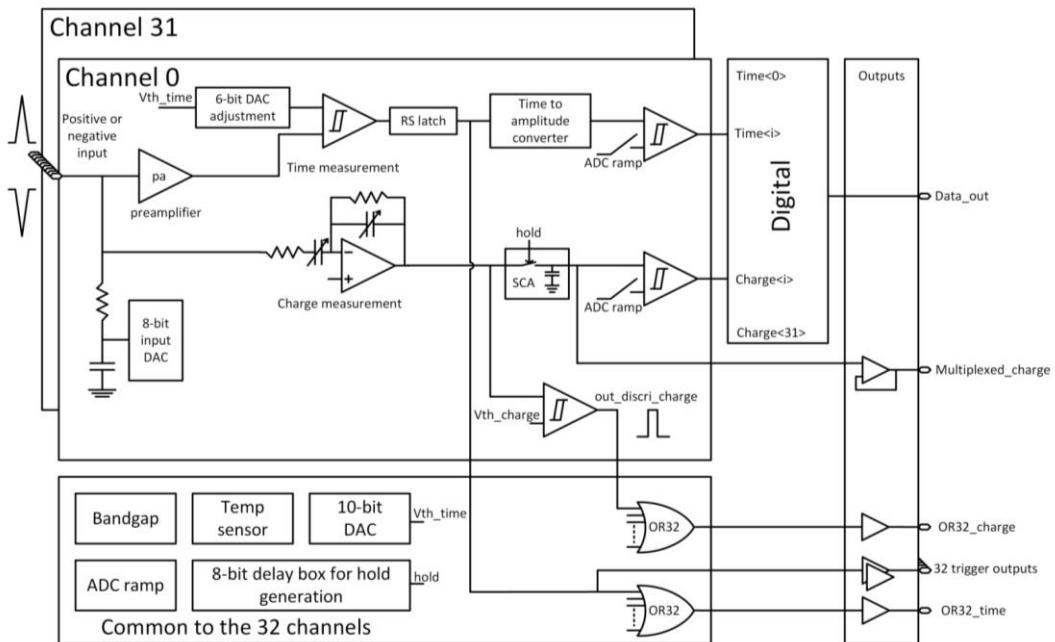

The A55PETx board is the Piggyback Board for DT5550W, hosting up to four PETIROC 2A WeeROC (\*) ASICs. It can be used in conjunction with DT5550W motherboard to perform **energy and high-resolution time measurements with SiPMs and SiPM matrixes**.

The device is designed to operate in laboratory environment under the supervision of skilled technicians.

The PETIROC 2A ASIC is the ideal solution for high density channel systems, aiming to readout SiPM sensors extracting energy, time and positional information. In fact, the PETIROC chip, besides the classical readout chain made of preamp, fast and slow shaper, it also integrates a trigger with a timing resolution better than 35 ps, a TDC, a Sample&Hold circuit and an internal ADC which can convert onboard the charge cumulated on each sensor. Each PETIROC 2A integrates 32 readout channels.

The A55PETx piggyback is equipped with CAEN module A7585D to be used for SiPM biasing. The A7585D power supply is directly soldered on the PCB.

The PETIROC 2A integrates in a chip an entire readout system, requiring externally only few passive components, two clock lines and a FPGA connected with few lines, which can manage up one hundred ASICs. Therefore, a system exploiting this chip is the best solution for experiments in which the high number of channels requires the reduction of the hardware components, because of geometrical reasons and costs.

The A55PETx Piggyback can be easily plugged onto the DT5550W motherboard to arrange a **complete Data Acquisition System for SiPM with up to 128 channels**. The PETIROCs readout is completely managed by the firmware preloaded on the FPGA hosted by the DT5550W motherboard.

The **DT5550W Readout Software** is the free and open source Windows-based software developed to perform acquisitions with the DT5550W. It works in conjunction with the DT5550W default firmware and it can be modified by the user according to the custom functions implemented in the firmware and for any other need. It allows to perform:

- List event readout (energy, time)

- Energy Spectrum measurements

- Time spectrum measurements

- Imaging with configurable detector shape

- System and ASIC configuration

- ASIC monitor signal probing

For more detailed information, see **[RD2]**.

Available board models and accessories are listed below.

| Motherboard            | Description                                      | Product Code |

|------------------------|--------------------------------------------------|--------------|

| DT5550W                | DT5550W - WeeROC ASICs Evaluation and DAQ System | WDT5550WXAAA |

| Piggyback Board Models | Description                                      | Product Code |

| A55PET1                | A55PET1 - Piggyback Board with 1 PETIROC chip    | WW55PET12AA1 |

| A55PET2                | A55PET2 - Piggyback Board with 2 PETIROC chip    | WW55PET12AA2 |

| A55PET4                | A55PET4 - Piggyback Board with 4 PETIROC chip    | WW55PET12AA4 |

| Accessories            | Description                                      | Product Code |

| REMOT5550W             | Remotization kit with 2-meters cable for DT5550W | WKREMOT5550W |

**Table 1.1:** table of available board models and accessories

(\*) <https://www.weeroc.com>

## 2 Safety Notices

**N.B. Read carefully the “Precautions for Handling, Storage and Installation” document provided with the product before starting any operation.**

The following HAZARD SYMBOLS may be reported on the unit:

|                                                                                     |                                   |

|-------------------------------------------------------------------------------------|-----------------------------------|

|    | Caution, refer to product manual  |

|    | Caution, risk of electrical shock |

|    | Protective conductor terminal     |

|   | Earth (Ground) Terminal           |

|  | Alternating Current               |

|  | Three-Phase Alternating Current   |

The following symbol may be reported in the present manual:

|                                                                                     |                           |

|-------------------------------------------------------------------------------------|---------------------------|

|  | General warning statement |

|-------------------------------------------------------------------------------------|---------------------------|

The symbol could be followed by the following terms:

- **DANGER:** indicates a hazardous situation which, if not avoided, will result in serious injury or death.

- **WARNING:** indicates a hazardous situation which, if not avoided, could result in death or serious injury.

- **CAUTION:** indicates a situation or condition that, if not avoided, could cause physical injury or damage the product and / or its environment.

To avoid potential hazards, use the product only as specified. Only qualified personnel should perform service procedures.

**Avoid Electric Overload.** To avoid electric shock or fire hazard, do not power a load outside of its specified range.

**Avoid Electric Shock.** To avoid injury or loss of life, do not connect or disconnect cables while they are connected to a voltage source.

**Do Not Operate without Covers.** To avoid electric shock or fire hazard, do not operate this product with covers or panels removed.

**Do Not Operate in Wet/Damp Conditions.** To avoid electric shock, do not operate this product in wet or damp conditions.

**Do Not Operate in an Explosive Atmosphere.** To avoid injury or fire hazard, do not operate this product in an explosive atmosphere.

**Do Not Operate with Suspected Failures.** If you suspect this product to be damaged, please contact Technical Support.

The mezzanine connector carries more than 250 I/O lines that can be grouped as:

- Digital 3.3V single ended I/O

- Digital 2.5V single ended I/O

- Digital differential 2.5V LVDS

- Analog differential Input

- Analog Common Mode Output

- I2C

- Power Supply

- Clock output

The following operating limits must be respected:

| Net class     | Connector           | Unit                      | Min                    | Max    |

|---------------|---------------------|---------------------------|------------------------|--------|

| Digital lines | Mezzanine connector |                           |                        |        |

|               |                     | Digital 3.3V              | Voltage                | 0 V    |

|               |                     |                           | Current                | 10 mA  |

|               |                     | Digital 2.5V              | Voltage                | 0 V    |

|               |                     |                           | Current                | 10 mA  |

|               |                     | LVDS                      | Voltage                | 0.5 V  |

|               |                     |                           | Current                | 10 mA  |

|               |                     |                           | Common Mode            | 1.25 V |

|               |                     | I2C                       | Voltage                | 0      |

|               |                     |                           | Voltage                | 3.5 V  |

|               |                     | Analog Differential Input | Common Mode            | 0.45 V |

|               |                     |                           | Voltage                | 1.55 V |

|               |                     | Analog Common Mode Output | Current                | 0.95 V |

|               |                     | Power 5V                  | Current                | 6 mA   |

|               |                     | Power 3.3V                | Current                | 2 A    |

|               |                     | Power 1.8V                | Current                | 2 A    |

|               |                     | Power 4V A                | Current                | 1 A    |

|               |                     | Power -1V A               | Current                | 600 mA |

|               |                     | Clock Output              | Differential Impedance | 600 mA |

|               |                     |                           | 80 Ω                   | 120 Ω  |

Table 2.1: operating limits for A55PETx mezzanine connector.

**WARNING:** the piggyback connector lines are directly connected to the FPGA I/O. Violation in maximum absolute rating given in this document will likely destroy the FPGA.

**THIS DEVICE SHOULD BE INSTALLED AND USED BY SKILLED TECHNICIAN

ONLY OR UNDER HIS SUPERVISION**

### 3 Block Diagram

**Figure 3.1:** A55PET4 Piggyback Board block diagram with A7585D High Voltage Power Supply for SiPM. On the left, the connections to the DT5550W motherboard components, through the mezzanine connector (big white rectangle), are shown.

# 4 Technical Specifications

| TECHNICAL                        |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>POWER CONSUMPTION</b>         | DT5550W + A55PET4 piggyback - 0.9A @ 12V (Typ.)                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>ANALOG INPUT</b>              | <b>Channels</b><br>32, 64 or 128 (=1, 2 or 4 Petiroc-2A) <b>Connector</b><br>Compatible with 64-channel Hamamatsu matrix<br>S13361-3050AE-08<br><br><b>INCLUDED strip adapter with 2.54 mm pitch</b>                                                                                                                                                                                                                                      |

| <b>SIGNAL POLARITY</b>           | Positive or Negative                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>SENSITIVITY</b>               | High bandwidth (GBW>1GHz) inverting voltage preamplifier with fixed gain (=40)                                                                                                                                                                                                                                                                                                                                                            |

| <b>DYNAMIC RANGE</b>             | The Petiroc-2A preamplifiers ensure a dynamic range from 160 fC to 400 pC (i.e. from 1 to 2500 photo-electrons with $10^6$ SiPM gain)                                                                                                                                                                                                                                                                                                     |

| <b>SHAPING TIME</b>              | <b>CRRC</b><br>4 options from 25 ns to 100 ns (25 ns step) for each RC filter                                                                                                                                                                                                                                                                                                                                                             |

| <b>SELF-TRIGGERS</b>             | - Programmable 10-bit DAC for common threshold<br>- Separate trigger line per channel<br>- Programmable 6-bit DAC for channel-by-channel threshold fine adjustment<br>$V_{th} = 0.89V + (10\text{-bit DAC} * 0.92\text{ mV}) - (6\text{-bit DAC} * 1.5\text{mV})$<br><br>- Logic combination (AND, OR) of triggers for start of A/D conversion and time reference<br><b>Custom combinations</b> through open FPGA and <b>SCI-Compiler</b> |

| <b>EXTERNAL TRIGGER</b>          | From LEMO 5 of the DT5550W motherboard programmable I/Os                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>HIGH VOLTAGE POWER SUPPLY</b> | Single channel PCB mounted A7585D High Voltage Power Supply:<br>- Common SiPM bias voltage: 20 $\div$ 85 V<br>- Vset vs. Vout Accuracy: $\pm 0.2\% \pm 50\text{mV}$<br>- Individual channel adjustment: 8-bit (2.5V or 4.5V dynamic range)<br>- Max. output bias current: 10 mA<br>- Programmable temperature compensation                                                                                                                |

| <b>ACQUISITION MODE</b>          | <b>Digital Readout (PHA + timestamp)</b><br>- Simultaneous acquisition of all channels – energy and timestamp<br>- 10-bit A/D conversion<br><br>- Systematic conversion time + serial data outing $\sim 12.8 + 12\text{ }\mu\text{s} \rightarrow$ Max. trigger rate $\sim 40\text{ kHz}$                                                                                                                                                  |

| <b>TIME STAMP</b>                | Resolution below 40ps for fine timestamp                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>INTERCONNECTION</b>           | Mezzanine connector carrying more than 200 analog/digital lines, to connect the A55PETx onto the DT5550W motherboard                                                                                                                                                                                                                                                                                                                      |

| <b>SOFTWARE</b>                  | - <b>DT5550W Readout Software</b> to manage the default firmware<br>- <b>SCI-Compiler</b> for custom firmware development on the DT5550W motherboard                                                                                                                                                                                                                                                                                      |

| MECHANICAL                       |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>FORM FACTOR</b>               | Desktop bare PCB unit                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>DIMENSIONS (H/W/L)</b>        | Piggyback: 5/160/145 mm <sup>3</sup> (including connectors)<br>Piggyback mounted on DT5550W: 24/152/260 mm <sup>3</sup> (including connectors)                                                                                                                                                                                                                                                                                            |

| ENVIRONMENTAL                    |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>ENVIRONMENTAL</b>             | Indoor use                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>OPERATING TEMPERATURE</b>     | Operating Temperature -20 °C $\div$ 50 °C                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>OPERATING HUMIDITY</b>        | 25% $\div$ 95% RH non condensing                                                                                                                                                                                                                                                                                                                                                                                                          |

| <b>STORAGE TEMPERATURE</b>       | -30 °C $\div$ +80 °C                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>STORAGE HUMIDITY</b>          | 5% $\div$ 90% RH non condensing                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>ALTITUDE</b>                  | $\leq$ 2000 m                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>POLLUTION DEGREE</b>          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>OVERVOLTAGE CATEGORY</b>      | II                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>EMC ENVIRONMENT</b>           | Commercial and light industrial                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>IP DEGREE</b>                 | IPX0 enclosure, not for wet location                                                                                                                                                                                                                                                                                                                                                                                                      |

| REGULATORY                       |                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <b>COMPLIANCE</b>                | <ul style="list-style-type: none"> <li>• EMC: CE 2014/30/EU Electromagnetic compatibility Directive</li> <li>• Safety: CE 2014/35/EU Low Voltage Directive</li> </ul>                                                                                                                                                                                                                                                                     |

Table 4.1: technical specifications of the A55PETx

## 5 Packaging and compliancy

The A55PETx is a bare piggyback PCB – 5/160/145 mm<sup>3</sup> (including connectors) H/W/L – intended to be mounted on the DT5550W motherboard. The system is provided as OEM device without any enclosure in order to be easily integrated in the final experimental setup. If the A55PETx is purchased together with the DT5550W motherboard, the system is provided already assembled, as shown in **Figure 5.1**

**Figure 5.1:** general view of the DT5550W system, where the piggyback is the upper board.

The unit is inspected by CAEN before the shipment, and it is guaranteed to leave the factory free of mechanical or electrical defects.

When receiving the unit, the user is strictly recommended to inspect for any damage which may have occurred during transportation. Particularly, inspect for exterior damages like broken connectors and check that the panel is not scratched or cracked.

All packing material should be held on until the inspection has been completed. If damage is detected, the user must file a claim with the carrier immediately and notify CAEN.

Before installing the unit, make sure to read thoroughly the safety rules and installation requirements (Sec. **Safety Notices** and **Installing the device**), then place the package content onto your bench.

The content of the delivered package standardly consists of the part list shown in the table below (**Table 5.1**). All the official documentation, firmware updates, software tools, and accessories are available on [www.caen.it](http://www.caen.it) at the product web page.

| Part                                                                                | Description           | Qty                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | A55PETx piggyback     | Weeroc ASICs evaluation and DAQ system                                                                                                                                                                                       |

|  | Dark box              | 3D-printed dark box with connector for optical fiber, compatible with CAEN SP5601/SP5605 LED Driver kit. It can be used to operate the SiPMs in a light-tight environment and illuminate them with an external light source. |

|  | 2.54 mm pitch adapter | 2.54 mm pitch adapter to convert the Ultra Fine Pitch Socket for SiPM connection into a double 2.54 mm strip connector                                                                                                       |

|                                                                                   |            |                                                                                                                                   |    |

|-----------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------|----|

|  | Fixing kit | Nuts and bolts to secure the dark box or pitch adapter to the A55PETx – by default it is already mounted to secure the dark boxes |    |

|  | User guide | UM7028 – A55PETx User Manual                                                                                                      | x1 |

Table 5.1: delivered kit.

**CAUTION:** to manage the product, consult the operating instructions provided.

**A55PETx is an ESD sensitive item. Handling without ESD protective covering shall be performed only into approved ESD Protected Area (EPAs)**

**A55PETx complies with EMC directive only if installed in a CE marked system**

It is recommended to:

- Inspect containers for damage during shipment. Report any damage to the freight carrier for possible insurance claims.

- Check that all the components received match those listed on the enclosed packing list. (CAEN cannot accept responsibility for missing items unless we are notified promptly of any discrepancies.)

- Open shipping containers; be careful not to damage contents.

- Inspect contents and report any damage. The inspection should confirm that there is no exterior damage to the unit such as broken knobs or connectors and that the front panel and display face are not scratched or cracked. Keep all packing material until the inspection has been completed.

- If damage is detected, file a claim with carrier immediately and notify CAEN service.

- If equipment must be returned for any reason, carefully repack equipment in the original shipping container with original packing materials if possible. Please contact CAEN service.

- If equipment is to be installed later, place equipment in original shipping container and store in a safe place until ready to install

**DO NOT SUBJECT THE ITEM TO UNDUE SHOCK OR VIBRATIONS**

**DO NOT BUMP, DROP OR SLIDE SHIPPING CONTAINERS**

**DO NOT LEAVE ITEMS OR SHIPPING CONTAINERS UNSUPERVISED IN AREAS WHERE UNTRAINED PERSONNEL MAY MISHANDLE THE ITEMS**

**USE ONLY ACCESSORIES WHICH MEET THE MANUFACTURER SPECIFICATIONS**

## 6 PID (Product Identifier)

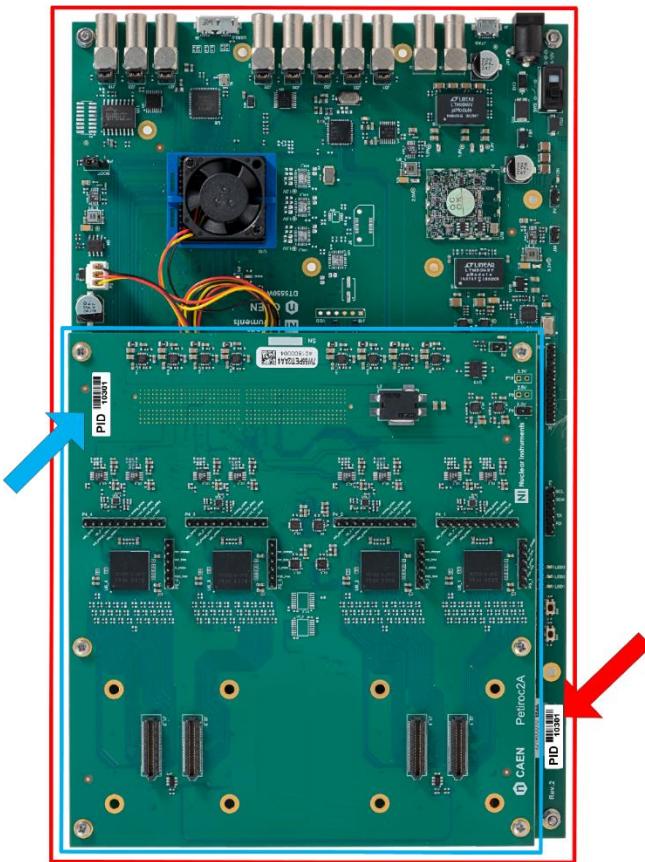

PID is the CAEN product identifier, an incremental number greater than 10000 that is unique for each product. The PID is on a label affixed to the product (Fig. 6.1).

**Fig. 6.1:** PID location. The blue arrow points to the piggyback board PID.

## 7 Power Requirements

The A55PETx is powered by the DT5550W motherboard. The motherboard is powered by an external 220-110 V to 12V, 60W AC/DC stabilized power supply provided with the board and included in the delivered kit, together with a standard wall IEC C13 power chord.

**Note:** using a different power supply source, like battery or linear type, it is recommended the source to provide +12 V and 2A; the power jack is a 2.1 mm type, a suitable cable is the RS 656-3816 type (or similar)

**The maximum operating voltage is 12.8V while the minimum is 9V**

## 8 Cooling Management

The A55PETx piggyback board can operate in the temperature range -20 + 50 °C.

The following paragraph refers to the piggyback mounted onto the DT5550W board.

An air flow fan is installed onboard, onto the FPGA of the DT5550W. The user must take in care to provide a proper cooling to the board with external fan if the board is used in an enclosure or if the board is installed in a setup with poor air flow.

Excessive temperature will, in first instance, reduce the performance and the quality of the measurements and can also damage the board.

Please do not stop fan operation to avoid FPGA overheating. If in a single rack tower, multiple units are installed, please consider external fans or rack mounted air conditioning system.

If the board is stored in cold environmental, please check for water condensation before power on.

The board has not been tested for radiation hardness. High energy particle can be source of soft error and can damage the FPGA. If used in strong proton or neutron beams, arrange proper shielding or remote the sensor with a custom cable.

## 9 Installing the device

- Connect the A55PETx piggyback onto the mezzanine connector of the DT5550W motherboard

- Power on the DT5550W as described in [RD2]

If the A55PETx is purchased together with the DT5550W motherboard, the system is provided already assembled, as shown in **Figure 5.1**.

**ONLY QUALIFIED PERSONNEL SHOULD PERFORM INSTALLATION, OPERATIONS**

**DO NOT INSTALL THE EQUIPMENT SO THAT IT IS DIFFICULT TO OPERATE THE ON/OFF SWITCH ONBOARD**

**IT IS RECOMMENDED THAT THE SWITCH OR CIRCUIT-BREAKER IS NEAR THE EQUIPMENT**

**THE SAFETY OF ANY SYSTEM THAT INCORPORATES THE DEVICE IS UNDER THE RESPONSIBILITY OF THE ASSEMBLER OF THE SYSTEM**

**A55PETx is an ESD sensitive item. Handling without ESD protective covering shall be performed only into approved ESD Protected Area (EPAs)**

**A55PETx complies with EMC directive only if installed in a CE marked system**

Do not use the device and contact technical support if one of these situations is verified:

- Enclosure integrity is compromised

- Insulation of HV chord is damaged (if present)

- The indication led or display is not performing as required (e.g. led not working, display with incorrect graphic)

- Fans are not working (if present)

# 10 Hardware Description

The A55PETx piggyback boards are designed to be plugged onto DT5550W motherboard to build a complete readout system for SiPM (32, 64 or 128 channels).

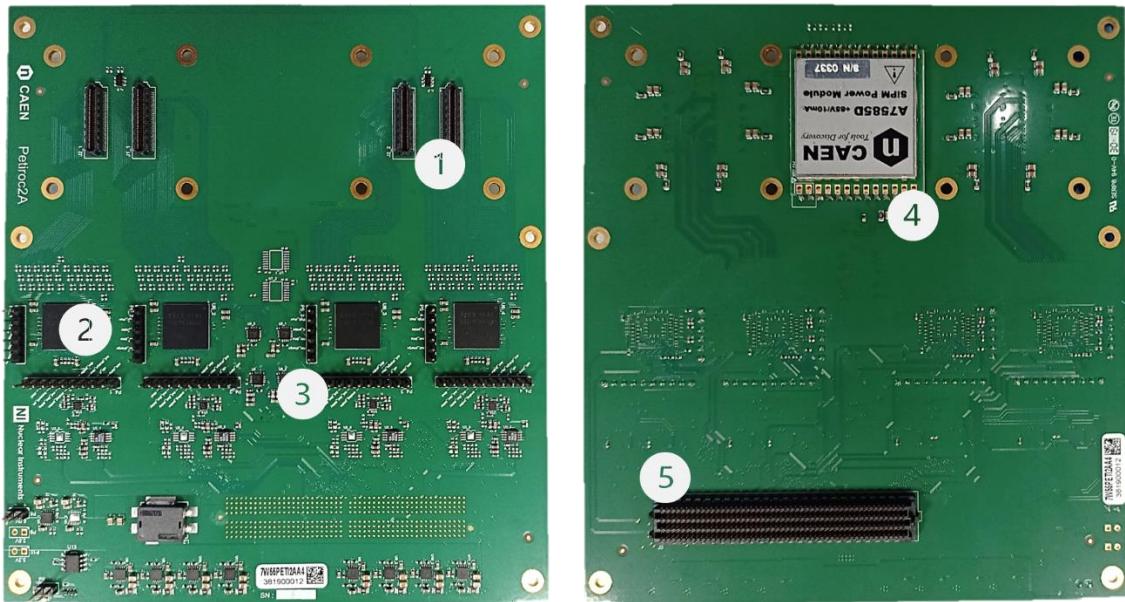

In the following picture the most important components and connectors on the front and rear side of the A55PET2 (taken as example for the A55PETx family) are highlighted.

Figure 10.1: general view (left front side, right: rear side) of the A55PET4 piggyback, shown as example.

| Number | Description                                                                                                                                                                                                                                                                                    |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | <b>Input connectors</b> SAMTEC SS4-40-3.00-L-D-K-TR, compatible with 64-channel Hamamatsu matrix S13361-3050AE-08. Each couple of connectors can host a SiPM matrix each. The pinout is the following:<br> |

| 2      | PETIROC ASIC in BGA packaging                                                                                                                                                                                                                                                                  |

| 3      | <b>Test Pins</b> – 2.54 mm strip – refer to Par. <b>Test Pins</b> for more details                                                                                                                                                                                                             |

| 4      | <b>A7585D 20-85 V Power Supply</b> for SiPM biasing                                                                                                                                                                                                                                            |

| 5      | <b>Mezzanine connector</b> – SAMTEC SEAM-50-02.0-S-08-2-A-K-TR, 8 column, 64 rows, BGA array connector used to plug the piggyback onto the DT5550W motherboard                                                                                                                                 |

Table 10.1: description of the main components and connectors of the A55PETx board

## SiPM connection and biasing

It is possible to connect SiPMs to the A55PETx board in three ways:

- use Hamamatsu S13361-3050AE-08 matrix to be connected directly on the onboard Samtec SS4-40-3.0-L-D-K-TR connectors.

- plug the PCB pitch adapter on the board connectors and use the exposed 2.54 mm pitch strip to easily solder any kind of SiPM matrix or array (refer to **Pitch Adapter Kit**). SiPM cathodes must be connected to *Bias* pins, while anodes to *S<sub>x</sub>* pins.

- use a compatible remoting cable to be plugged on the board connectors and design a custom PCB hosting SiPMs – for example CAEN 64-channels Remotization kit **[RD3]**

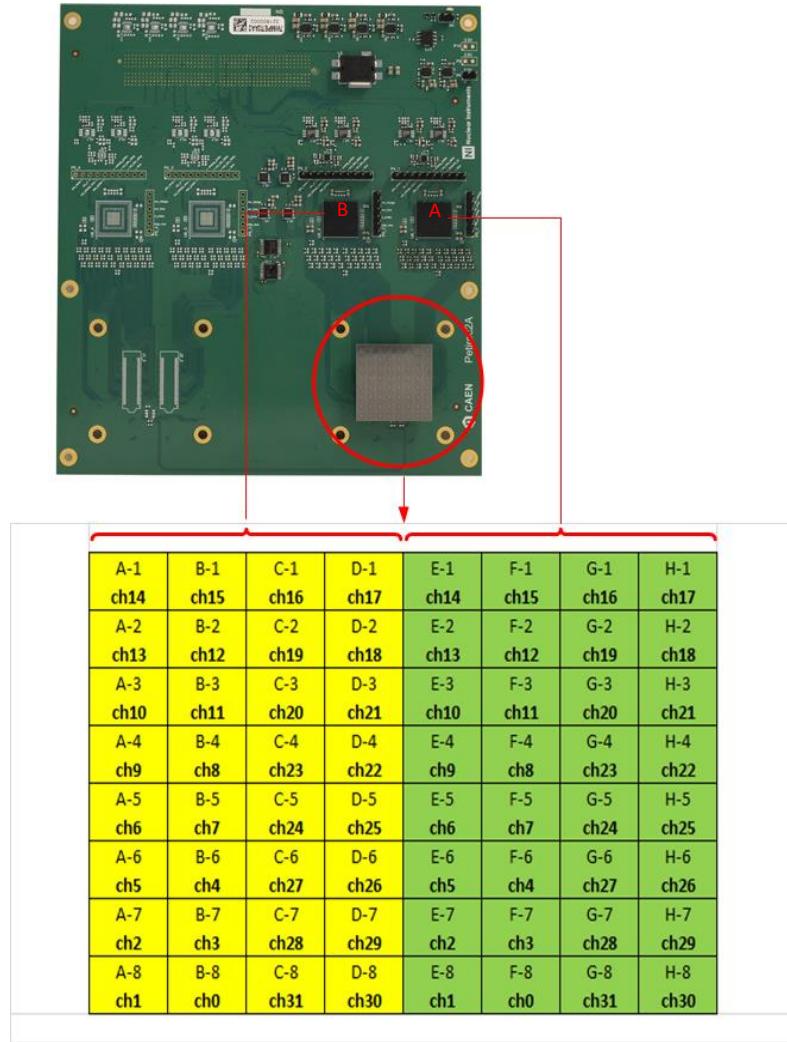

If connecting a S13361-3050AE-08 Hamamatsu 64-channels matrix directly onboard, the resulting correspondence with the board readout channels is the following:

**Figure 10.2:** the Hamamatsu S13361-3050AE-08 connected onboard. The grid reports the association between the matrix pixels (A-1 ... H-8) and the ASIC channels (ch0 ... ch31). The green-coloured pixels are connected to ASIC A while yellow-coloured pixels are connected to ASIC B.

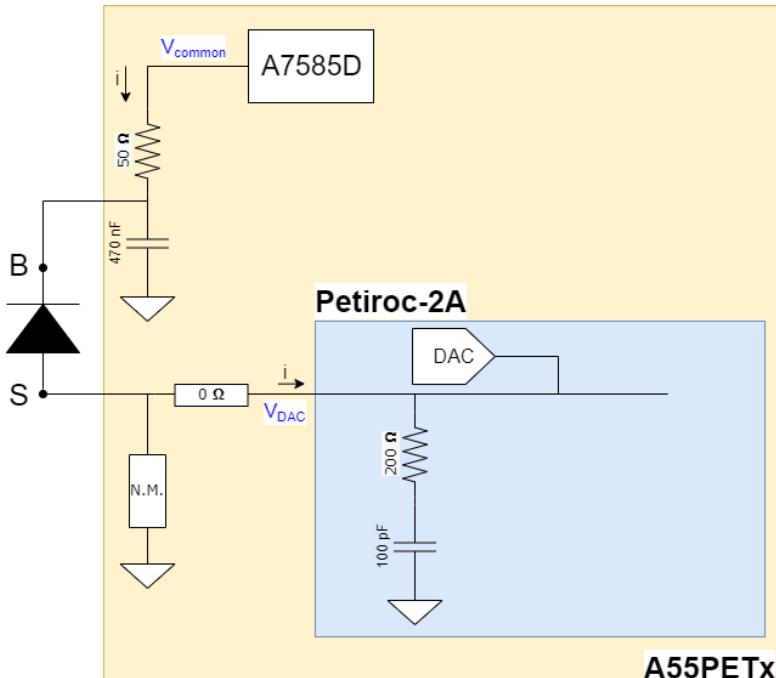

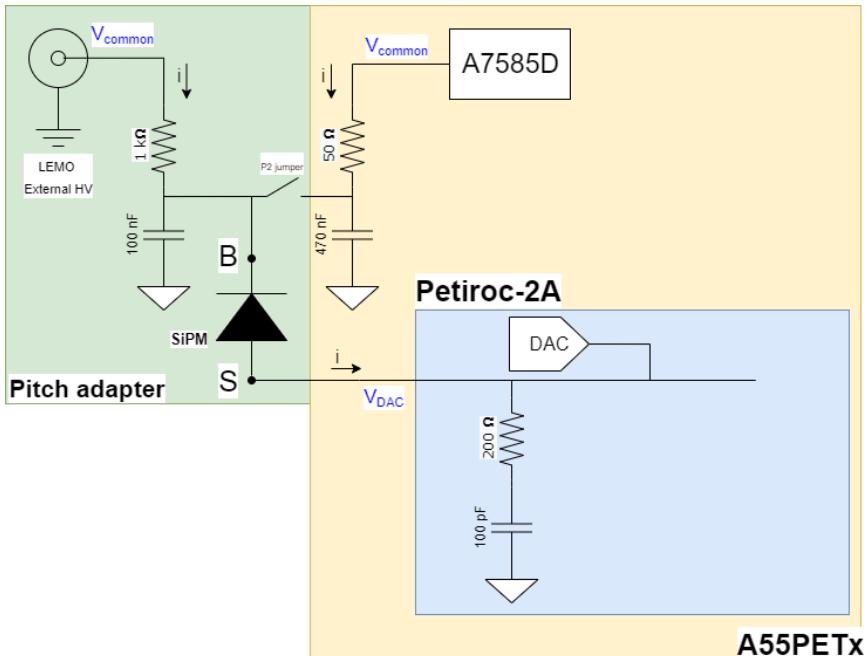

The SiPM bias is provided onboard by the CAEN A7585D Power Supply module, which is extremely low noise (no additional filters needed). The bias lines for SiPMs are grouped eight by eight and connected to the A7585D through a  $50\ \Omega$  resistance in series, as shown in **Figure 10.3**. The provided PCB adapter, instead, is equipped with independent filters for each bias line to be fed into the SiPMs.

Since the A7585D feeds the SiPM with positive high voltage, the anode of SiPMs are independently connected to the ASIC input lines, while cathodes are connected to the bias voltage (see **Figure 10.3**). On the A55PETx, before feeding the ASIC input channel, the SiPM signal passes through two components. By default, a short circuit configuration is mounted, with a series  $0\ \Omega$  resistance and no component mounted towards ground. In this configuration, the SiPM generates a positive pulse which is processed by the ASIC.

At the ASIC input stage, an 8-bit DAC allows to perform a fine tuning of the bias, individually for each SiPM channel. The voltage can be adjusted in the range 0-1 V. This is important in particular to tune the gain of each element, especially when connecting single SiPMs, which can have a spread on the breakdown voltage up to 400 mV. In default SiPM configuration (as in **Figure 10.3**), increasing the DAC value has the effect of lowering the effective bias voltage on the SiPM.

Figure 10.3: SiPM connection scheme to the ASIC input lines in standard configuration. N.M. means Not Mounted component.

**Note:** in case the user wants to use negative bias SiPMs, an external power supply is needed and the board components must be modified to achieve the correct coupling of the SiPMs to the ASIC. Refer to [Connecting a matrix in negative-bias configuration](#) for more details.

## Pitch Adapter Kit

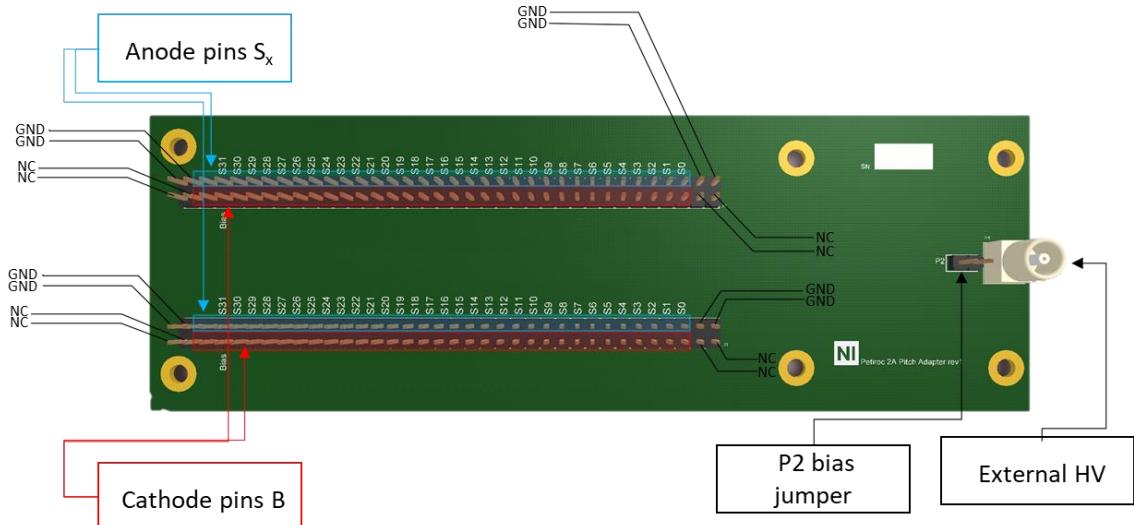

CAEN provides with the A55PETx board, an adapter kit composed by one or two 64-ch PCB boards, to allow the user to easily connect any kind of single SiPM, matrix or array to the board.

The PCB is designed to be pressure-pluggable onto the input connectors available onboard and converts a couple of SAMTEC SS4-40-3.00-L-D-K-TR to a **double 2.54 mm strip connector** (see [Figure 10.4](#)). In this way, the user can easily mount through-holes 2.54 mm headers on the adapter PCB to connect SiPMs anode/cathode lines. Using two of these PCBs allows to exploit the 128 readout channels of the A55PETx board, exposed on the 2.54 mm pitch strips.

The adapter provides 64 signal readout lines ( $S_x$ ) and 64 sensor bias (B) lines. Each adapter has two 2.54mm-pitch strip connectors, each one exposing 32 bias/signal couples. Once the adapters are plugged in, the bias can be provided by the A7585D on the A55PETx board itself or externally through the LEMO HV connector available on the adapter. The jumper P2, if inserted, connects the bias pins to the DT5550W High Voltage generator while the LEMO connector is always connected to the Bias pins. The adapter is designed to optimize connections to SiPMs. Each detector has independent bias lines filtered with  $1k\Omega$  resistor and  $100nF$  capacitor, as shown in Figure 10.6

**In order to operate with external bias generator, the jumper P2 should be removed from the pitch adapter, in order to avoid damaging the A55PETx board. External high voltage should not exceed 100V.**

**Note:** the channels pinout indicated on the PCB silkscreen is merely indicative. The effective correspondence with the ASIC channels is defined in the *Mapping* section of the DT5550W Readout Software.

**Note:** Refer to Figure 10.7 for instructions to correctly plug the pitch adapter onto the A55PETx.

**Figure 10.4:** view of the 64-ch pitch adapters. The strip connectors (each for 32 channels), the External HV LEMO and the P2 jumper are clearly visible.

| Name             | Description                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Anode pins $S_x$ | <b>2.54 mm strip – 32 pins.</b> Connection to ASIC input lines, to wire SiPM anodes. GND = ground                                                                                               |

| Cathode pins B   | <b>2.54 mm strip – 32 pins.</b> Connection to High Voltage lines, to wire SiPM cathodes for biasing. NC = not connected                                                                         |

| External HV      | <b>LEMO HV.</b> External High Voltage input for SiPM biasing. Connection to SiPMs cathodes as shown in <b>Figure 10.6</b> . The external HV connector is always connected to the Cathode pins B |

| P2 Jumper        | If inserted, connects the Cathode pins B to the DT5550W High Voltage generator                                                                                                                  |

**Table 10.2:** description of the pitch adapter connectors.

**Figure 10.5:** dimensions of the pitch adapter.

Figure 10.6: SiPM connection scheme to the ASIC and biasing lines when using the pitch adapter kit

Figure 10.7: Top: how to plug the pitch adapter on the board's SiPM connector. The connectors are pressure-pluggable. Bottom: general view of a DT5550W with A55PET4 piggyback and two pitch adapters plugged in. In this configuration, all 128 channels of the DT5550W board are exposed on the strip connectors.

## Connecting a matrix in negative-bias configuration

The A55PETx piggyback is designed to provide positive bias voltage to the SiPM. In this standard configuration, suitable for a wide range of SiPM matrices, the A7585D feeds the SiPM with positive high voltage, the anode of SiPMs are independently connected to the ASIC input lines, while cathodes are connected to the bias voltage line (see [Figure 10.3](#)).

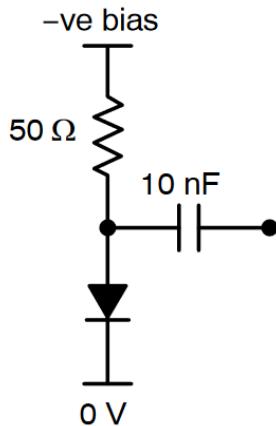

However, exploiting the features of the pitch adapter, it is possible to read out SiPMs also in negative-bias configuration, for instance the one suggested for SensL ARRAYJ-60035-64P with common cathode. In order to do that, an external high

voltage source can be connected to the LEMO of the pitch adapter and the board needs a component modifications in order to correctly couple the sensor to the ASIC. A typical connection of a negative bias SiPM is shown in **Figure 10.8**.

**Figure 10.8:** typical connection of a cell of a SiPM matrix with common cathode using negative bias.

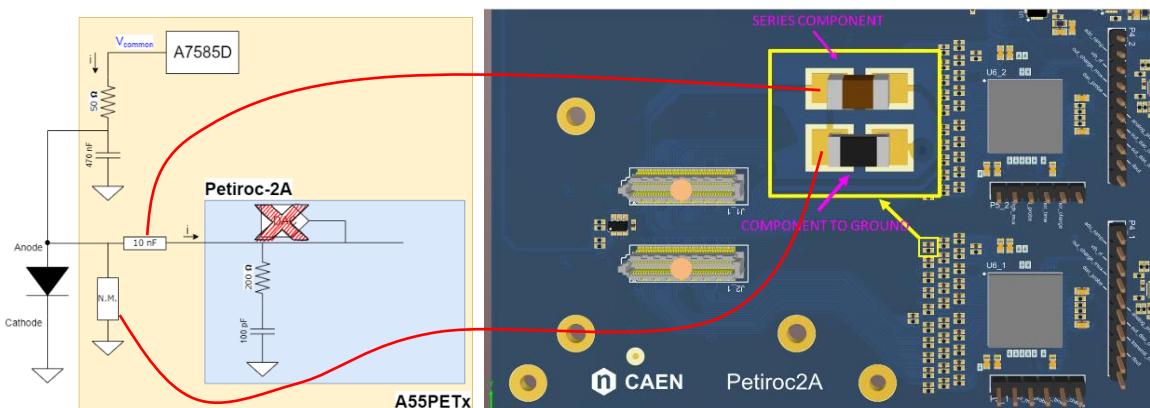

In order to AC couple the sensor, the user needs to mount a series 10 nF capacitance replacing the 0 Ω resistance (mounted by default), as shown in **Figure 10.9**. The component to ground can be left not mounted. Using the AC coupled configuration, the ASIC internal DAC is useless.

**Figure 10.9:** connections of the SiPM to the ASIC input stage, to obtain AC coupling with negative bias voltage. All series components (by default 0 Ω resistance) must be dismounted and replaced with a 10 nF capacitance. The component to ground can be left not mounted. The hardware components for each input channels, are shown on the right.

## Temperature Feedback

Near each SiPM connector hosted on the A55PETx board, a temperature sensor is soldered. This sensor is read by the FPGA and the information is used by the DT5550W Readout Software for SiPM bias active compensation during temperature changes.

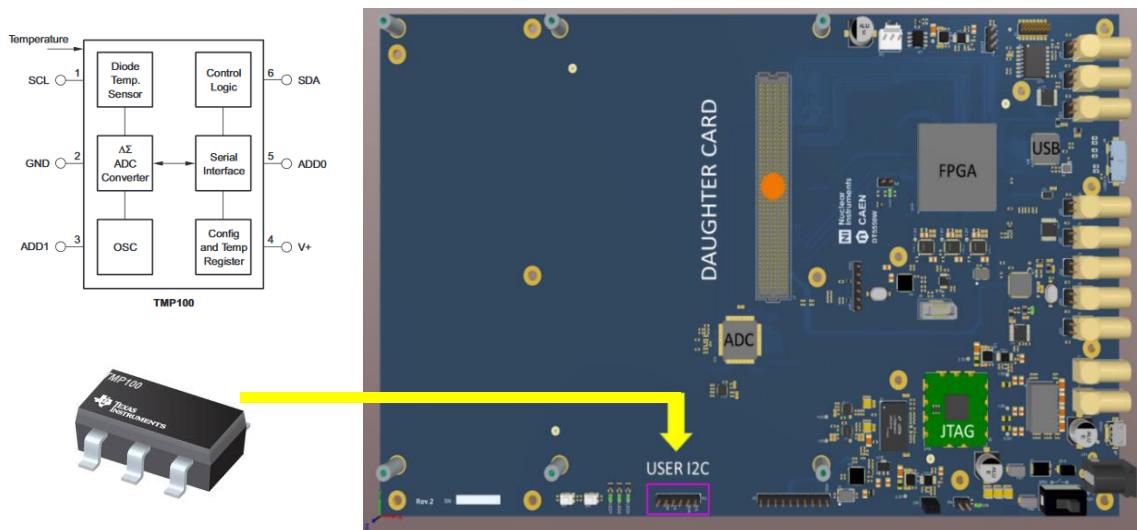

In case of using SiPMs mounted on an external PCB, it is recommended exploiting the USER I2C bus, available on the motherboard, to read out an external sensor (pinout of I2C on the PCB serigraphy). In this case, in order to use the active bias compensation as defined in the DT5550W Readout Software, the user needs a Texas Instruments TMP100 external sensor, configuring its address at 0x50, bit A0 = GND and A1 = 3.3V.

**Figure 10.10:** the user I2C interface on the motherboard, to be used for external temperature sensor connection.

In general, there are several methods to perform the active SiPM bias compensation, using:

- The average temperature read out by the two sensors soldered on the piggyback PCB, near the matrix connectors. This method is directly supported by DT5550W Readout Software.

- The temperature read by an external sensor. If using a Texas Instruments TMP100 with address 0x50, this method is directly supported by DT5550W Readout Software.

- A temperature read out with any other method (like thermocouples or similar sensors readout). The provided temperature can be passed to the SDK libraries for active bias compensation.

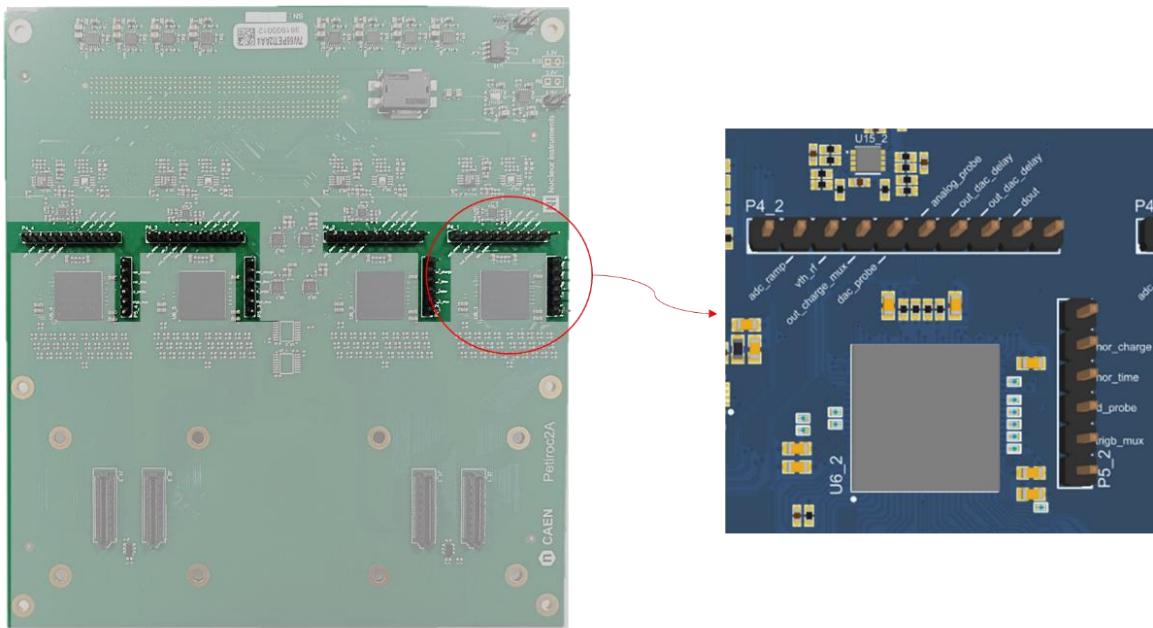

## Test Pins

On the sides of each ASIC hosted on the A55PETx board, some test pins are available, to allow the user to debug the internal operation of the chip itself. The name of each pin is reported on the PCB serigraphy (see **Table 10.3** for more details)

**Figure 10.11:** the test pins for A55PETx piggyback boards.

| Pin name  | Description                                                                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| trigb_mux | Charge triggers <b>multiplexed output</b> , available during analog readout.                                                                                       |

| d_probe   | Internal probe managed by the software. For the selected channel it shows one of the following: <ul style="list-style-type: none"> <li>• charge trigger</li> </ul> |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | <ul style="list-style-type: none"> <li>• <b>ADC ramp start</b></li> <li>• <b>hold signal</b> for the slow shaper, i.e. the delayed time trigger.</li> </ul>                                                                                                                                                                                                                                                              |