Rev. 5 - October 9th, 2024

# DT5495

Desktop Programmable Logic Unit

# Register your device

Register your device to your **MyCAEN+** account and get access to our customer services, such as notification for new firmware or software upgrade, tracking service procedures or open a ticket for assistance. **MyCAEN+** accounts have a dedicated support service for their registered products. A set of basic information can be shared with the operator, speeding up the troubleshooting process and improving the efficiency of the support interactions.

**MyCAEN+** dashboard is designed to offer you a direct access to all our after sales services. Registration is totally free, to create an account go to <https://www.caen.it/become-mycaenplus-user> and fill the registration form with your data.

<https://www.caen.it/become-mycaenplus-user/>

# Purpose of this Manual

This document contains the full hardware and software description of the DT5495 Desktop Programmable Logic Unit.

## Change Document Record

| Date                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 2 <sup>nd</sup> , 2018   | 00       | Initial release                                                                                                                                                                                                                                                                                                                                                                           |

| May 30 <sup>th</sup> , 2019     | 01       | Added Sec. <b>PLIscaler_daq</b> and Chap. <b>14</b> . Updated Sec. <b>Direct USB Driver</b> and Sec.14.2.                                                                                                                                                                                                                                                                                 |

| August 29 <sup>th</sup> , 2019  | 02       | Added "DT5495 Mezzanine Installation Notes" in Sec. <b>Reference Documents</b> . Removed "Product Code" column from <b>Tab. 1.2</b> . Updated <b>Tab. 5.5</b> , Sec. <b>Expansion Mezzanine</b> , and Sec. <b>User FPGA I/O ports</b> with impedance information and instructions on the A395D channel impedance selection. Removed Sec. 14.1 and Sec. 14.2 and renamed Chap. <b>16</b> . |

| October 25 <sup>th</sup> , 2019 | 03       | Removed "Preliminary". Updated Sec. <b>Expansion Mezzanine</b> .                                                                                                                                                                                                                                                                                                                          |

| March 31 <sup>st</sup> , 2023   | 04       | Added Sec. <b>Safety Notice</b> , and Sec. <b>12.3.1</b>                                                                                                                                                                                                                                                                                                                                  |

| October 9 <sup>th</sup> , 2024  | 05       | Added Chap. <b>7</b> and <b>8</b> . Updated Sec. <b>9.2</b> . Replaced CAEN Upgrader description (obsolete) with CAEN Toolbox in Sec. <b>10.4</b> . Updated PID description in Sec. <b>11.1.3</b> . Updated LAD signal width in <b>Tab. 12.8</b> . Updated Chap <b>16</b> .                                                                                                               |

## Symbols, Abbreviated Terms, and Notations

|       |                               |

|-------|-------------------------------|

| AM    | Address Modifier              |

| ETH   | Ethernet Interface            |

| FPGA  | Field Programmable Gate Array |

| GDG   | Gate and Delay Generator      |

| LB    | Local Bus                     |

| LBM   | Local Bus Master              |

| LBS   | Local Bus Slave               |

| LED   | Light Emitting Diode          |

| MFPGA | Main FPGA                     |

| SPI   | Serial Peripheral Interface   |

| UFPGA | User FPGA                     |

| USB   | Universal Serial Bus          |

## Reference Documents

[RD1] UM11111 – CAEN Toolbox user Manual

[RD2] A967 Adapter for P50E – 068S 68 Pin Connectors

[RD3] UM6510 – CAEN PLULib Library User Manual

[RD4] UM5175 – FW2495SC - DT5495 V2495 Scaler Firmware User Manual

[RD5] DT5495 Mezzanine Installation Notes

All documents can be downloaded at: <https://www.caen.it/support-services/documentation-area/>

## Manufacturer Contacts

---

**CAEN S.p.A.**

Via Vetraia, 11 55049 Viareggio (LU) - ITALY

Tel. +39.0584.388.398 Fax +39.0584.388.959

[www.caen.it](http://www.caen.it) | [info@caen.it](mailto:info@caen.it)

© CAEN SpA – 2024

## Limitation of Responsibility

If the warnings contained in this manual are not followed, CAEN will not be responsible for damage caused by improper use of the device. The manufacturer declines all responsibility for damage resulting from failure to comply with the instructions for use of the product. The equipment must be used as described in the user manual, with particular regard to the intended use, using only accessories as specified by the manufacturer. No modification or repair can be performed.

## Disclaimer

No part of this manual may be reproduced in any form or by any means, electronic, mechanical, recording, or otherwise, without the prior written permission of CAEN spa.

The information contained herein has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies. CAEN spa reserves the right to modify its products specifications without giving any notice; for up to date information please visit [www.caen.it](http://www.caen.it).

## Made in Italy

We remark that all our boards have been designed and assembled in Italy. In a challenging environment where a competitive edge is often obtained at the cost of lower wages and declining working conditions, we proudly acknowledge that all those who participated in the production and distribution process of our devices were reasonably paid and worked in a safe environment (this is true for the boards marked "MADE IN ITALY", while we cannot guarantee for third-party manufacturers).

# Index

|                                                                 |           |

|-----------------------------------------------------------------|-----------|

| Purpose of this Manual .....                                    | 3         |

| Change Document Record .....                                    | 3         |

| Symbols, Abbreviated Terms, and Notations .....                 | 3         |

| Reference Documents .....                                       | 3         |

| Manufacturer Contacts .....                                     | 3         |

| Limitation of Responsibility .....                              | 4         |

| Disclaimer .....                                                | 4         |

| Made in Italy .....                                             | 4         |

| <b>Index .....</b>                                              | <b>5</b>  |

| <b>List of Figures .....</b>                                    | <b>6</b>  |

| <b>List of Tables .....</b>                                     | <b>7</b>  |

| <b>Safety Notices .....</b>                                     | <b>8</b>  |

| <b>1 Introduction .....</b>                                     | <b>10</b> |

| <b>2 Block Diagram .....</b>                                    | <b>12</b> |

| <b>3 Main Components and Interconnections .....</b>             | <b>13</b> |

| 3.1 USB Interface .....                                         | 14        |

| 3.2 Ethernet Interface .....                                    | 14        |

| 3.3 Main FPGA .....                                             | 14        |

| 3.4 User FPGA .....                                             | 14        |

| 3.5 Gate and Delay Generator .....                              | 14        |

| 3.6 Clock Distribution .....                                    | 14        |

| <b>4 Front Panel Connectors, LEDs and Labels .....</b>          | <b>15</b> |

| 4.1 Front Panel .....                                           | 16        |

| 4.2 Rear Panel .....                                            | 18        |

| <b>5 Technical Specifications .....</b>                         | <b>19</b> |

| <b>6 Power Requirements .....</b>                               | <b>21</b> |

| <b>7 Packaging and Compliancy .....</b>                         | <b>22</b> |

| <b>8 PID (Product Identifier) .....</b>                         | <b>24</b> |

| <b>9 Getting Started with DT5495 .....</b>                      | <b>25</b> |

| 9. Expansion Mezzanines .....                                   | 25        |

| 9.1 Mezzanine Installation .....                                | 25        |

| 9.2 Front Panel Connector Cabling .....                         | 25        |

| 9.3 Power-on Configuration Sequence .....                       | 26        |

| 9.3.1 Restore Function .....                                    | 26        |

| <b>10 Driver and Software Installation .....</b>                | <b>27</b> |

| 10.1 Drivers .....                                              | 27        |

| 10.1.1 Direct USB Driver .....                                  | 27        |

| 10.2 Ethernet Configuration .....                               | 31        |

| 10.3 Web Interface .....                                        | 33        |

| 10.4 Software Tools .....                                       | 34        |

| 10.4.1 CAEN Toolbox .....                                       | 34        |

| 10.4.2 PLULib Library .....                                     | 35        |

| 10.4.3 PLUscaler_daq .....                                      | 35        |

| <b>11 Communication Interfaces .....</b>                        | <b>36</b> |

| 11.1 Address Map .....                                          | 36        |

| 11.1.1 User FPGA Data Access (0x0000-0x0FFF) .....              | 36        |

| 11.1.2 User FPGA Register Access (0x1000-0x7FFF) .....          | 36        |

| 11.1.3 Configuration ROM (0x8100-0x81FF) .....                  | 37        |

| 11.1.4 Configuration and Status Registers (0x8200-0x83FF) ..... | 37        |

| 11.1.5 MFPGA Firmware Revision Register .....                   | 38        |

| 11.1.6 Software Reset Register .....                            | 38        |

| 11.1.7 Scratch Register .....                                   | 38        |

| 11.1.8 Flash Configuration (0x8500-0x8AFF) .....                | 38        |

| 11.1.9 Internal Scratch SRAM(0x8C00-0x8FFF) .....               | 38        |

|                                                         |           |

|---------------------------------------------------------|-----------|

| <b>12 Firmware Development.....</b>                     | <b>39</b> |

| 12.1 Introduction.....                                  | 39        |

| <b>12.1.1 Safety Notice .....</b>                       | <b>39</b> |

| 12.2 Sci-Compiler.....                                  | 40        |

| 12.3 User FPGA I/O ports.....                           | 40        |

| <b>12.3.1 Preventing User FPGA Input Conflicts.....</b> | <b>43</b> |

| 12.4 Local Bus Interface .....                          | 44        |

| 12.5 Gate and Delay Controller .....                    | 46        |

| <b>12.5.1 General Description .....</b>                 | <b>46</b> |

| <b>12.5.2 Register Description .....</b>                | <b>47</b> |

| <b>12.5.3 Example Procedures.....</b>                   | <b>48</b> |

| 12.6 Porting V1495 to DT5495 .....                      | 49        |

| <b>13 Demo Firmware .....</b>                           | <b>50</b> |

| 13.1 Introduction.....                                  | 50        |

| 13.2 Demo Structure .....                               | 50        |

| 13.3 Demo Setup .....                                   | 50        |

| 13.4 Gate Pattern Demo Description .....                | 51        |

| <b>13.4.1 Introduction.....</b>                         | <b>51</b> |

| <b>13.4.2 Register Map .....</b>                        | <b>51</b> |

| <b>13.4.3 Register Description .....</b>                | <b>51</b> |

| 13.5 Pattern Recorder Demo Description .....            | 54        |

| <b>13.5.1 Introduction.....</b>                         | <b>54</b> |

| <b>13.5.2 Register Map .....</b>                        | <b>54</b> |

| <b>13.5.3 Register Description .....</b>                | <b>54</b> |

| 13.6 DAC Demo Description .....                         | 56        |

| <b>13.6.1 Introduction.....</b>                         | <b>56</b> |

| <b>13.6.2 Register Map .....</b>                        | <b>56</b> |

| <b>13.6.3 Register Description .....</b>                | <b>56</b> |

| 13.7 Gate and Delay Demo Description .....              | 58        |

| <b>13.7.1 Introduction.....</b>                         | <b>58</b> |

| <b>13.7.2 Register Map .....</b>                        | <b>58</b> |

| <b>13.7.3 Register Description .....</b>                | <b>58</b> |

| <b>14 FW2495SC Pay Firmware .....</b>                   | <b>61</b> |

| <b>15 Software Development .....</b>                    | <b>62</b> |

| <b>16 Technical Support.....</b>                        | <b>63</b> |

## List of Figures

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| Fig. 2.1: Block diagram .....                                                                     | 12 |

| Fig. 3.1: Main components and interconnections.....                                               | 13 |

| Fig. 3.2: The UFGPA and GDG interface.....                                                        | 14 |

| Fig. 4.1: front (top) and rear (down) panel view .....                                            | 15 |

| Fig. 8.1:PID location on the desktop device (the number in the picture is purely indicative)..... | 24 |

| Fig. 9.1: DT5495 motherboard with mezzanine boards .....                                          | 25 |

| Fig. 9.2: Multi-pin connector pin assignment .....                                                | 25 |

| Fig. 9.3: CAEN A967 Cable Adapter.....                                                            | 25 |

| Fig. 10.1: DT5495 hardware detection .....                                                        | 27 |

| Fig. 10.2: USB driver manual installation: Step1.....                                             | 28 |

| Fig. 10.3: USB driver manual installation: Step2.....                                             | 28 |

| Fig. 10.4: USB driver manual installation: Step3.....                                             | 29 |

| Fig. 10.5: USB driver manual installation: Step4.....                                             | 29 |

| Fig. 10.6: USB driver manual installation: Step5.....                                             | 30 |

| Fig. 10.7: The Network and Sharing Center window .....                                            | 31 |

| Fig. 10.8: Properties window of the Ethernet network .....                                        | 32 |

| Fig. 10.9: Ethernet Properties window".....                                                       | 32 |

| Fig. 10.10: Properties window of the "Internet Protocol Version (TPC/IPv4)" .....                 | 32 |

| Fig. 10.11: Instrument Information page of the DT5495 Web Interface.....                          | 33 |

| Fig. 10.12: Instrument Information page of the DT5495 Web Interface.....                          | 33 |

| Fig. 10.13: CAEN Toolbox Graphical User Interface .....                                           | 34 |

| Fig. 10.14: CAEN PLULib Demo application prompt.....                                              | 35 |

| Fig. 10.15: PLUscaler_daq prompt.....                                                             | 35 |

|                                                                                               |    |

|-----------------------------------------------------------------------------------------------|----|

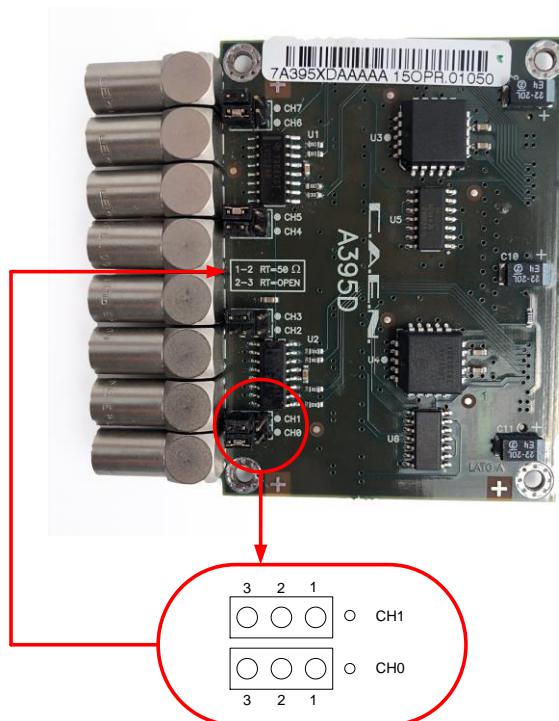

| Fig. 12.1: A395 jumpers for the channel impedance selection .....                             | 41 |

| Fig. 12.2: CAENComm Demo Java and LabVIEW graphical interface.....                            | 42 |

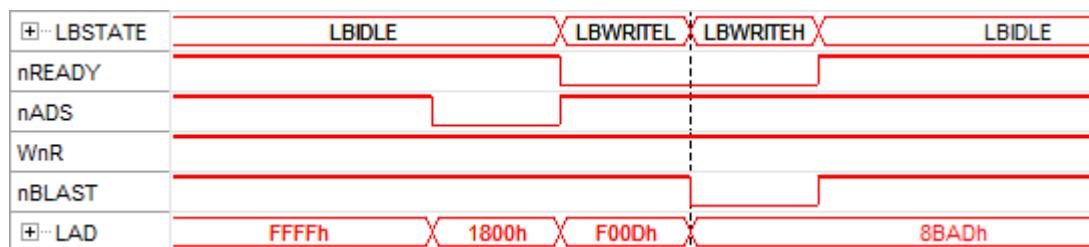

| Fig. 12.3: Local bus signals at a write access (x8BADF00D is written on register x1800) ..... | 44 |

| Fig. 12.4: Local bus signal at a read access (x8BADF00D is read from register x1800) .....    | 44 |

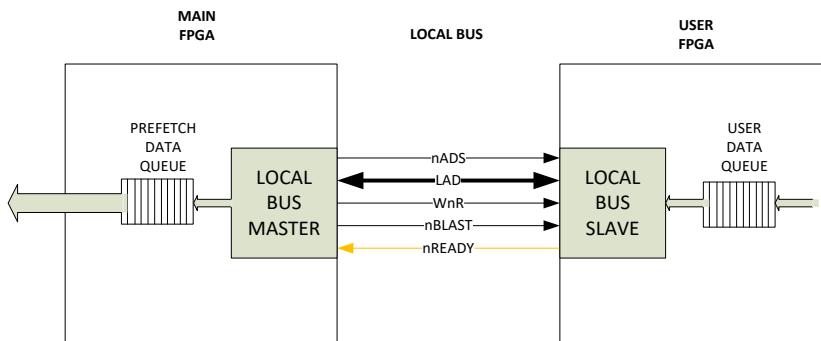

| Fig. 12.5: Prefetch mechanism .....                                                           | 45 |

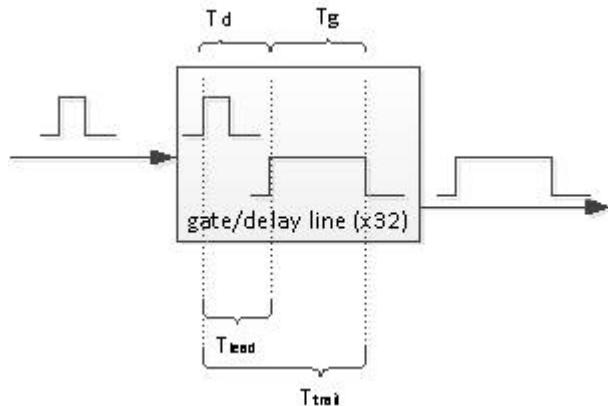

| Fig. 12.6: Gate and Delay parameters representation .....                                     | 46 |

## List of Tables

|                                                                                                  |    |

|--------------------------------------------------------------------------------------------------|----|

| Tab. 1.1: Comparison table between V1495 and DT5495.....                                         | 10 |

| Tab. 1.2: Table of models and related items.....                                                 | 11 |

| Tab. 5.1: DT5495 specifications table.....                                                       | 19 |

| Tab. 5.2: A395A Mezzanine specifications table.....                                              | 19 |

| Tab. 5.3: A395B Mezzanine specifications table.....                                              | 20 |

| Tab. 5.4: A395C Mezzanine specifications table .....                                             | 20 |

| Tab. 5.5: A395D Mezzanine specifications table .....                                             | 20 |

| Tab. 5.6: A395E Mezzanine specifications table.....                                              | 20 |

| Tab. 7.1: Delivered kit content .....                                                            | 22 |

| Tab. 11.1: DT5495 register address map.....                                                      | 36 |

| Tab. 11.2: ROM Address Map of the DT5495 .....                                                   | 37 |

| Tab. 11.3: CSR registers .....                                                                   | 37 |

| Tab. 12.1: Clock ports description table .....                                                   | 40 |

| Tab. 12.2: Mainboard Robinson-Nugent connector description table .....                           | 40 |

| Tab. 12.3: LEMO G ports description table.....                                                   | 40 |

| Tab. 12.4: Expansion I/O ports description table .....                                           | 40 |

| Tab. 12.5: A395D mapping.....                                                                    | 41 |

| Tab. 12.6: LED ports description table .....                                                     | 42 |

| Tab. 12.7: Gate and Delay Generator ports description table .....                                | 42 |

| Tab. 12.8: Local Bus ports description table .....                                               | 42 |

| Tab. 12.9: Main parameters of the Gate and Delay Generator.....                                  | 46 |

| Tab. 12.10: Local Bus registers description for the Gate and Delay Generator configuration ..... | 47 |

# Safety Notices

**N.B. Read carefully the “Precautions for Handling, Storage and Installation” document provided with the product before starting any operation.**

The following HAZARD SYMBOLS may be reported on the unit:

|                                                                                     |                                      |

|-------------------------------------------------------------------------------------|--------------------------------------|

|    | Caution, refer to the product manual |

|    | Caution, risk of electrical shock    |

|    | Protective conductor terminal        |

|   | Earth (Ground) Terminal              |

|  | Alternating Current                  |

|  | Three-Phase Alternating Current      |

The following symbol may be reported in the present manual:

General warning statement

The symbol could be followed by the following terms:

- **DANGER:** Indicates a hazardous situation that, if not avoided, will result in serious injury or death.

- **WARNING:** Indicates a hazardous situation that, if not avoided, could result in death or serious injury.

- **CAUTION:** Indicates a situation or condition that, if not avoided, could cause physical injury, or damage the product and/or its environment.

**CAUTION:** Avoid potential hazards.

**USE THE PRODUCT ONLY AS SPECIFIED.**

**ONLY QUALIFIED PERSONNEL SHOULD PERFORM SERVICE PROCEDURES**

**CAUTION:** Avoid Electric Overload.

**TO AVOID ELECTRIC SHOCK OR FIRE HAZARD, DO NOT POWER A LOAD OUTSIDE OF ITS SPECIFIED RANGE**

**CAUTION:** Avoid Electric Shock.

**TO AVOID INJURY OR LOSS OF LIFE, DO NOT CONNECT OR DISCONNECT CABLES WHILE THEY ARE CONNECTED TO A VOLTAGE SOURCE**

**CAUTION:** Do Not Operate in Wet/Damp Conditions.

**TO AVOID ELECTRIC SHOCK, DO NOT OPERATE THIS PRODUCT IN WET OR DAMP CONDITIONS**

**CAUTION:** Do Not Operate in an Explosive Atmosphere.

**TO AVOID INJURY OR FIRE HAZARD, DO NOT OPERATE THIS PRODUCT IN AN EXPLOSIVE ATMOSPHERE**

**THIS DEVICE SHOULD BE INSTALLED AND USED BY A SKILLED TECHNICIAN ONLY OR UNDER HIS SUPERVISION**

**DO NOT OPERATE WITH SUSPECTED FAILURES.

IF YOU SUSPECT THIS PRODUCT TO BE DAMAGED, PLEASE CONTACT THE TECHNICAL SUPPORT**

# 1 Introduction

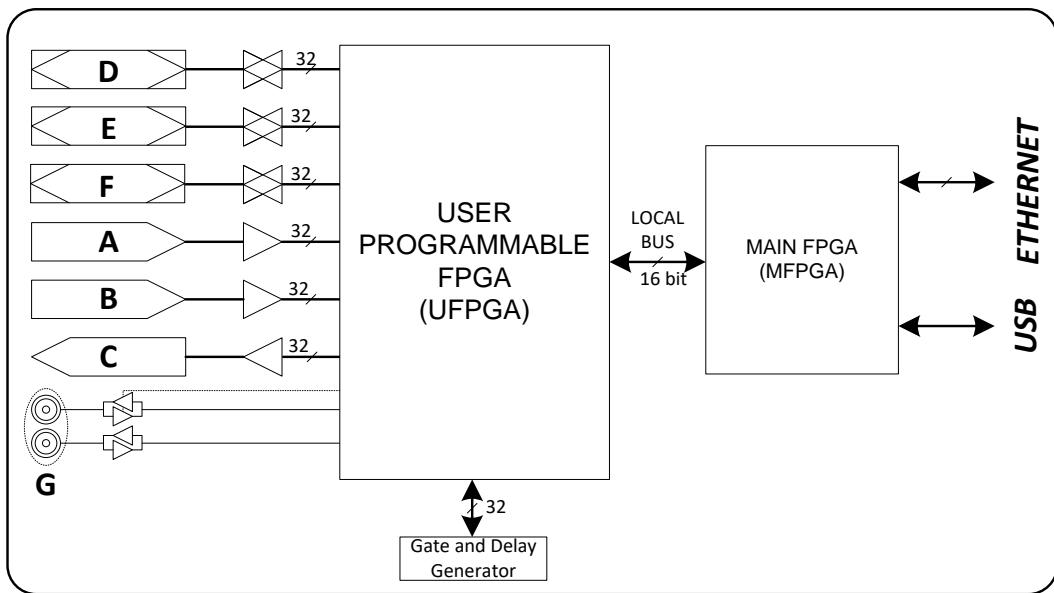

The DT5495 is a general-purpose programmable FPGA and I/O unit in a compact desktop form factor. The board is a suitable solution for the implementation of digital functions such as Coincidence, Trigger Logic, Gate and Delay Generator, Input/Output Register and more.

The programmable architecture is based on the User FPGA (hereafter UFGA). The UFGA is directly interfaced to the front panel I/Os and to an onboard Gate and Delay Generator, that allows to delay and gate up to 32 signals. A second FPGA, the Main FPGA (hereafter MFPGA), is responsible for USB and Ethernet interface management. The MFPGA communicates with the UFGA through an internal local bus.

The presence of three expansion slots interfaced to the UFGA allows to extend the channel interface of the DT5495 by adding up to three independent mezzanine boards. Five mezzanine board types are available: A395A, A395B, A395C, A395D, A395E (see **Tab. 1.2**). The DT5495 can reach a maximum of 194 I/O channels.

The board can be controlled and programmed through either the Ethernet or the USB interface. The custom firmware can be developed either with VHDL tools or the new SCI-Compiler application (Chap. 12). The firmware is then loaded on the User FPGA by a dedicated JTAG connector on the rear panel, allowing for in-system JTAG configuration and debugging (e.g. using Altera SignalTap).

Simple operations, like retrieving the board information or changing the ethernet settings, can be performed simply via the Internet or a Local Area Network (LAN) through the web interface, without need of any control software but just opening a web browser.

The DT5495 is also available in VME form factor, called V2495, which represents an evolution of CAEN V1495 board. Thanks to several analogies with the V1495 (e.g. the front panel connectors have the same function and nomenclature with respect to the V1495), users who want to upgrade their system with the DT5495 can port their firmware already developed for the V1495 just considering few hints (Sec. 12.6).

The following **Tab. 1.1** is a comparison table between the two modules.

|                          | V1495                                                                                                                                                                                                           | DT5495                       |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| User FPGA                | Altera Cyclone EPI1C20, 20k LEs                                                                                                                                                                                 | Altera Cyclone V GX, 50k LEs |

| Front Panel I/O          | Sections A and B (2 x 68-pin Robinson Nugent connector; 32 input channel each)<br>Section C (1 x 68-pin Robinson Nugent connector; 32 output channels)<br>Section G (2 X LEMO connector; input/output channels) |                              |

| On-board Delay Generator | 4 Delay lines                                                                                                                                                                                                   | 32 Gate and Delay lines      |

| Local Bus                | 16-bit 50 MHz parallel interface                                                                                                                                                                                |                              |

| VME Bus                  | Addressing spaces: A24, A32<br>Data transfer modes: D16, D32, BLT32                                                                                                                                             | Not Supported                |

| USB Interface            | Not Supported                                                                                                                                                                                                   | USB2.0                       |

| ETH Interface            | Not Supported                                                                                                                                                                                                   | ETHERNET 10/100T             |

| Mezzanine Boards         | A395A, A395B, A395C, A395D, A395E                                                                                                                                                                               |                              |

**Tab. 1.1:** Comparison table between V1495 and DT5495

**Tab. 1.2** lists the board models, the firmware and hardware related products as well as the ordering option information.

| Board Models            |  | Description                                                               |

|-------------------------|--|---------------------------------------------------------------------------|

| DT5495                  |  | Desktop Programmable Logic Unit                                           |

| 5495KITPRO              |  | DT5495 + SW555PRO - Programmable Logic Unit & Sci-Compiler PRO Bundle Kit |

| User Firmware           |  | Description                                                               |

| FW2495SC <sup>(*)</sup> |  | Channel Latching Scaler for V2495 and DT5495                              |

| Accessories             |  | Description                                                               |

| A395A                   |  | 32 LVDS/ECL/PECL input channels                                           |

| A395B                   |  | 32 LVDS output channels                                                   |

| A395C                   |  | 32 ECL output channels                                                    |

| A395D                   |  | 8 NIM/TTL input/output channels                                           |

| A395E                   |  | 8 Channel 16Bit $\pm$ 5V DAC                                              |

| A967                    |  | 32 Channel Cable Adapter (1x32 to 2x16)                                   |

**Tab. 1.2:** Table of models and related items

(\*) Pay firmware. Unlocking license needed. Please, refer to the FW2495SC web page for details.

## 2 Block Diagram

Fig. 2.1: Block diagram

### 3 Main Components and Interconnections

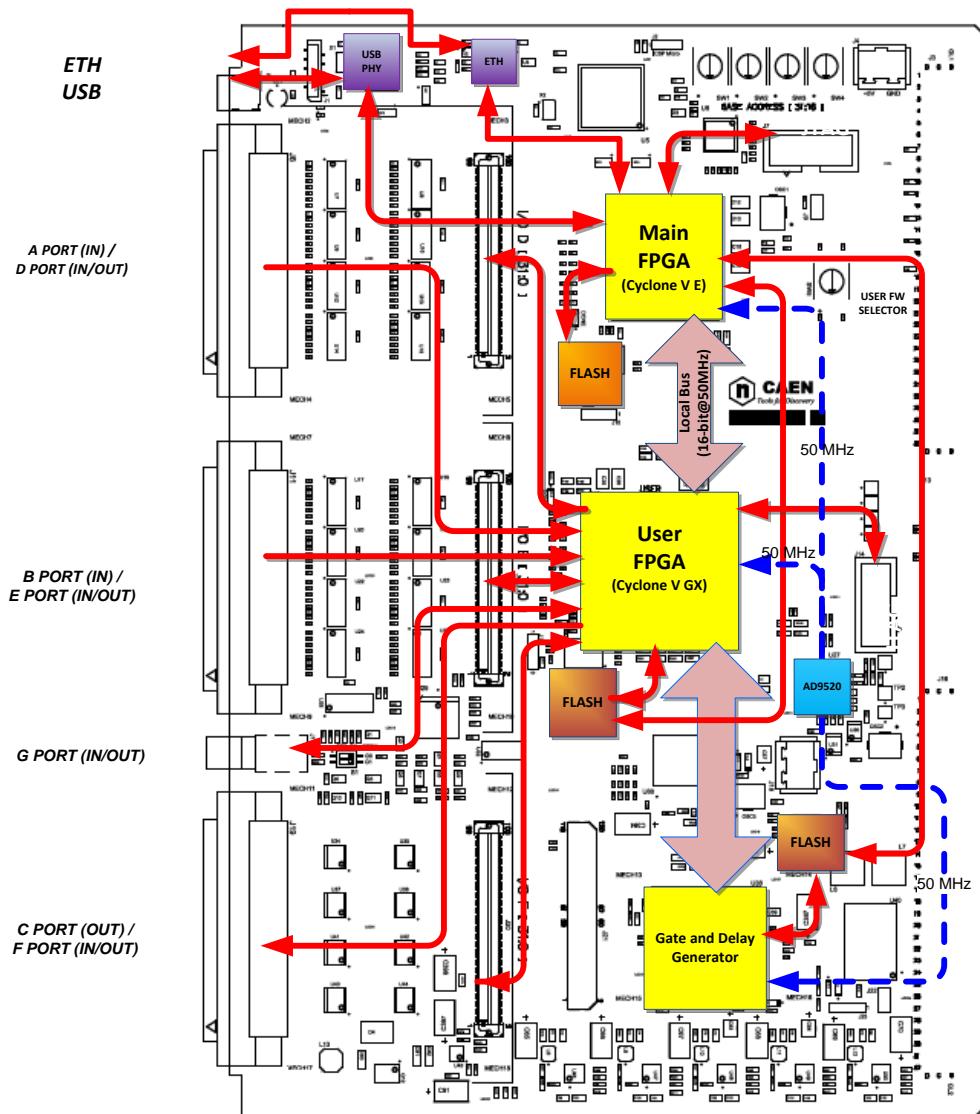

Fig. 3.1: Main components and interconnections

## 3.1 USB Interface

The DT5495 is equipped with a USB2.0 interface. The USB physical layer is managed by a high-speed transceiver controlled by the Main FPGA.

## 3.2 Ethernet Interface

In addition to the USB, the DT5495 provides a 10/100T Ethernet interface controlled by the Main FPGA.

## 3.3 Main FPGA

The MFPGA (Altera Cyclone V E) manages the Ethernet and USB interfaces and the connection with the UFFGA through a proprietary 16-bit@50 MHz local bus. The MFPGA has a dedicated external flash memory for configuration purposes. It also pilots the flash memories dedicated to loading the firmware on the UFFGA and on the GDG.

## 3.4 User FPGA

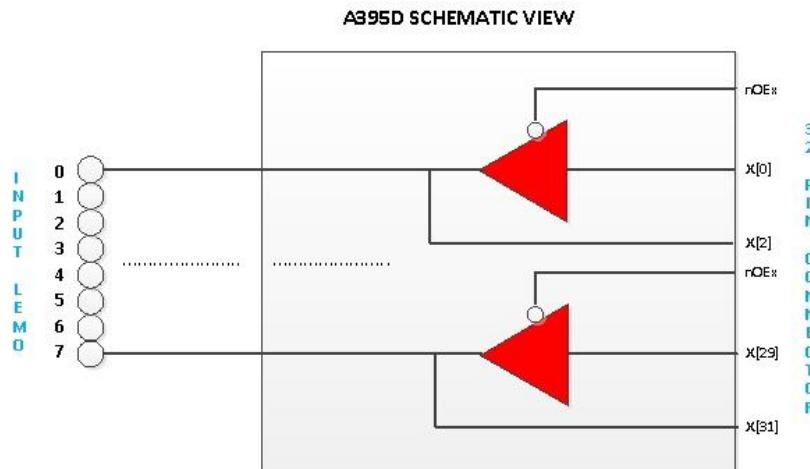

The User FPGA (Altera Cyclone V GX) manages the I/O peripherals (A/D, B/E, G, C/F ports) and communicates with the GDG. A dedicated external flash memory can store a set of firmware images to be loaded on the User FPGA. A dedicated JTAG connector allows to program the UFFGA “on-the-fly” for fast firmware prototyping and debugging.

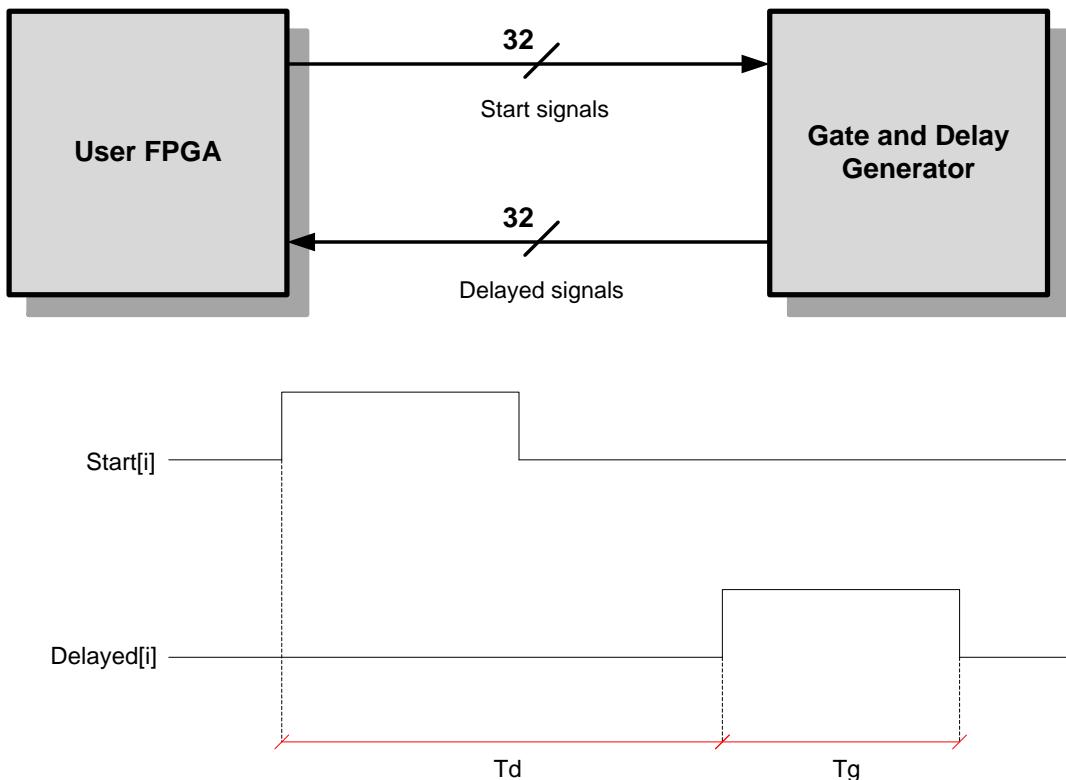

## 3.5 Gate and Delay Generator

The DT5495 hosts a Gate and Delay Generator (see [Fig. 3.2](#)) able to provide up to 32 gated and delayed signals (“delayed signals”) triggered by 32 inputs (“start signals”). The gate width and delay value are user programmable. The GDG is an external component implemented in a Xilinx Spartan-6 FPGA. It is connected through a serial bus (SPI) to the User FPGA for gate and delay register programming (refer to [Sec. 3.5](#) for detailed information). The GDG configuration is stored in a dedicated flash memory. The GDG firmware cannot be modified by the user.

[Fig. 3.2: The UFFGA and GDG interface.](#)

## 3.6 Clock Distribution

Each FPGA receives the same 50-MHz system clock generated by a common on-board oscillator.

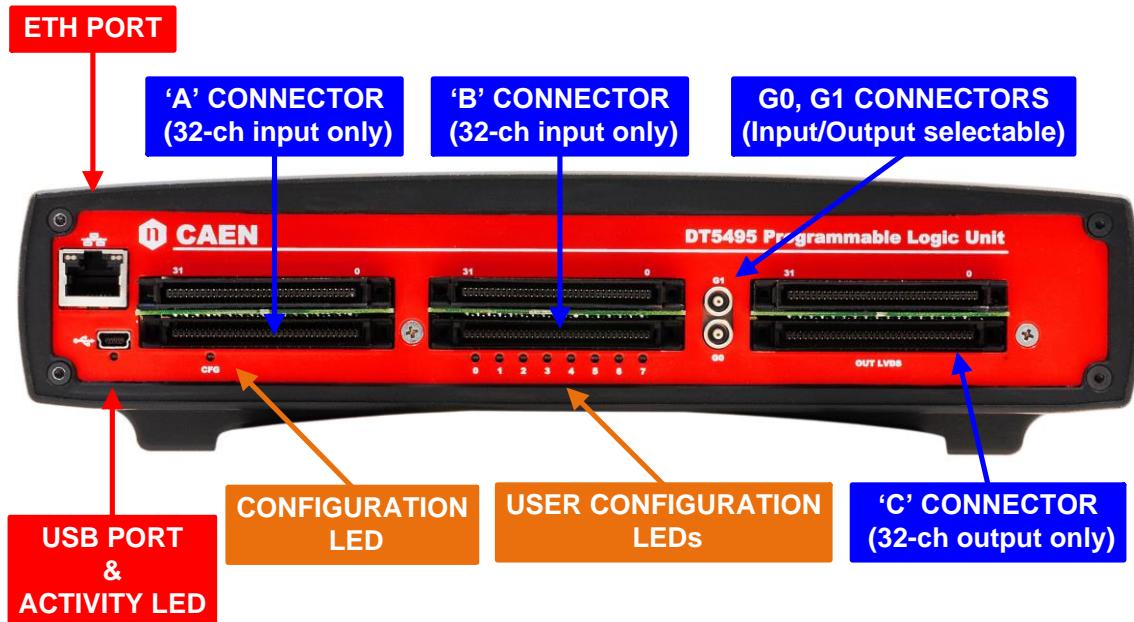

## 4 Front Panel Connectors, LEDs and Labels

Fig. 4.1: front (top) and rear (down) panel view

## 4.1 Front Panel

| USB PORT                                                                          |                                                                                                                                                                               |                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <p><b>FUNCTION</b><br/>MiniUSB connector to communicate with the DT5495 by USB link for board configuration and firmware upgrade.</p> <p><b>ELECTRICAL Specs</b><br/>N.A.</p> | <p><b>MECHANICAL Specs</b><br/>Series: miniUSB connectors.<br/>Type: SD-54819-026 (B-type).<br/>Manufacturer: Molex Inc.</p> <p><b>CABLES</b><br/>A 1-m USB standard cable is included with the DT5495 (USB A-type to miniUSB B-type).</p> |

**USB LED (GREEN):** driven by the Main FPGA, this LED lights up if a USB read/write access to the board is performed.

| ETHERNET PORT                                                                      |                                                                                                                                                                                |                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <p><b>FUNCTION</b><br/>Ethernet connector to communicate with the DT5495 for board configuration and firmware upgrade.</p> <p><b>ELECTRICAL Specs</b><br/>10/100T ETHERNET</p> | <p><b>MECHANICAL Specs</b><br/>Series: RJ45 connectors.<br/>Type: GIGABIT MIC3801D-5166.<br/>Manufacturer: Wurt.</p> <p><b>CABLES</b><br/>A 2-m Ethernet cable is included with the DT5495 (type ASSMANN: A-MCSSP60020/R).</p> |

| A, B, C CONNECTORS                                                                   |                                                                                                                                                                                                                |                                                                                                                |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|  | <p><b>FUNCTION</b><br/>Motherboard I/O 34+34 pin connectors:</p> <ul style="list-style-type: none"> <li>- A/B are inputs</li> <li>- C is an output</li> </ul> <p><b>ELECTRICAL Specs</b><br/>See Tab. 5.1.</p> | <p><b>MECHANICAL Specs</b><br/>Series: 80-0009-0666-1.<br/>Type: P50E-068-P1-SR1-TG.<br/>Manufacturer: 3M.</p> |

| ETHERNET PORT                                                                       |                                                                                                                                                                                                             |                                |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

|  | <p><b>FUNCTION</b><br/>This LED is constantly on when all the on-board FPGAs are configured by the application firmware on their relevant flash memory. The LED blinks if the MPPGA is in Factory mode.</p> | <p><b>COLOR</b><br/>Green.</p> |

**G0, G1 CONNECTORS**

|                                                                                   | <b>FUNCTION</b>                                                                                                                                                                                                                    | <b>MECHANICAL Specs</b>                                                                   |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|  | <p>Bidirectional single-ended connectors. Factory direction is Output. (high impedance state). External 50Ω termination required when using the connector as input.</p> <p><b>ELECTRICAL Specs</b></p> <p>See <b>Tab. 5.1.</b></p> | <p>Series: 00 LEMO Connectors.</p> <p>Type: EPY.00.250.NTN.</p> <p>Manufacturer: LEMO</p> |

|                                                                                   |                                                                                                                                                                                                                                    |                                                                                           |

**0, 1, 2, ..., 7 LEDs**

| <b>FUNCTION</b>                                                                 | <b>COLOR</b> |

|---------------------------------------------------------------------------------|--------------|

| The status of these LEDs is user-programmable                                   | Green.       |

| NOTE: when the UFGPA is in Factory mode, odd and even LEDs alternatively blink. |              |

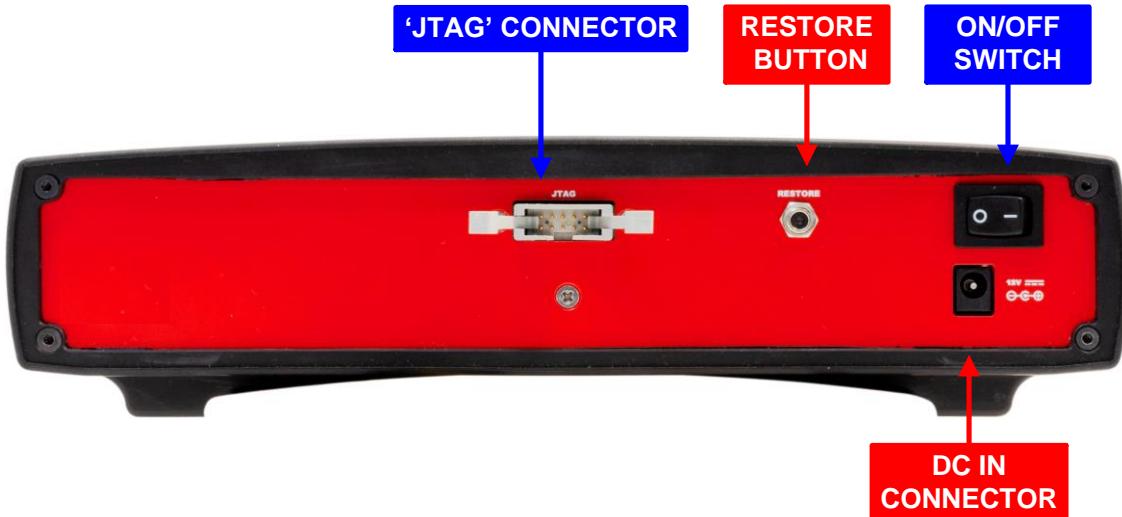

## 4.2 Rear Panel

| JTAG CONNECTOR                                                                    |                                                                                                                           |                                                                                                                            |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|  | <p><b>FUNCTION</b><br/>This connector allows for on-the-fly FPGA programming.</p> <p><b>ELECTRICAL Specs</b><br/>N.A.</p> | <p><b>MECHANICAL Specs</b><br/>Series: 4600 - panel rectangular connectors.<br/>Type: 4610-6350.<br/>Manufacturer: 3M.</p> |

| RESTORE BUTTON                                                                     |                                                                                                                                                             |                                                                                                                                 |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|  | <p><b>FUNCTION</b><br/>Restores the default IP address and forces the module in factory state (see Sec. 9.3.1).</p> <p><b>ELECTRICAL Specs</b><br/>N.A.</p> | <p><b>MECHANICAL Specs</b><br/>Series: 9000 - momentary pushbutton switches.<br/>Type: APR9433NA-O.<br/>Manufacturer: Apem.</p> |

| JTAG CONNECTOR                                                                      |                                                                                                                                                                                |                                                                                                               |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|  | <p><b>FUNCTION</b><br/>Input connector for the DT5495 main power supply from the external AC/DC adaptor.</p> <p><b>ELECTRICAL Specs</b><br/>Input voltage: +12 VDC (typ.).</p> | <p><b>MECHANICAL Specs</b><br/>Series: DC power Jacks.<br/>Type: KLDX-0202-A-LT.<br/>Manufacturer: KYCON.</p> |

| ON/OFF SWITCH                                                                       |                                                                                                                     |                                                                                                                               |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

|  | <p><b>FUNCTION</b><br/>Power switch of the module:<br/>on (I) / off (O)</p> <p><b>ELECTRICAL Specs</b><br/>N.A.</p> | <p><b>MECHANICAL Specs</b><br/>Series: Power Switches.<br/>Type: Rocker SwitchP (A11131121000)<br/>Manufacturer: Molveno.</p> |

# 5 Technical Specifications

|                                               |                                                                                                                   |                                                                                                                                                                                       |                                                                                          |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|

| DT5495 Motherboard                            |                                                                                                                   |                                                                                                                                                                                       |                                                                                          |  |

| <b>FORM FACTOR</b>                            |                                                                                                                   | Desktop module                                                                                                                                                                        |                                                                                          |  |

| <b>I/O SECTIONS A and B</b>                   | <b>Nr. of Channels</b><br>32                                                                                      | <b>Logic</b><br>Direct                                                                                                                                                                | <b>Bandwidth</b><br>200 MHz                                                              |  |

|                                               | <b>Direction</b><br>Input                                                                                         | <b>Signal</b><br>Differential LVDS/ECL/PECL<br>(single ended TTL optional)<br>$Z_{diff}$ : 100 $\Omega$<br>Extended Common Mode<br>Input range: -4V to +5V<br>Fail Safe input feature | <b>Front Panel Connector</b><br>Robinson Nugent P50E-068-P1-SR1-TG<br>type, (34+34) pins |  |

| <b>I/O SECTION C</b>                          | <b>Nr. of Channels</b><br>32 channels                                                                             | <b>Logic</b><br>Direct                                                                                                                                                                | <b>Bandwidth</b><br>250 MHz                                                              |  |

|                                               | <b>Direction</b><br>Output                                                                                        | <b>Signal</b><br>Differential LVDS<br>Require 100 $\Omega$ termination                                                                                                                | <b>Front Panel Connector</b><br>Robinson Nugent P50E-068-P1-SR1-TG<br>type, (34+34) pins |  |

| <b>I/O SECTION G</b>                          | <b>Nr. of Channels</b><br>2                                                                                       | <b>Logic</b><br>TTL IN = Direct<br>TTL OUT = Direct<br>NIM IN = Invert<br>NIM OUT = Direct                                                                                            | <b>Bandwidth</b><br>250 MHz                                                              |  |

|                                               | <b>Direction</b><br>I/O (default is Output)<br>External 50 $\Omega$ termination<br>required when used as<br>input | <b>Signal</b><br>Single ended NIM/TTL<br>selectable                                                                                                                                   | <b>Front Panel Connector</b><br>LEMO 00                                                  |  |

| <b>GATE and DELAY<br/>GENERATOR</b>           | <b>Minimum Delay/Gate</b>                                                                                         | <b>Min.</b><br>9.6 ns                                                                                                                                                                 | <b>Typ.</b><br>10.7 ns                                                                   |  |

|                                               | <b>Maximum Delay/Gate</b>                                                                                         | 631 $\mu$ s                                                                                                                                                                           | 701.2 $\mu$ s                                                                            |  |

| <b>Maximum channel-to-channel spread:</b> 20% |                                                                                                                   |                                                                                                                                                                                       |                                                                                          |  |

| <b>COMMUNICATION<br/>INTERFACE</b>            | <b>ETHERNET</b><br>10/100T                                                                                        | <b>USB</b><br>USB 2.0 compliant                                                                                                                                                       |                                                                                          |  |

| <b>POWER REQUIREMENTS</b>                     | 750 mA (max.) @ +12VDC<br>AC-DC 12V-45W power unit included                                                       |                                                                                                                                                                                       |                                                                                          |  |

Tab. 5.1: DT5495 specifications table

|                           |                                                                              |                                                                                                                                                                                       |                                                                                          |

|---------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| A395A Mezzanine Board     |                                                                              |                                                                                                                                                                                       |                                                                                          |

| <b>I/O SECTION</b>        | <b>Nr. Of Channels</b><br>32                                                 | <b>Logic</b><br>Direct                                                                                                                                                                | <b>Bandwidth</b><br>200 MHz                                                              |

|                           | <b>Direction</b><br>Input                                                    | <b>Signal</b><br>Differential LVDS/ECL/PECL<br>(single ended TTL optional)<br>$Z_{diff}$ : 100 $\Omega$<br>Extended Common Mode<br>input range: -4V to +5V<br>Fail Safe input feature | <b>Front Panel Connector</b><br>Robinson Nugent P50E-068-P1-SR1-TG<br>type, (34+34) pins |

| <b>POWER CONSUMPTIONS</b> | 0.1 A (max) @ +5V internal rail<br>+12V and -12V internal rails are not used |                                                                                                                                                                                       |                                                                                          |

Tab. 5.2: A395A Mezzanine specifications table

| <b>A395B Mezzanine Board</b> |                                                                              |                                                                         |                                                                                       |

|------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| <b>I/O SECTION</b>           | <b>Nr. of Channels</b><br>32                                                 | <b>Logic</b><br>Direct                                                  | <b>Bandwidth</b><br>250 MHz                                                           |

|                              | <b>Direction</b><br>Output                                                   | <b>Signal</b><br>Differential LVDS<br>Requires 100 $\Omega$ termination | <b>Front Panel Connector</b><br>Robinson Nugent P50E-068-P1-SR1-TG type, (34+34) pins |

| <b>POWER CONSUMPTIONS</b>    | 0.1 A (max) @ +5V internal rail<br>+12V and -12V internal rails are not used |                                                                         |                                                                                       |

Tab. 5.3: A395B Mezzanine specifications table

| <b>A395C Mezzanine Board</b> |                                                                              |                                   |                                                                                       |

|------------------------------|------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------|

| <b>I/O SECTION</b>           | <b>Nr. of Channels</b><br>32                                                 | <b>Logic</b><br>Direct            | <b>Bandwidth</b><br>300 MHz                                                           |

|                              | <b>Direction</b><br>Output                                                   | <b>Signal</b><br>Differential ECL | <b>Front Panel Connector</b><br>Robinson Nugent P50E-068-P1-SR1-TG type, (34+34) pins |

| <b>POWER CONSUMPTIONS</b>    | 1.4 A (max) @ +5V internal rail<br>+12V and -12V internal rails are not used |                                   |                                                                                       |

Tab. 5.4: A395C Mezzanine specifications table

| <b>A395D Mezzanine Board</b> |                                                                              |                                                                             |                                         |

|------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------|

| <b>I/O SECTION</b>           | <b>Nr. of Channels</b><br>8                                                  | <b>Logic</b><br>Direct                                                      | <b>Bandwidth</b><br>250 MHz             |

|                              | <b>Direction</b><br>I/O selectable                                           | <b>Signal</b><br>selectable TTL/NIM:<br>TTL IN = Direct<br>TTL OUT = Direct | <b>Front Panel Connector</b><br>LEMO 00 |

|                              | <b>Impedance</b><br>Selectable 50 $\Omega$ /high-Z<br>by on-board jumper     | <b>NIM IN</b> = Invert<br><b>NIM OUT</b> = Direct                           |                                         |

| <b>POWER CONSUMPTIONS</b>    | 1.1 A (max) @ +5V internal rail<br>+12V and -12V internal rails are not used |                                                                             |                                         |

Tab. 5.5: A395D Mezzanine specifications table

| <b>A395E Mezzanine Board</b> |                                                                              |                                                                                              |                                         |

|------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------|

| <b>I/O SECTION</b>           | <b>Nr. of Channels</b><br>8                                                  | <b>Logic</b><br>Analog                                                                       | <b>Bandwidth</b><br>n.a.                |

|                              | <b>Direction</b><br>Output                                                   | <b>Signal</b><br>16-bit resolution<br>$\pm 5V$ @10k $\Omega$ RL<br>$\pm 4V$ @200 $\Omega$ RL | <b>Front Panel Connector</b><br>LEMO 00 |

| <b>POWER CONSUMPTIONS</b>    | 0.3 A (max) @ +5V internal rail<br>+12V and -12V internal rails are not used |                                                                                              |                                         |

Tab. 5.6: A395E Mezzanine specifications table

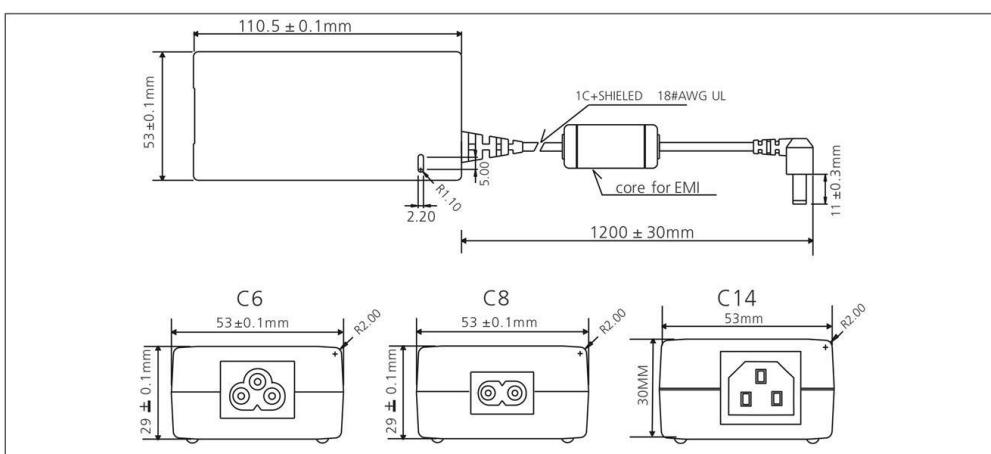

# 6 Power Requirements

The DT5495 is powered by the external 45W 12V AC/DC stabilized power supply unit included in the delivered kit (see Chap. Errore. L'origine riferimento non è stata trovata.). The maximum required current is typically 500mA (without any mezzanine extension).

## Switchbox FRA030/045/050 Series

**30 - 50 W SINGLE OUTPUT AC/DC DESKTOP ADAPTOR**

**Features**

- Universal input

- IEC320 receptacle 2P or 3P

- Optional output connector

- OVP, OCP, OPP, auto recovery

- CEC compliance

**Specifications**

| <b>INPUT</b>            |                                          |

|-------------------------|------------------------------------------|

| Voltage range           | 100-240VAC.                              |

| Inrush current          | 40A at 115VAC / 80A at 230VAC max.       |

| Dielectric withstand    | Input/output 3,000VDC.                   |

| <b>OUTPUT</b>           |                                          |

| Output voltage          | 5-48V                                    |

| Ripple and noise        | 2% p-p max.                              |

| Load regulation         | ±5% max.                                 |

| No load stand by power  | <0.5W @ 230VAC.                          |

| Efficiency              | >=85% for CEC requirement.               |

| Hold up time            | 10ms at nominal line.                    |

| Protections             | OCP, OVP, over power & short circuit.    |

| <b>GENERAL</b>          |                                          |

| Std output connector    | Dc barrel jack.                          |

| Std output cable/length | UL1185, #18AWG / 5 ft.                   |

| <b>ENVIRONMENTAL</b>    |                                          |

| Operating temperature   | 0°C to +40°C.                            |

| Storage temperature     | -20°C to +85°C.                          |

| <b>STANDARDS</b>        |                                          |

| Safety standards        | IEC/UL/EN60950-1, CE, CB.                |

| EMC                     | EN55022 (CISPR 22) class B, FCC class B. |

**Note:**

X = Inlet type code

X = 4, IEC320 C14      X = 6, IEC320 C6      X = 8, IEC320 C8

\*CEC compliance model provide under customer's request.

\*CEC compliance model standby power (@ no load) <0.5W.

**powerbox**

[www.powerbox.info](http://www.powerbox.info)

20081029

21

UM6508 – DT5495 User Manual rev. 5

## 7 Packaging and Compliancy

The DT5495 board is available in a desktop form factor.

The device is inspected by CAEN before shipment, and it is guaranteed to leave the factory free of mechanical or electrical defects.

The content of the delivered package standardly consists of the part list shown in the table below.

|                                                                                     | Part                                                                  | Description                                     | Qt |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------|----|

|    | DT5495<br>(with or without mezzanine board extension <sup>(1)</sup> ) | <b>Programmable Logic Unit</b>                  | x1 |

|    | USB cable                                                             | <b>USB-2.0 cable, type A to mini-USB, L=1mt</b> | x1 |

|   | Ethernet cable                                                        | <b>Cat6 SSTP Ethernet cable assembly RJ45</b>   | x1 |

|  | Documentation                                                         | <b>UMS175 - V2495 PLU User Manual</b>           | -  |

**Tab. 7.1:** Delivered kit content

<sup>(1)</sup> Mezzanine boards are available by ordering option (refer to **Tab. 1.2**).

**CAUTION:** to manage the product, consult the operating instructions provided.

When receiving the unit, the user is strictly recommended to:

- Inspect containers for damage during shipment. Report any damage to the freight carrier for possible insurance claims.

- Check that all the components received match those listed on the enclosed packing list as in **Tab. 7.1**. (CAEN cannot accept responsibility for missing items unless we are notified promptly of any discrepancies.)

- Open shipping containers; be careful not to damage contents.

- Inspect contents and report any damage. The inspection should confirm that there is no exterior damage to the unit such as broken knobs or connectors and that the front panel and display face are not scratched or cracked. Keep all packing material until the inspection has been completed.

- If damage is detected, file a claim with the carrier immediately and notify CAEN service.

- If equipment must be returned for any reason, carefully repack equipment in the original shipping container with original packing materials if possible. Please, contact CAEN service.

- If equipment is to be installed later, place equipment in the original shipping container and store it in a safe place until ready to install.

**DO NOT SUBJECT THE ITEM TO UNDUE SHOCK OR VIBRATIONS**

**DO NOT BUMP, DROP OR SLIDE SHIPPING CONTAINERS**

**DO NOT LEAVE ITEMS OR SHIPPING CONTAINERS UNSUPERVISED IN AREAS WHERE PERSONNEL UNTRAINED MAY MISHANDLE THE ITEMS**

**USE ONLY ACCESSORIES WHICH MEET THE MANUFACTURER'S SPECIFICATIONS**

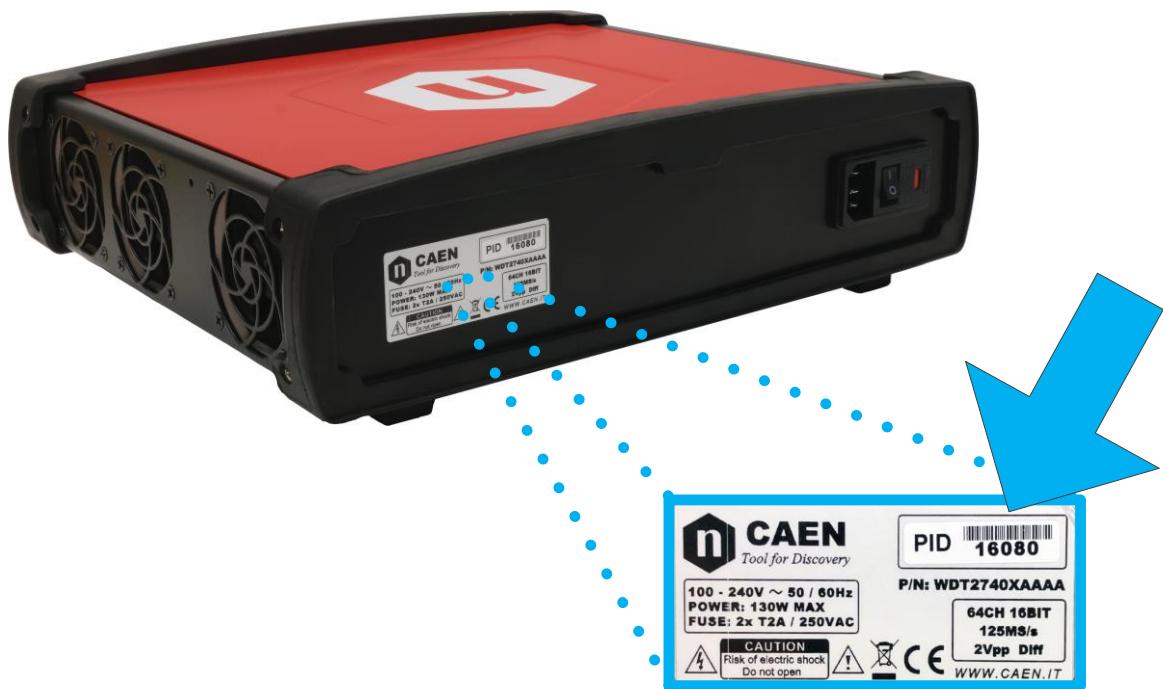

## 8 PID (Product Identifier)

PID is the CAEN product identifier, an incremental number greater than 10000 that is unique for each product. The PID is on a label affixed to the product (Fig. 8.1), it is even stored in an on-board non-volatile memory (Sec. 11.1.3), and readable by CAEN toolbox software (Sec. 10.4.1).

Fig. 8.1: PID location on the desktop device (the number in the picture is purely indicative)

# 9 Getting Started with DT5495

## 9. Expansion Mezzanines

Four different type of mezzanine boards are available by ordering option to extend the DT5495 functions (Tab. 1.2).

Fig. 9.1: DT5495 motherboard with mezzanine boards

### 9.1 Mezzanine Installation

Users who need to install one or more A395x-series mezzanine board on the DT5495 can follow the instructions in the dedicated Guide [RD5] or look at the tutorial video on the product web page.

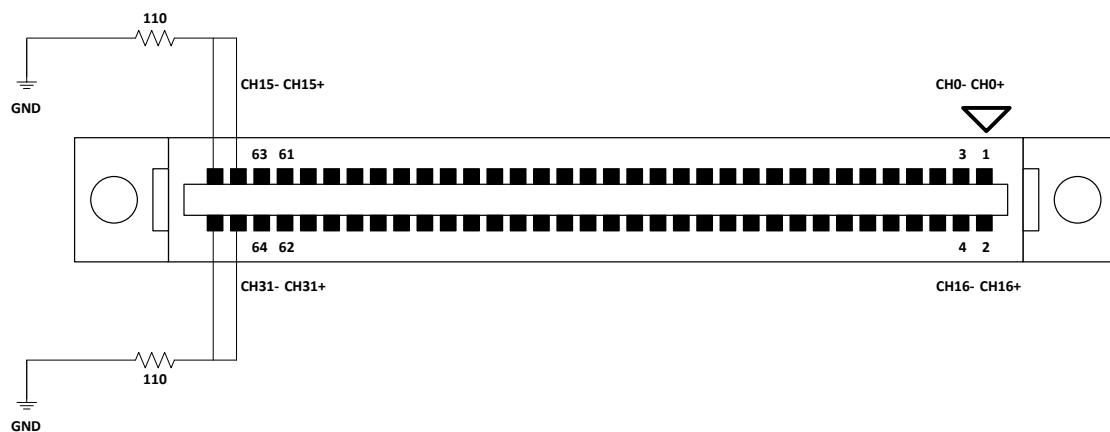

### 9.2 Front Panel Connector Cabling

Motherboard I/O sections A, B, C and A395A, A395B and A395C mezzanine boards feature the Robinson Nugent P50E-068-P1-SR1-TG multi-pin connector (see Chap. 4), whose pin layout is shown in Fig. 9.2.

Fig. 9.2: Multi-pin connector pin assignment

The CAEN A967 Cable Adapter (Fig. 9.3) allows to adapt each Robinson Nugent multi-pin connector into two 1" 17+17-pin Header-type male connectors (3M, 4634-7301) with locks through two 25 cm long flat cables. Refer to the cable datasheet [RD2] for specifications and to Tab. 1.2 for the ordering option.

Fig. 9.3: CAEN A967 Cable Adapter

## 9.3 Power-on Configuration Sequence

When the board is powered on, the on-board programmable devices are configured with the firmware images stored in their dedicated flash memories. If all programmable devices (MFPGA, UFPGA and GDG) are correctly configured, the CFG LED is lit on. In case an anomaly occurs, the CFG LED status can be:

- 1) BLINKING: the FPGAs are configured, but the Main FPGA remained in Factory mode.

The MFPGA can be configured by two kind of firmware images which are stored on the dedicated flash memory: the Factory firmware and the Application firmware. The Factory firmware is a basic firmware specifically intended for boot and recovery functions. The Application firmware is the standard operating firmware and can be upgraded by the user through the Ethernet or the USB interface.

At power-on, the MFPGA configures itself with the Factory firmware image and subsequently attempts to load the Application firmware. If the application firmware is missing or corrupted, the MFPGA will remain in the factory mode. The Factory firmware guarantees the communication with the board and allows the MFPGA Application firmware upgrade.

- 2) OFF: one or more FPGAs may not have been configured.

In case of a MFPGA configuration issue, an attempt to force the MFPGA in Factory mode can be performed by the Restore button (see next paragraph). If the CFG LED starts blinking, an application firmware upgrade can be attempted.

### 9.3.1 Restore Function

The Restore button on the DT5495 rear panel (see [Fig. 4.1](#)) allows to:

- Reset the board to the default IP address: 192.168.0.90. The IP can anytime be changed by the Web Interface (see [Sec. 10.3](#))

- Force the board in the Factory firmware of the Main FPGA.

Use the button in two alternative modes:

1. Hold the button down (with a pen tip, for example).

- 2a. Power cycle the DT5495, then wait for less than 5 seconds; this mode only forces the boot from the factory Main FPGA firmware, while the ethernet IP address of the board is not affected.

- 2b. Power cycle the DT5495, then wait for at least 15 seconds; this way, both the IP address is restored to the default value and the board is forced to boot from the factory Main FPGA firmware.

3. Release the button.

4. Power cycle the DT5495 again.

In factory mode, the CFG LED starts blinking (see the CFG description in [Chap. 4](#)). Use the Web Interface with ethernet connection to 192.168.0.90 for check in case of IP address change ([Sec. 10.3](#)).

# 10 Driver and Software Installation

## 10.1 Drivers

To communicate with the board using one of the available communication buses, specific drivers should be installed on your host device.

**Note:** to ensure the best system performance, it is recommended to have always the latest drivers release installed.

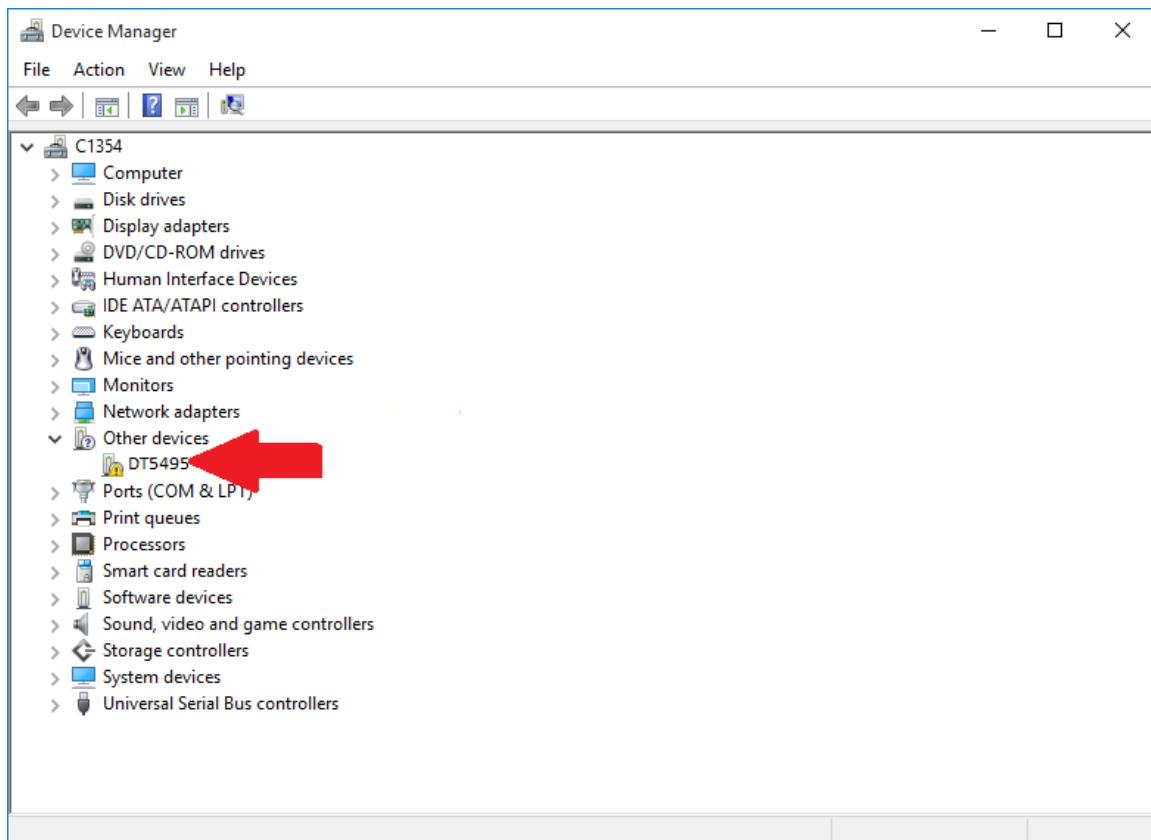

### 10.1.1 Direct USB Driver

In order to communicate with the DT5495 through the front panel USB interface (see Chap. 4), the related driver is available for free download at the DT5495 *Downloads* page on CAEN web site (**login required**).

#### ➤ WINDOWS OS

A step-by-step driver installation procedure is given next.

**Note:** The procedure is based on a Windows 10 system. It may be slightly different for other Windows OSs.

1. Download and unpack the driver installation package on the host PC.

2. Plug the USB cable on the DT5495 and on the PC. Windows should detect the new hardware.

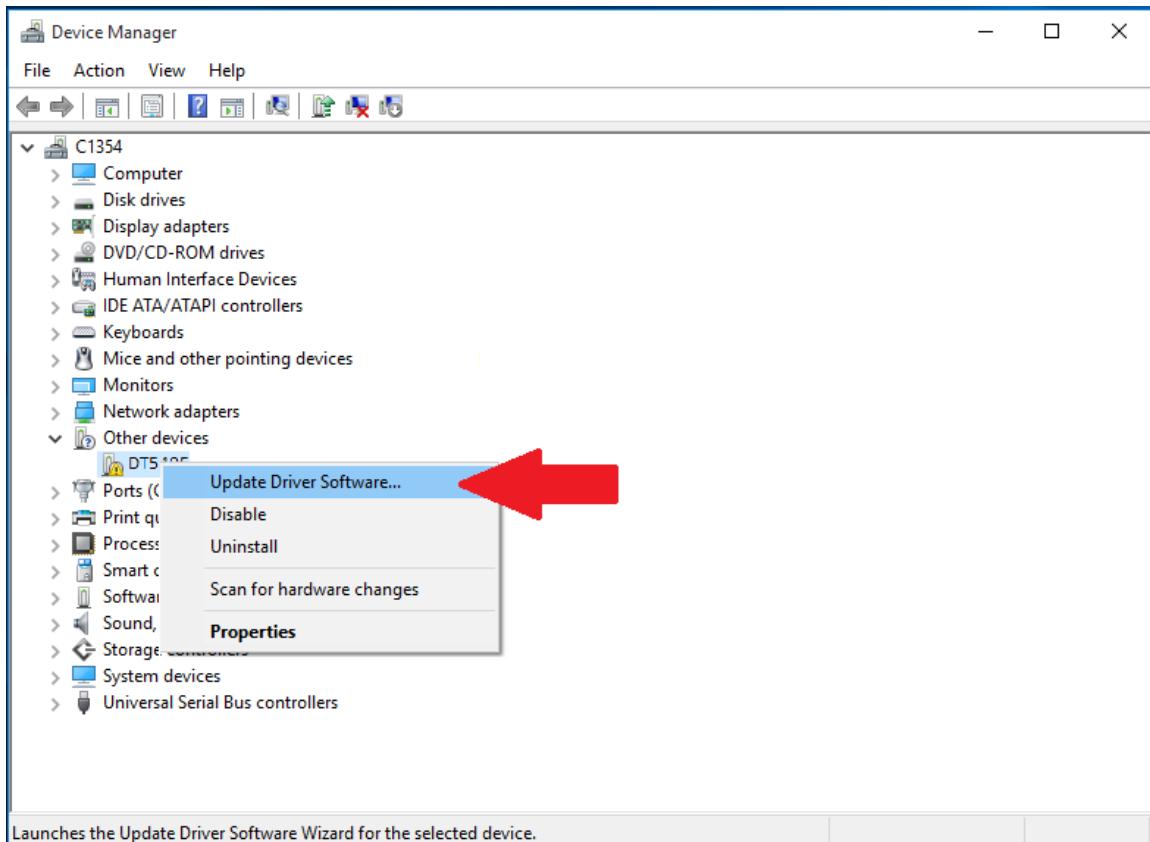

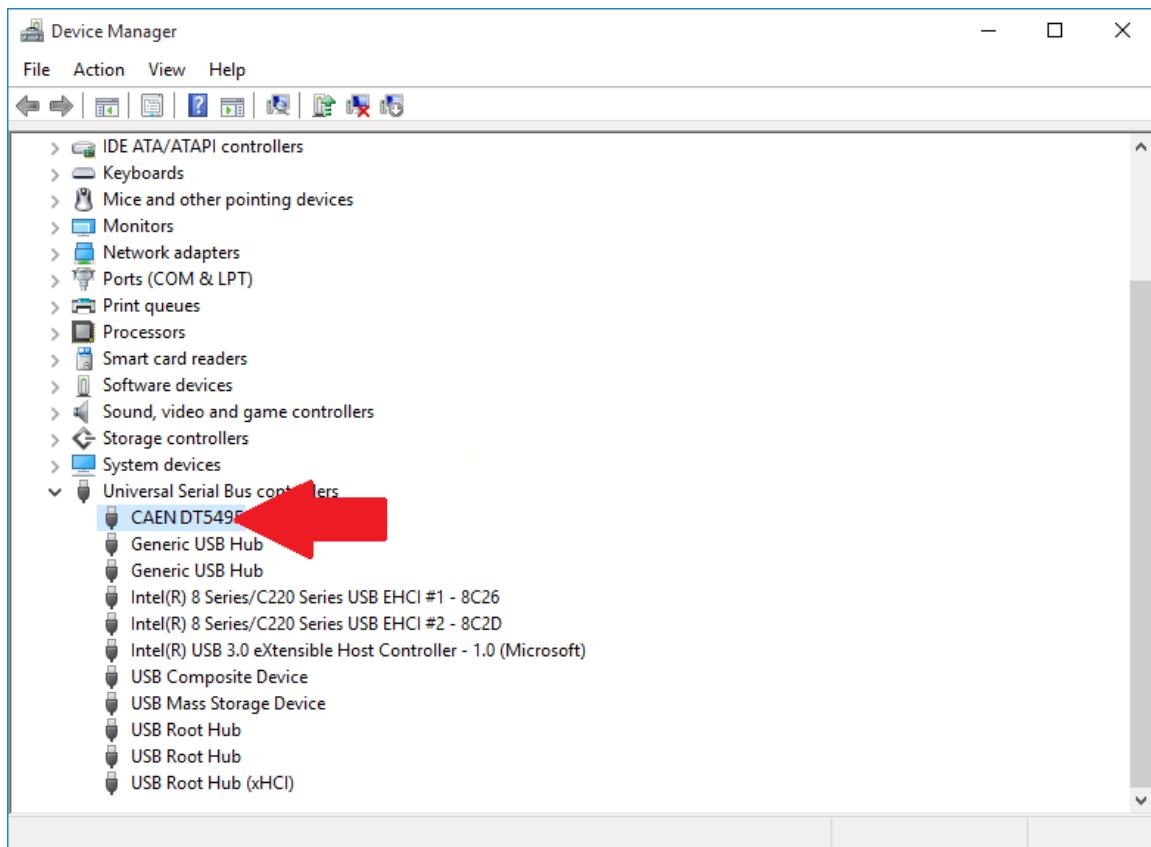

3. Go to the *Device Manager* area; the new hardware is listed in *Other devices* as “DT5495” (see **Fig. 2.1**).

**Fig. 10.1:** DT5495 hardware detection

4. Right click on "DT5495" item and select *Update Driver Software* option in the slide menu.

**Fig. 10.2:** USB driver manual installation: Step1

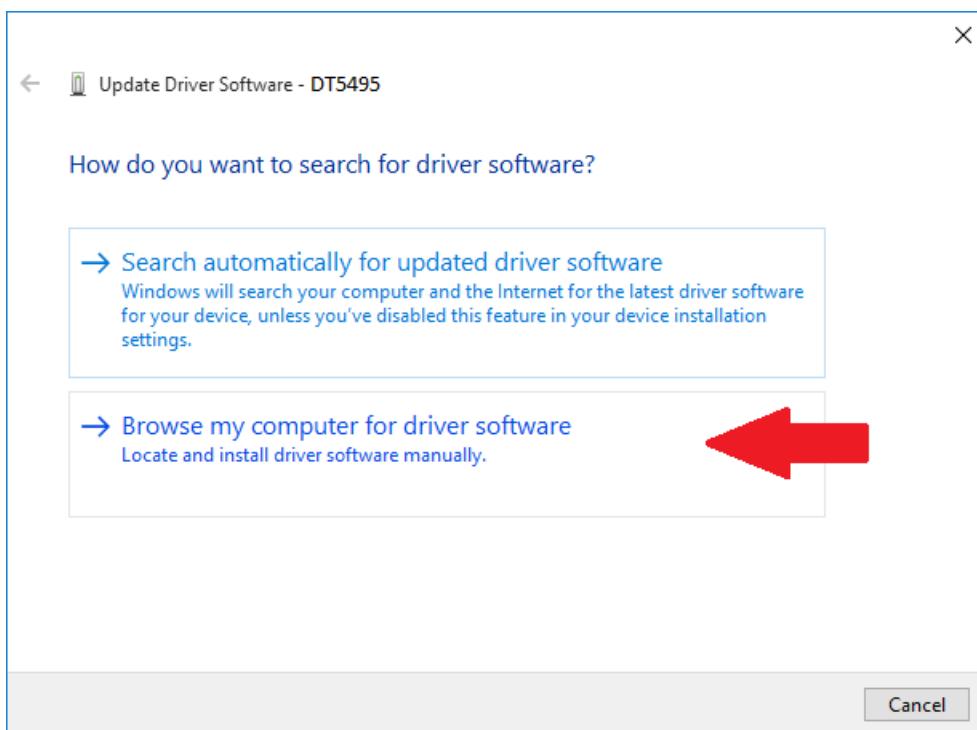

5. Select *Browse my computer for driver software* as in **Fig. 10.3.**

**Fig. 10.3:** USB driver manual installation: Step2

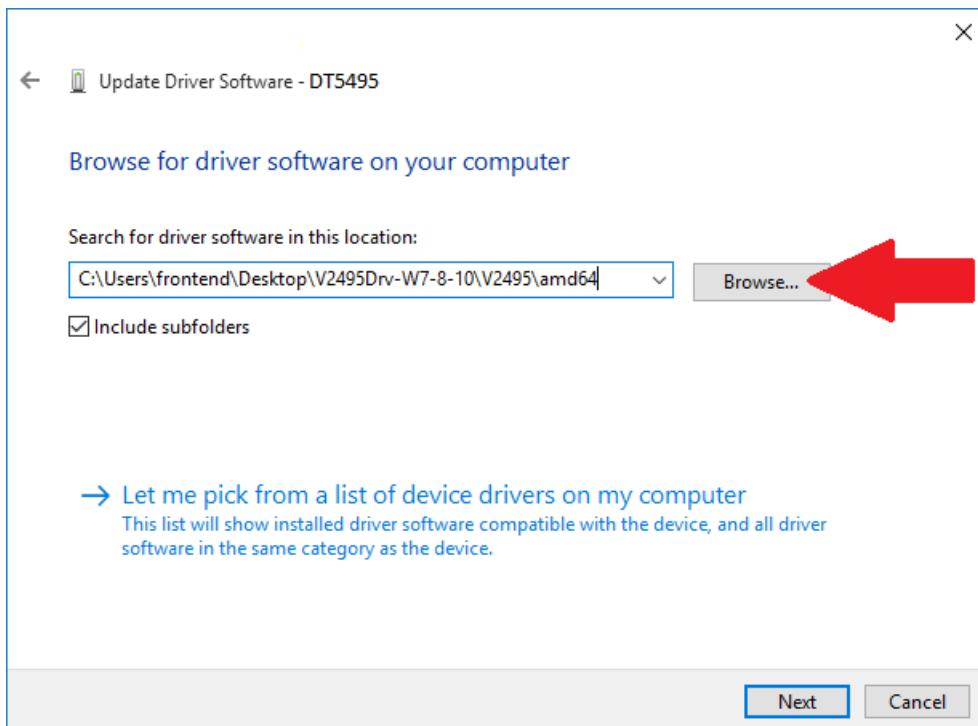

6. Use the [Browse] button to point to the driver folder in the destination path on the host PC, then click the [Next] button.

Fig. 10.4: USB driver manual installation: Step3

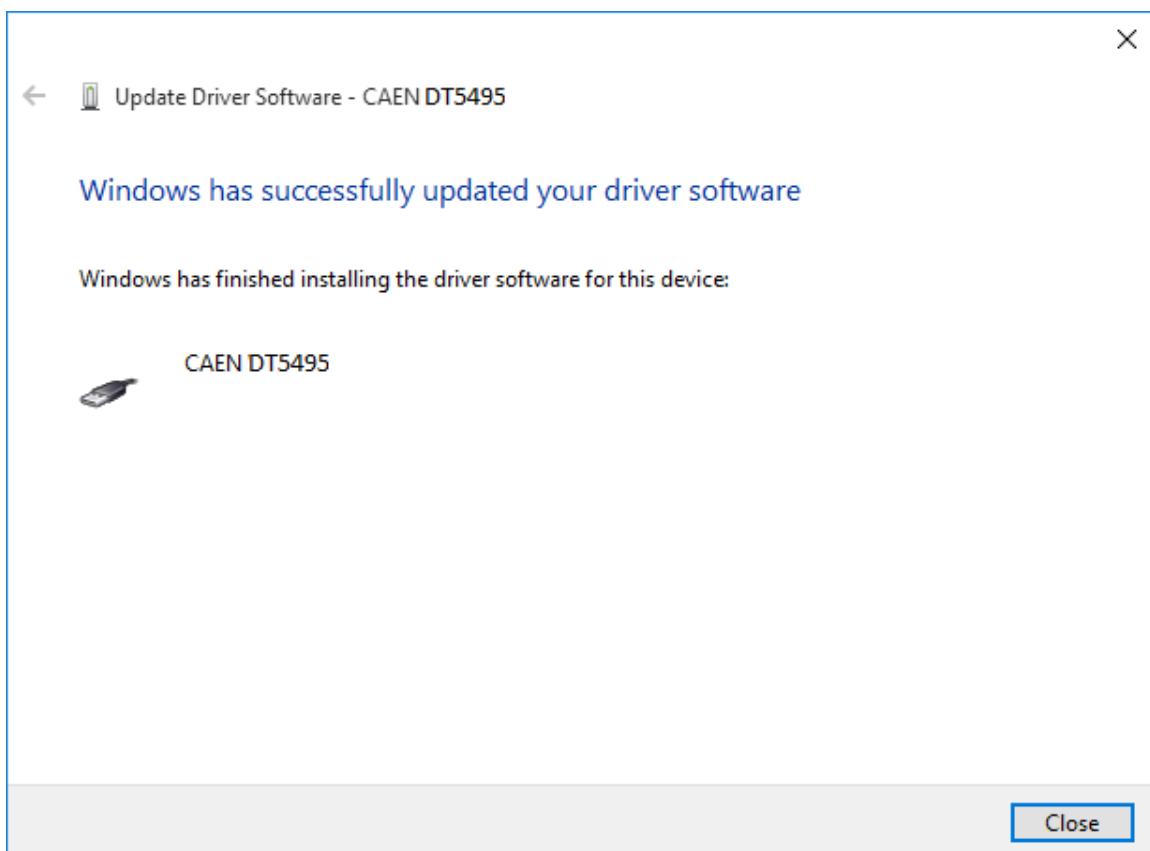

7. Click the [Close] button at the end of the installation process.

Fig. 10.5: USB driver manual installation: Step4

8. Check that the “CAEN DT5495” item appears in the *Universal Serial Bus controllers* list.

Fig. 10.6: USB driver manual installation: Step5

➤ **Linux OS**

DT5495 is fully supported by Linux kernels from kernel version 3.13 on. This means that such kernel versions should be able to recognize the hardware automatically, without requiring the user to install any driver.

**Note:** The in-Linux drivers don't automatically give to the user the rights to directly connect to the board. It is then recommended to authenticate as root or to enable the low-level user rights before to try any communication by software.

## 10.2 Ethernet Configuration

1. Connect the Ethernet cable between Hexagon and the PC.

2. Configure the Ethernet network of your PC in the following steps.

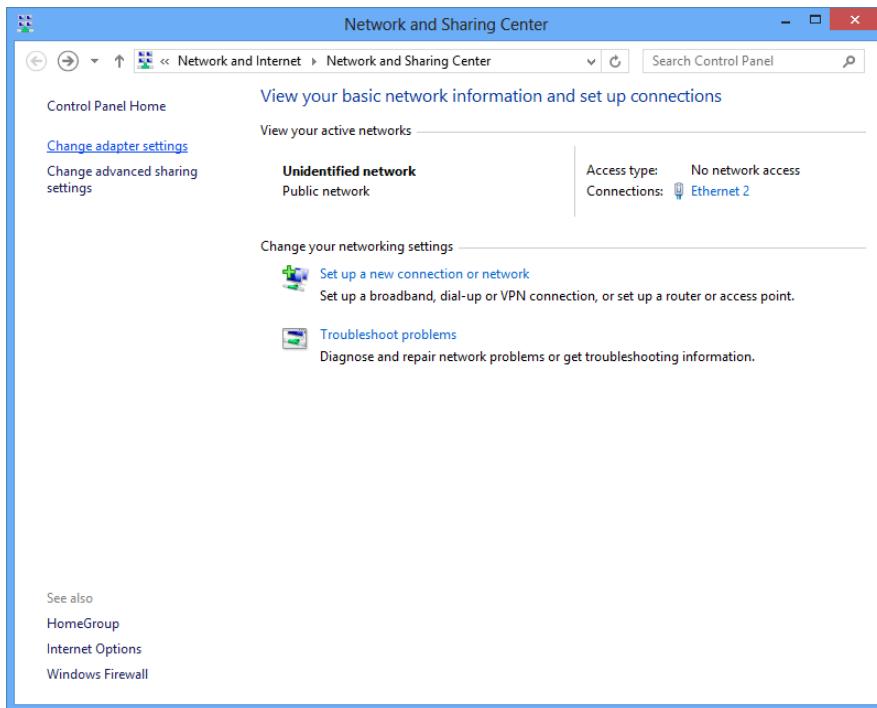

- a. Open the path: *Control Panel - Network and Internet - Network and Sharing Center* (Errore. L'origine riferimento non è stata trovata.).

**Fig. 10.7:** The Network and Sharing Center window

- b. Click on "Change adapter settings".

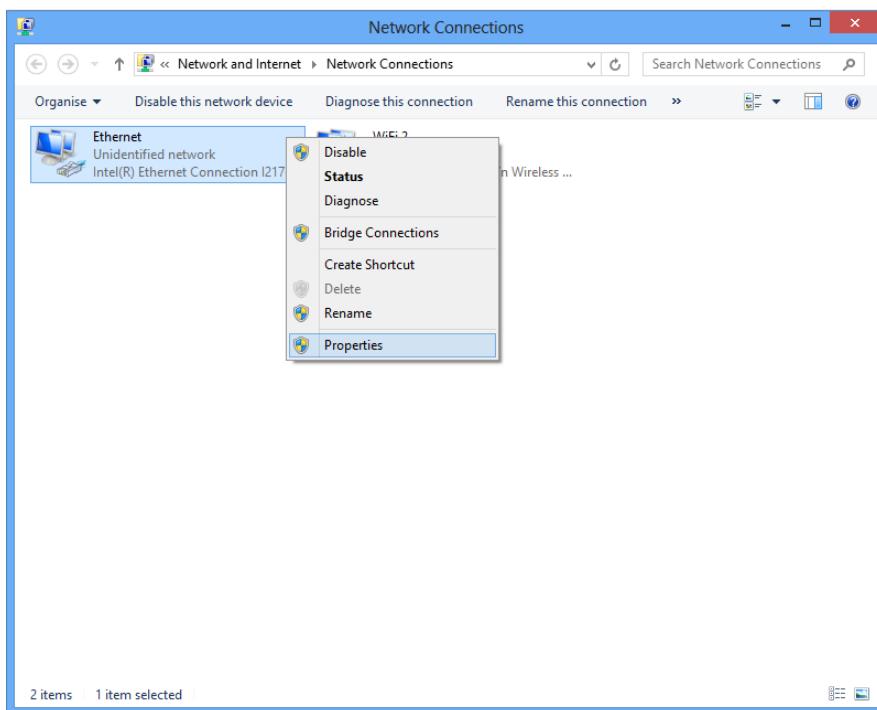

- c. Right click on the Ethernet icon and select "Properties" from the slide menu (Fig. 10.8).

**Fig. 10.8:** Properties window of the Ethernet network

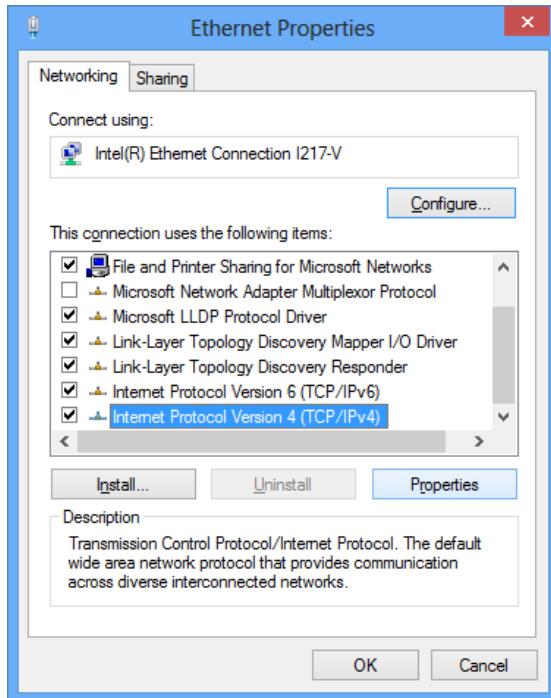

- d. Click on "Internet Protocol Version (TCP/IPv4)", and select "Properties" (Fig. 10.9).

**Fig. 10.9:** Ethernet Properties window"

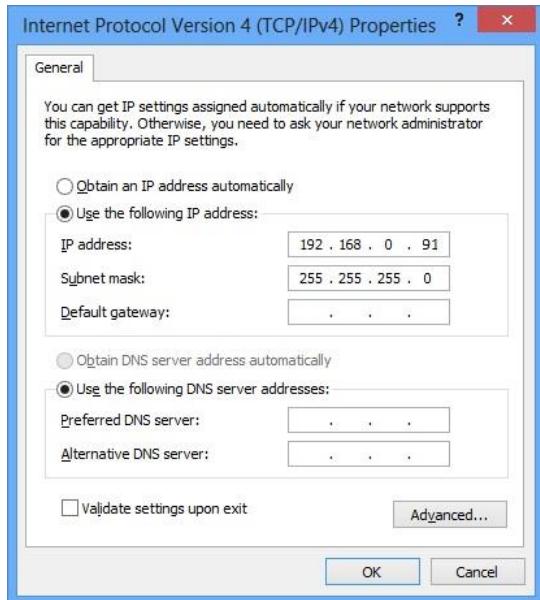

- e. Copy the configuration as in Fig. 10.10 on the "Internet Protocol Version (TCP/IPv4) Properties" window.

**Fig. 10.10:** Properties window of the "Internet Protocol Version (TCP/IPv4)"

**Note:** Considering the factory default IP address of Hexagon is 192.168.0.90, use for the Network settings of the PC the same first three IP Address numbers of the Hexagon IP, while make sure to set the fourth decimal number to a value different from the Hexagon one to avoid IP conflicts over the net.

It is finally possible to connect to Hexagon by the Web Interface described in the next section (Sec. 10.3).

## 10.3 Web Interface

**Note:** Check that the DT5495 is powered on, the Ethernet cable is connected, and the Network is set according to Sec. 10.2.

Open the web browser and type the DT5495 IP Address as web address. In the default case, the IP Address is 192.168.0.90:

*http://192.168.0.90*

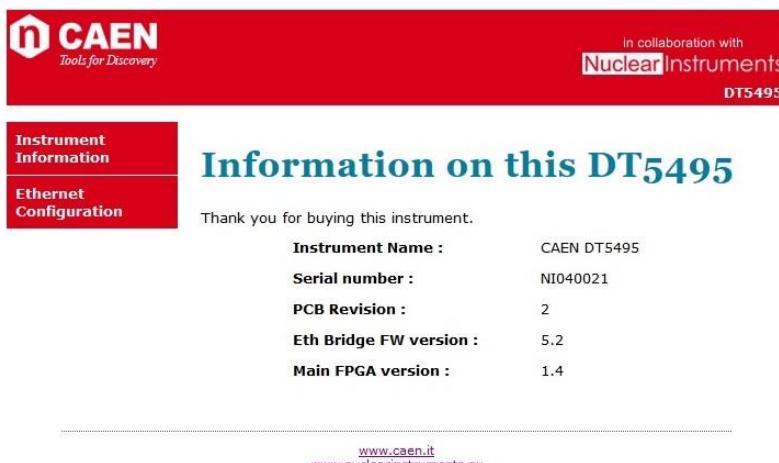

The Web Interface will enter the “Instrument Information” page (Fig. 10.11).

Instrument Information

Ethernet Configuration

Information on this DT5495

Thank you for buying this instrument.

|                         |             |

|-------------------------|-------------|

| Instrument Name :       | CAEN DT5495 |

| Serial number :         | NI040021    |

| PCB Revision :          | 2           |

| Eth Bridge FW version : | 5.2         |

| Main FPGA version :     | 1.4         |

[www.caen.it](http://www.caen.it)

[www.nuclearinstruments.eu](http://www.nuclearinstruments.eu)

Fig. 10.11: Instrument Information page of the DT5495 Web Interface

Information includes the name, the serial number, the PCB revision, the revision of the Ethernet Bridge and the Main FPGA firmware version.

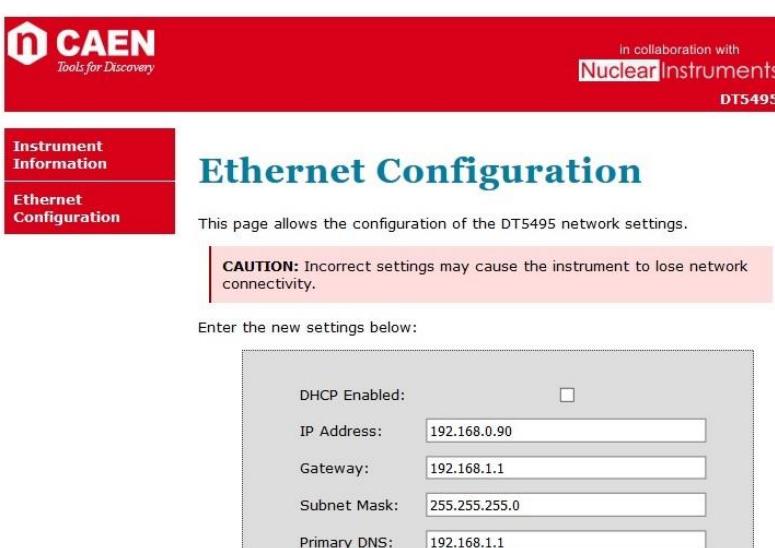

Selecting “Ethernet Configuration”, the Web Interface shows the page where the ethernet settings can be changed by the user.

Instrument Information

Ethernet Configuration

This page allows the configuration of the DT5495 network settings.

**CAUTION:** Incorrect settings may cause the instrument to lose network connectivity.

Enter the new settings below:

|               |                          |

|---------------|--------------------------|

| DHCP Enabled: | <input type="checkbox"/> |

| IP Address:   | 192.168.0.90             |

| Gateway:      | 192.168.1.1              |

| Subnet Mask:  | 255.255.255.0            |

| Primary DNS:  | 192.168.1.1              |

**Save Config**

[www.caen.it](http://www.caen.it)

[www.nuclearinstruments.eu](http://www.nuclearinstruments.eu)

Fig. 10.12: Instrument Information page of the DT5495 Web Interface

Press the “Save Config” button after modifications and remind to power cycle the board to make the new settings effective.

## 10.4 Software Tools

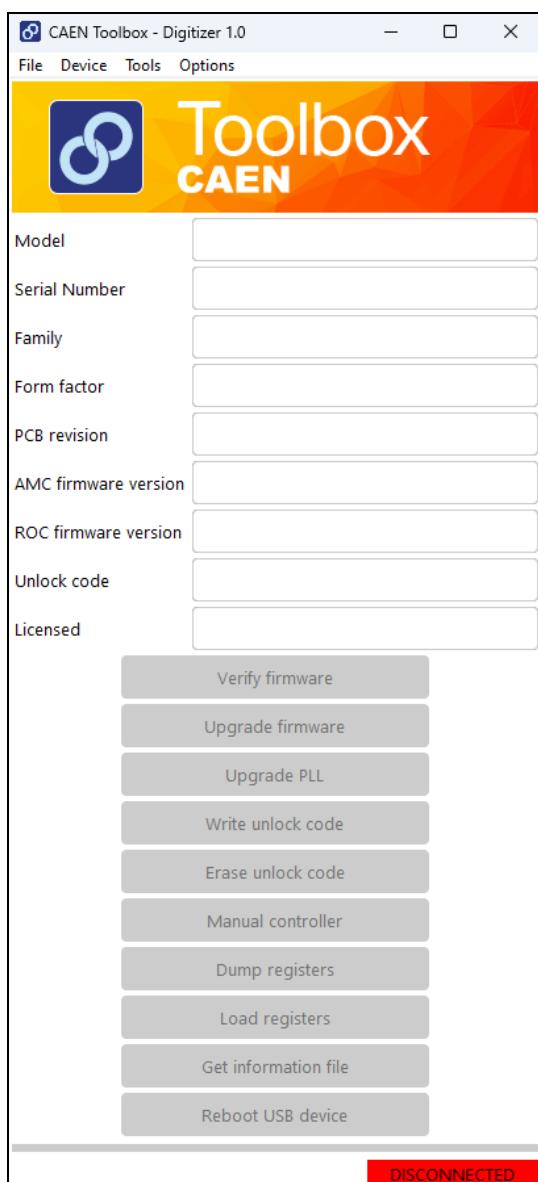

### 10.4.1 CAEN Toolbox

CAEN Toolbox is the comprehensive software suite designed for CAEN Front-End boards.

With V2495, CAEN Toolbox simplifies various tasks into a few easy steps, including:

- Upgrade the MFPGA firmware

- Load the User firmware on the UFGA

- Verify the Main and User FPGA firmware

- Read the release number of the MFPGA firmware

- Store and get the Product Unlock Code in case of paid firmware

- Get the Board Info file (useful in case of support requests)

Fig. 10.13: CAEN Toolbox Graphical User Interface

CAEN Toolbox runs on Windows® and Linux® platforms. The software is stand-alone on both the available versions.

Refer to the CAEN Toolbox documentation for installation instructions and a detailed description [RD1]

#### 10.4.2 PLULib Library

CAEN PLULib library is a library of C functions developed to control V2495 and DT5495 programmable logic units through direct USB and Ethernet communication interfaces, but also through the VMEbus connection by using CAEN Bridges, if supported.

The library includes a simple demo application, which is not intended for the board readout, but rather to automatically test the library functions. The user can then inspect the code as reference for his customized software development based on the PLU library.

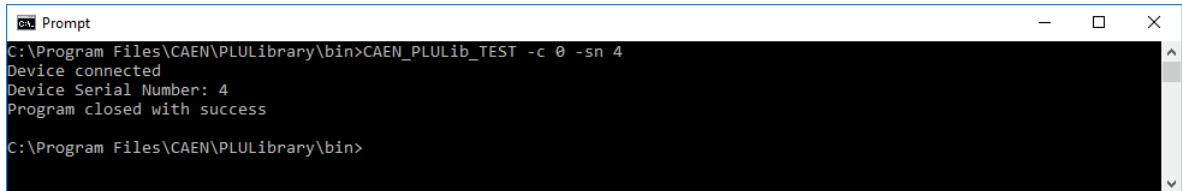

```

C:\Program Files\CAEN\PLULibrary\bin>CAEN_PLULib_TEST -c 0 -sn 4

Device connected

Device Serial Number: 4

Program closed with success

C:\Program Files\CAEN\PLULibrary\bin>

```

**Fig. 10.14:** CAEN PLULib Demo application prompt

CAEN PLULib library can operate on Windows® and Linux®, 32 and 64-bit, and requires the CAENComm library to be installed. The documentation [RD3] and installation packages are available for free download at the PLULib *Downloads* page on CAEN web site ([login required](#)).

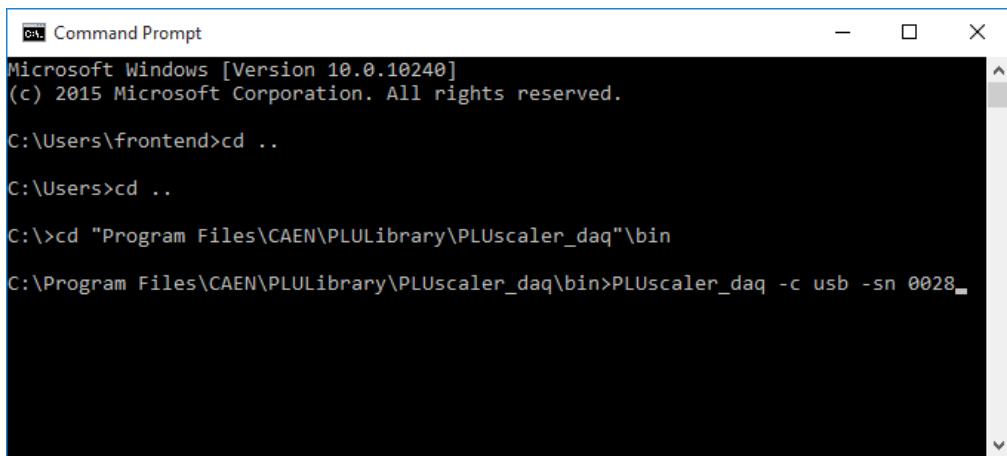

#### 10.4.3 PLUscaler\_daq

PLUscaler\_daq is a CAEN software dedicated to manage data acquisition from DT5495 and V2495 Programmable Logic Unit with the FW2495SC firmware (see Chap. 14). It is a C-based simple application without a graphical user interface which relies on an external configuration text file.

The source code included in the package gives to the user a useful starting point to develop customized software applications.

```

Microsoft Windows [Version 10.0.10240]

(c) 2015 Microsoft Corporation. All rights reserved.

C:\Users\frontend>cd ..

C:\Users>cd ..

C:\>cd "Program Files\CAEN\PLULibrary\PLUscaler_daq"\bin

C:\Program Files\CAEN\PLULibrary\PLUscaler_daq\bin>PLUscaler_daq -c usb -sn 0028

```

**Fig. 10.15:** PLUscaler\_daq prompt

PLUscaler\_daq can operate on Windows® and Linux®, 32 and 64-bit, and requires the PLULib library to be installed. The documentation [RD4] and installation packages packages are available for free download at the FW2495SC *Downloads* page on CAEN web site ([login required](#)).

# 11 Communication Interfaces

The DT5495 board can be accessed via both Ethernet and USB interface. All registers are accessible from both interfaces.

## 11.1 Address Map

The following table illustrates the DT5495 address map:

| Address       | Description                        |

|---------------|------------------------------------|

| 0x0000-0x0FFF | UFPGA data access                  |

| 0x1000-0x7FFF | UFPGA register access              |

| 0x8000-0x80FF | <i>reserved</i>                    |

| 0x8100-0x81FF | Configuration ROM                  |

| 0x8200-0x83FF | Configuration and Status Registers |

| 0x8400-0x84FF | Reserved                           |

| 0x8500-0x86FF | MFPGA flash configuration          |

| 0x8700-0x88FF | UFPGA flash configuration          |

| 0x8900-0x8AFF | GDG flash configuration            |

| 0x8B00-0x8BFF | Reserved                           |

| 0x8C00-0x8FFF | Internal scratch RAM               |

| 0x9000-0xFFFF | <i>reserved</i>                    |

Tab. 11.1: DT5495 register address map

### 11.1.1 User FPGA Data Access (0x0000-0x0FFF)

The UFPGA data access space is allocated specifically for the readout of data produced in the UFPGA logic which need to exploit the maximum readout throughput available. This space can be accessed by using the available block transfer mechanism over the Ethernet or USB communication interfaces.

Block data transfer allows to implement a faster readout. Block transfers requests over Ethernet or USB do not trigger any transfer over the internal local bus between the MFPGA and UFPGA: a data prefetch mechanism, implemented in the MFPGA, stores User data into a local data queue (prefetch data queue). Please, refer to the prefetch mechanism description in Sect **Local Bus Interface**. Consequently, data from the UFPGA data access space are read from the prefetch data queue in the MFPGA.

### 11.1.2 User FPGA Register Access (0x1000-0x7FFF)

UFPGA register address range is allocated for User register read/write.

A read or write transfer (single cycle) can be triggered on the local bus by performing a corresponding read transfer in the 0x1000-0x7FFF address interval.