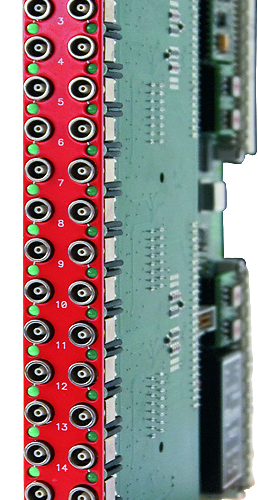

- 16 independent channels programmable as inputs/outputs

- Inputs: Internally / Externally Strobed or Glitched

- Outputs: Transparent or Externally Strobed

- Programmable LAM generator

Digital

I/O Registers

I/O Registers Models

C219

DT5495

-

User Programmable FPGA

-

Compact Desktop form factor

-

Up to 162 inputs, up to 130 outputs

-

LVDS/ECL/PECL/NIM/TTL

-

3 expansion slots for piggyback board:

-

A395A 32 LVDS/ECL/PECL input ch.

-

A395B 32 LVDS output ch.

-

A395C 32 ECL output ch.

-

A395D 8 NIM/TTL input/output ch.

-

A395E 8 Analog output 16bit ch.

-

-

32 independent programmable Gate and Delay Generator

-

Ethernet and Mini-USB 2.0 Connection

-

Available in VME version V2495

-

Supported by SCI-Compiler software tool

V1495

-

User customisable FPGA Unit (with preloaded demo code)

-

LVDS/ECL/PECL inputs (differential)

-

64 inputs, expandable to 162 (with 32 outputs)

-

32 outputs, expandable to 130 (with 64 inputs)

-

405 MHz maximum frequency supported by clock tree for registered logic

-

I/O delay smaller than 15 ns (in Buffer Mode)

-

Programmable 3-color LED

-

Libraries (C and LabView) and Software tools for Windows and Linux

V2495

-

User customisable FPGA Unit

-

LVDS/ECL/PECL inputs (differential)

-

64 inputs, expandable to 162 (with 32 outputs)

-

32 outputs, expandable to 130 (with 64 inputs)

-

32 independent programmable Gate and Delay Generators

-

3 expansion slots for piggyback board

-

Mini-USB 2.0 Connection

-

Available in Desktop version DT5495

V977

-

NIM and TTL inputs/outputs

-

Individual channel enabling/disabling

-

Software Input/Output generation

-

Fully programmable RORA Interrupter

-

Pushbutton TEST signal

-

Status A capabilities

-

Live insertion