-

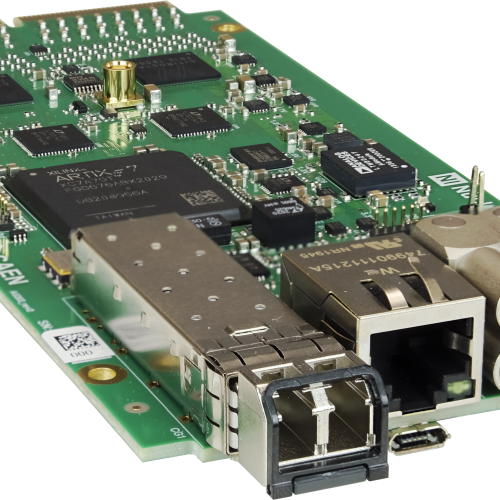

64-ch frontend unit for SiPM readout applications housing two Weeroc Citiroc-1A ASICs

-

Part of FERS-5200, the CAEN platform for the readout of large arrays of detectors (SiPM, MA-PMTs, Gas Tubes, Si detectors, …)

-

Onboard A7585D SiPM power supply for sensors biasing

-

Acquisition modes: Spectroscopy (PHA), Counting, Timing with ToT

-

Scalability and easy-synch: up to 128 cards (8192 channels) can be managed and synchronized by a single DT5215 Concentrator Board, thanks to the optical TDlink

-

Janus 5202 open source software available for board and DAQ control

-

Flexibility: a full range of adapters and cables for different kind of SiPMs and sensors remotization

-

Boxed FERS unit (DT5202) for desktop use or bare (A5202) for customizable mechanical frame

Read Out Systems

FERS-5200 Concentrators

FERS-5200 is a Front-End Readout System designed for large detector arrays, such as SiPMs, multi-anode PMTs, Silicon Strip detectors, Wire Chambers, GEM, Gas Tubes and others. FERS is a highly-scalable distributed platform. Each unit is a small card which houses 32 or 64 channels and includes Front End electronics, A/D converters, trigger logic, synchronization, local memory and readout interface.

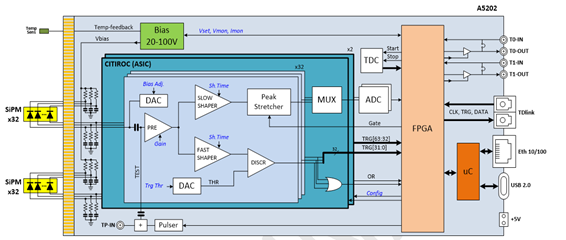

FERS was designed with flexibility in mind: a single user-interface and readout infrastructure has been designed to support and perform a wide range of front-end tasks suitable for a large variety of detector types. In most cases, the front-end is based on ASIC chips. This design is perfect for large detector arrays, combining high density, cost-effective integration of multi-channel readout electronics with a small footprint and low power draw. The Front End ASIC can implement an analog chain made of preamplifier, shaper, peak sensing and discriminator: this is the case of the model A5202, based on the Citiroc-1A chip produced by Weeroc for SiPM readout. In other cases, the ASIC is a fast flash ADC (1 GS/s or more) that records the waveform of the input pulses and makes it possible to apply digital algorithms providing timing, energy and pulse shape information.

- Platform for the readout of large arrays of detectors (SiPM, MA-PMTs, Gas Tubes, Si detectors, …)

- Based on a complete family of Front-End cards (FERS units) + Concentrator Board

- Scalability: from a single standalone FERS unit for prototyping to many thousands of channels, with simple tree network structure.

- Modularity: multiple FERS units (up to 128) can be managed via a single Concentrator board DT5215

- Flexibility: FERS units can be tailored to specific detectors and applications

- Compact size: high-channel density FERS units are very efficient in terms of detector connectivity and footprint.

- DT5202 64-ch Desktop Front-End unit for SiPM readout with Weeroc CITIROC chip

- Naked FERS unit A5202 for integration into mechanical frames available

- Concentrator + A5202/DT5202 = up 8192 channel SiPM array readout

- Data Management: Concentrator Board DT5215 manages event building, processing and formatting.

- Easy-Sync: a single optical link (TDlink) for data readout, slow control and boards synchronization.

- Acquisition modes: spectroscopy (PHA), counting, time stamping, waveform recording, depending on the Front-End ASIC.

FERS-5200 Concentrators Models

A5202

A5203

-

64/128-ch TDC unit for high-resolution timing applications housing the CERN picoTDC

-

Part of FERS-5200, the CAEN platform for the readout of large arrays of detectors (SiPM, MA-PMTs, Gas Tubes, Si detectors, …)

-

Timing resolution: LSB = 3.125 ps, RMS typ. ∼ 7 ps

-

TDC dynamic range: up to 26 bit (∼ 210 μs). Extendable to 56 bit in the FPGA

-

Inputs: differential LVDS signals (max common mode = 1.2 V; max absolute voltage = 1.45 V). NIM, TTL or analog signals through dedicated adapters.

-

Acquisition of leading/trailing edge Time of Arrival (ToA), or leading edge ToA plus Time over Threshold (ToT) of the input signals

-

Scalability and easy-synch: up to 128 cards (8192/16384 channels) can be managed and synchronized by a single DT5215 Concentrator Board, thanks to the optical TDlink

-

Janus 5203 open source software available for board configuration and DAQ control

-

Flexibility: a full range of accessories for different kind of applications

-

Boxed FERS unit (DT5203) for desktop use available – 64 channels only

DT5202

-

64-ch frontend unit for SiPM readout housing two Weeroc Citiroc-1A ASICs

-

Part of FERS-5200, the CAEN platform for the readout of large arrays of detectors (SiPM, MA-PMTs, Gas Tubes, Si detectors, …)

-

Onboard A7585D SiPM power supply

-

Acquisition modes: Spectroscopy (PHA), Counting, Timing with ToT

-

Scalability and easy-sync: from a single standalone FERS unit for prototyping to many thousands of channels, with simple tree network structure. Up to 128 DT5202 units can be managed by a single DT5215 Concentrator Board, i.e. up to 8192 SiPM pixels

-

Flexibility: a full range of accessories for sensors remotization

-

Modularity: multiple FERS units can be distributed on large detector volume and managed by a DT5215 Concentrator board

-

Compactness: front-end cards with high channel density ASICs and effective connection to the detector backplane

-

Janus 5202 open source software available for board and DAQ control

-

Boxed FERS unit (DT5202) for desktop use or naked (A5202) for customizable mechanical frames

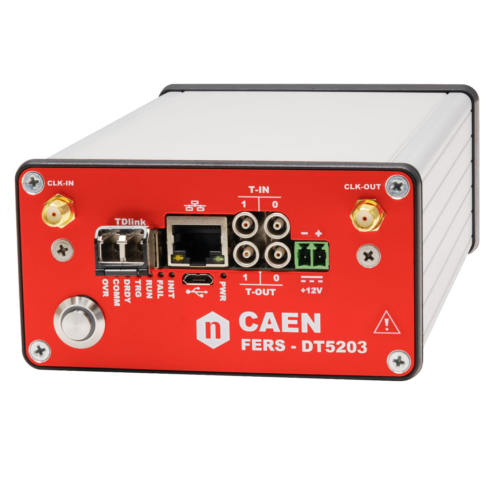

DT5203

-

64-ch TDC unit for high-resolution timing applications housing the CERN picoTDC

-

Part of FERS-5200, the CAEN platform for the readout of large arrays of detectors (SiPM, MA-PMTs, Gas Tubes, Si detectors, …)

-

Timing resolution: LSB = 3.125 ps, RMS typ. ∼ 7 ps

-

TDC dynamic range: up to 26 bit (∼ 210 μs). Extendable to 56 bit in the FPGA

-

Inputs: differential LVDS signals (max common mode = 1.2 V; max absolute voltage = 1.45 V). NIM, TTL or analog signals through dedicated adapters

-

Acquisition of leading/trailing edge Time of Arrival (ToA), or leading edge ToA plus Time over Threshold (ToT) of the input signals

-

Scalability and easy-synch: up to 128 cards (8192 channels) can be managed and synchronized by a single DT5215 Concentrator Board, thanks to the optical TDLink

-

Janus 5203 open source software available for board and DAQ control

-

Flexibility: a full range of adapters and cables for different kind of applications and sensors remotization

-

Naked unit available (A5203) for customizable mechanical frames

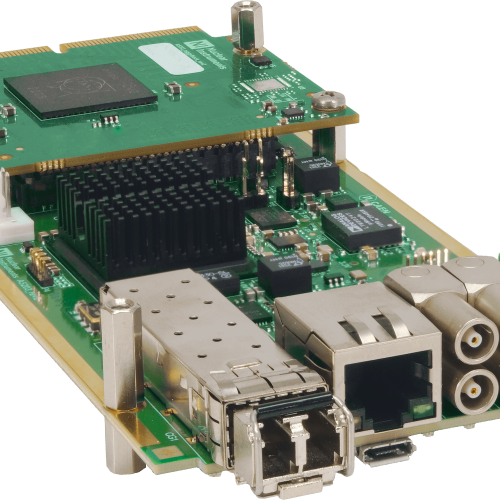

DT5215

-

Concentrator board for multiboard management in FERS-5200, the CAEN platform for the readout of large arrays of detectors (SiPM, MA-PMTs, Gas Tubes, Si detectors, …).

-

Scalability: from a single standalone FERS unit for prototyping to many thousands of channels, with simple tree network structure.

-

Modularity: multiple FERS units can be distributed on large detector volume and managed by a single Concentrator board.

-

8x TDlink for event data building, processing and formatting.

-

Easy-synch: one single optical link (TDlink) for data readout, slow control and boards synchronization.

-

Available also in single TDlink version (DT5216): supports up to 8 FERS units in daisy chain.

A5202 - DT5202

For prototyping and R&D, all that is required is a single A5202 – standalone FERS Unit connected to a computer via USB 2.0 or Ethernet 10/100T (boxed version DT5202 for desktop use also available). This offers a low cost, easy-to-use option to evaluate the system and the ASIC chip housed in the FERS unit. When the solution is validated, it becomes extremely quick and easy to scale up by way of connecting multiple FERS unit to a Concentrator board via optical TDlink. TDlink is the critical physical connection that guarantees high throughput data readout, accurate timing synchronization, and slow control.

DT5215

One DT5215 (FERS Data Concentrator) can manage up to 8 TDlinks. Each TDLink can connect and manage up to 16 FERS units in daisy chain. In the case of the A5202 (CITIROC 1A), it makes 8192 channels read out by a single Concentrator. Multiple concentrator boards can be synchronized to further extend the total number of channels. The Data Concentrator is connected to the Host computer through 1/10 Gb Ethernet or USB 3.0.

A Linux-based Single Board Computer is embedded in the Concentrator board. It manages the data readout from the network of FERS units and the event data building according to the time stamp and/or trigger ID of the event fragments acquired by each unit. Sorted and merged data packets are then stored to the local memory and finally sent to the host computers through a fast 10 GbE or USB 3.0 link. Custom algorithms for data processing and reduction can be easily uploaded by the user onto the embedded CPU.

One computer, one Concentrator, thousands of channels

FERS-5200 is an extendable system: the same FERS unit can be used as stand-alone system for prototyping and validation, and then added to a greater network tree for the readout of large arrays. This strategy eliminates waste and maximizes cost efficiency.

The core of the scalability of the FERS-5200 is the optical TDlink, which manages simultaneously data stream, unit synchronization and slow control.

The concentrator board DT5215 hosts 8 optical links, each capable of sustaining up to 16 FERS units in daisy chain. In the case of A5202 for SiPM readout, this means 8192 channels managed by a single Concentrator board… and multiple Concentrator board can be synchronized to support a limitless number of channels!

HW Functional Description (FPGA)

DT5215

One DT5215 (FERS Data Concentrator) can manage up to 8 TDlinks. Each TDLink can connect and manage up to 16 FERS units in daisy chain. In the case of the A5202 (CITIROC 1A), it makes 8192 channels read out by a single Concentrator. Multiple concentrator boards can be synchronized to further extend the total number of channels. The Data Concentrator is connected to the Host computer through 1/10 Gb Ethernet or USB 3.0.

A Linux-based Single Board Computer is embedded in the Concentrator board. It manages the data readout from the network of FERS units and the event data building according to the time stamp and/or trigger ID of the event fragments acquired by each unit. Sorted and merged data packets are then stored to the local memory and finally sent to the host computers through a fast 10 GbE or USB 3.0 link. Custom algorithms for data processing and reduction can be easily uploaded by the user onto the embedded CPU.

DT5202: 64 channel SiPM readout

- A5202/DT5202 with CITIROC ASIC

- Measurements with SiPMs

- Goes standalone on your desk via Ethernet/USB connection

- Ideal for prototyping phase