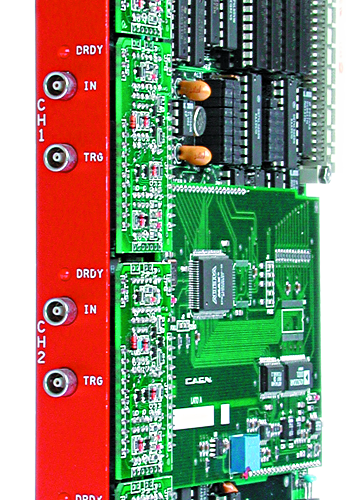

- 4 V full scale range

- 12 bit resolution

- 10 µs/8 ch. conversion time

- Integral non-linearity: ±2 counts

- Differential non linearity ±1 %

- Gate width programmable from 1 to 15 µs

- Zero suppression

Analog

ADCs (Peak Sensing)

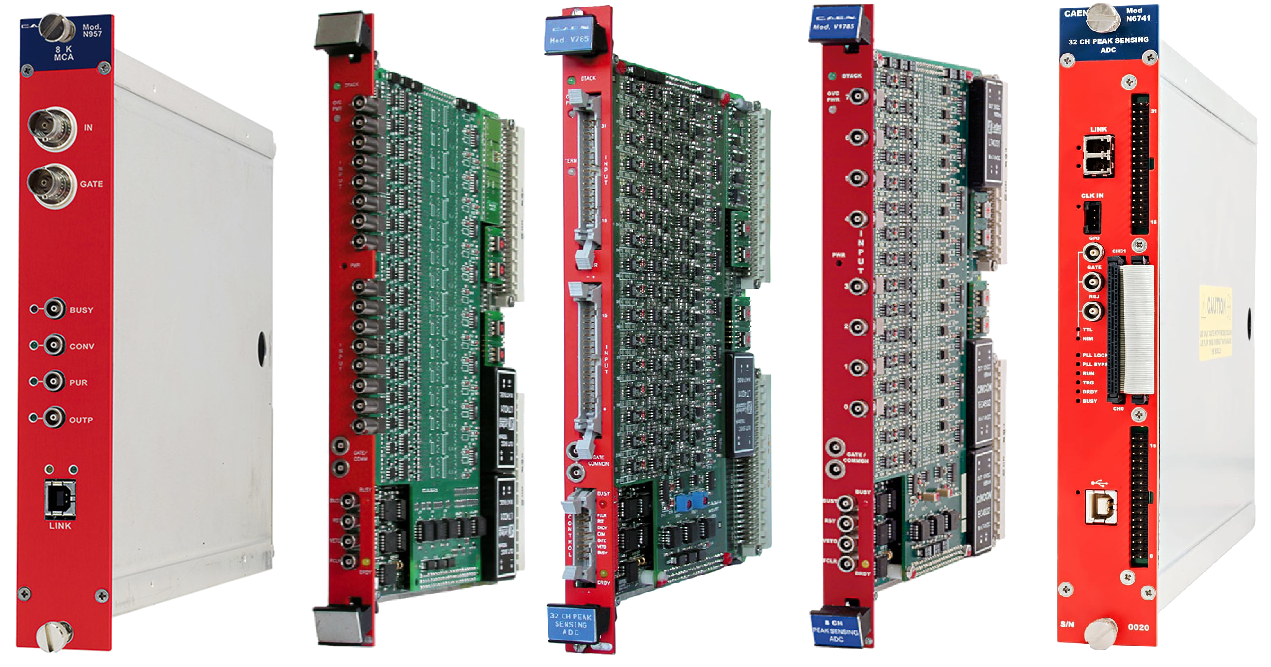

ADCs (Peak Sensing) Models

C420

N6741

-

1-unit wide NIM Module

-

1k, 2k, 4k 8k, 16k Peak Sensing ADC

-

32 input channels, single-ended, with 68-pin ERNI SMC connector (Zin: 2.5 kΩ)

-

Accepts positive and negative inputs

-

4 Vpp or 8 Vpp Full Scale Range software selectable (3.75 Vpp and 7.5 Vpp when sliding scale is enabled)

-

-

Common Gate mode (32 channels converted at once) with linear gate width or programmable by software

-

Low dead time (about 50 ns after the previous gate closes)

-

Sliding scale algorithm for DNL reduction

-

Zero suppression with programmable threshold

-

Multi-Event Buffer (1024 events)

-

USB2.0 and Optical link (CAEN CONET proprietary protocol) communication interfaces

-

Windows and Linux drivers, C and LabVIEW libraries, demo software

-

Firmware upgradable by the user

N957

-

1 input Multichannel Analyzer

-

Fully computer controlled MCA

-

8K ADC, fast conversion time with linearization enhancement circuit

-

PHA acquisition mode

-

Suitable for HPGe, Nai(Tl), CdTe and other detector technologies

-

USB 2.0 communication interface

-

Libraries, Demos (C and LabView) and Software tools for Windows and Linux

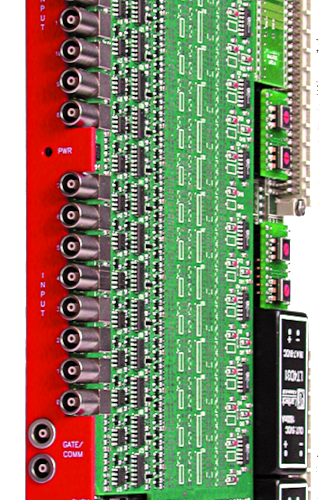

V1741

-

1-unit wide 6U VME64 module

-

1k, 2k, 4k 8k, 16k Peak Sensing ADC

-

64 input channels, single-ended, with 68-pin Dual Row ERNI SMC connector (Zin: 2.5 kΩ)

-

Accepts positive and negative inputs

-

4 Vpp or 8 Vpp Full Scale Range software selectable (3.75 Vpp and 7.5 Vpp when sliding scale is enabled)

-

-

Common Gate mode (64 channels converted at once) with linear gate width or programmable by software

-

Low dead time (about 50 ns after the previous gate closes)

-

Sliding scale algorithm for DNL reduction

-

Zero suppression with programmable threshold

-

Multi-Event Buffer (1024 events)

-

VME64 and Optical link (CAEN CONET proprietary protocol) communication interfaces

-

Windows and Linux drivers, C libraries, demo software

-

Firmware upgradable by the user

V1785

-

Two simultaneous ranges: 0 ÷ 4 V / 0 ÷ 500 mV

-

12 bit resolution with 15 bit dynamics

-

125 µV LSB on low range, 1mV LSB on high range

-

2.8 µs / 8 ch conversion time

-

600 ns fast clear time

-

Zero and overflow suppression for each channel

-

±0.1 % Integral non linearity

-

±1.5 % Differential non linearity

-

32 event buffer memory

-

BLT32/MBLT64/CBLT32/CBLT64 data transfer

-

Multicast commands

-

Live insertion

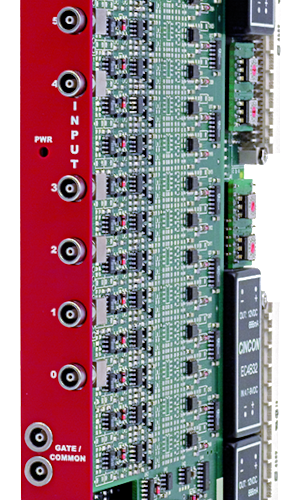

V419

- 0 ÷ 4 V input range

- Full 12 bit resolution

- 1 mV LSB

- 1.2 µs / ch. conversion time

- ±0.5 counts integral non linearity

- ±1% differential non linearity

- Gate width (Rise Time Protection) programmable from 2 to 32 µs

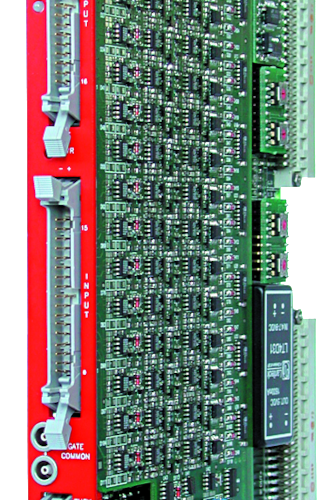

V785

-

High channel density

-

12-bit resolution

-

5.7 µs / 32 ch conversion time

-

600 ns fast clear time

-

Zero and overflow suppression for each channel

-

±1.5% differential non linearity

-

±0.1% integral non linearity

-

32 event buffer memory

-

BLT32/MBLT64/CBLT32/CBLT64 data transfer

-

Multicast commands

-

Live insertion

-

Libraries, Demos (C and LabView) and Software tools for Windows and Linux

V785N

-

High channel density

-

12 bit resolution

-

2.8 µs / 16 ch conversion time

-

600 ns fast clear time

-

Zero and overflow suppression for each channel

-

±1.5% differential non linearity

-

±0.1% integral non linearity

-

32 event buffer memory

-

BLT32/MBLT64/CBLT32/CBLT64 data transfer

-

Multicast commands

-

Live insertion

-

Libraries, Demos (C and LabView) and Software tools for Windows and Linux